簡介

本文從電氣工程師的觀點(diǎn) (POV) 出發(fā),重點(diǎn)研究了給定處理器的實(shí)施和如何在各種實(shí)施方式下進(jìn)行權(quán)衡。軟件工程師關(guān)于程序執(zhí)行中的多線程、并行處理或者再配置的觀點(diǎn)不在本文的考慮范圍之列。程序執(zhí)行的主要方面包括速度、精度、面市時(shí)間 (TM) 和存儲(chǔ)器利用等。另外,編碼標(biāo)準(zhǔn)、IP 維護(hù)、便攜性和文檔等其他因素僅影響將來項(xiàng)目的 TM,對(duì)目前的程序沒有影響。因此,在本文的案例研究中只考慮主要的方面。在理想的情況下,我們希望能夠把程序執(zhí)行的每個(gè)方面都是最優(yōu)秀的,但實(shí)際的系統(tǒng)并非完美,需要有所取舍。本文將探討在程序?qū)嵤┲袡?quán)衡使用公式法和 LUT 的情況,并探討各方面下表現(xiàn)最佳的方法。實(shí)施方法的選擇將取決于應(yīng)用的具體要求。

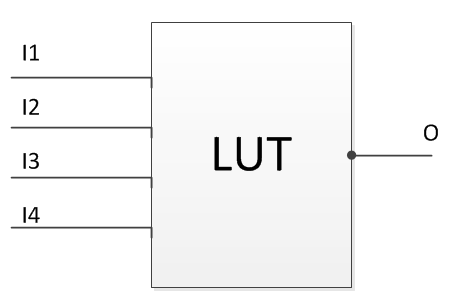

LUT 是存儲(chǔ)在系統(tǒng)存儲(chǔ)器中的預(yù)期結(jié)果范圍列表或者陣列。使用測得的輸入值作為索引,就可以在執(zhí)行中得到輸出值,從而節(jié)約處理時(shí)間。LUT 可以通過多種方式建立。大多數(shù)工程師除了需要具備工程領(lǐng)域內(nèi)的各項(xiàng)技術(shù)技能,也同時(shí)還需要具備“Excel 工程設(shè)計(jì)”技能,因此,本文將采用 Microsoft Excel 表格創(chuàng)建 LUT。將預(yù)期的輸入范圍輸入公式,即可在 LUT在得到對(duì)應(yīng)的輸出值。與執(zhí)行傳統(tǒng)的數(shù)學(xué)公式相比,使用 LUT 系統(tǒng)具有多種優(yōu)勢(shì)。

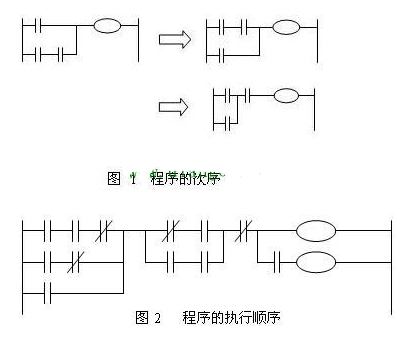

執(zhí)行速度

Accuracy

在完整的系統(tǒng)中,輸入和預(yù)期輸出之間的延遲來自硬件、軟件、中斷和邏輯驅(qū)動(dòng)延遲。數(shù)據(jù)處理和分析也會(huì)影響程序中的軟件延遲。數(shù)據(jù)處理取決于實(shí)施指令所需要的時(shí)鐘周期數(shù)量。簡單來說,與 LUT 方法訪問存儲(chǔ)器中的值相比,公式法使用的乘、除或者其他復(fù)雜的數(shù)學(xué)函數(shù)耗用的 CPU 周期更多。盡管可以采用移位法和加減法算法來完成乘除運(yùn)算,提高公式法的速度,但在大多數(shù)情況下對(duì)簡化等式及提升效率和精度的作用微乎其微。因此,LUT 法一般都會(huì)快于公式法。

精度

在精度方面,公式法一直優(yōu)于 LUT 法。由于我們采用的是電氣工程師的視角,我們不妨在執(zhí)行方法和電氣信號(hào)之間進(jìn)行一下類比。公式法類似于連續(xù)時(shí)間模擬信號(hào),而 LUT 則類似于量化的離散信號(hào)。無限樣本的 LUT 可以達(dá)到公式法的精度。LUT 的精度取決于考慮的范圍和范圍中的樣本數(shù)量。因此,根據(jù)要求的精度和范圍,LUT 的存儲(chǔ)器利用是可擴(kuò)展的。

存儲(chǔ)器利用

公式法中的存儲(chǔ)器使用主要取決于用于等式執(zhí)行的代碼空間大小和支持這些等式的數(shù)學(xué)庫的大小。如果采用單浮點(diǎn)函數(shù)則需要添加整個(gè)庫,存儲(chǔ)器耗用會(huì)顯著增長。在 LUT 法下,存儲(chǔ)器耗用取決于用來解析 LUT 獲得輸出值的代碼大小和LUT 的大小。一般而言,實(shí)施公式和解析 LUT 的代碼空間差別不大,但庫對(duì)存儲(chǔ)器的占用顯著高于 LUT 的大小。LUT 的大小是由要求的精度決定的,并可通過插值法進(jìn)行優(yōu)化。因此,在應(yīng)用要求的公式比較復(fù)雜,輸入范圍又較小的情況下,LUT 對(duì)存儲(chǔ)器的利用效率更高。

面市時(shí)間

由于早已開發(fā)完畢,并在大多數(shù)系統(tǒng)上得到過驗(yàn)證,因而在直接采用公式的情況下,面市時(shí)間會(huì)更快。這樣既能達(dá)到要求的精度,又能節(jié)省設(shè)計(jì)、調(diào)試和測試系統(tǒng)的時(shí)間。在某些項(xiàng)目中,存儲(chǔ)器可能不足以滿足公式法使用的數(shù)學(xué)庫的要求。在這種情況下,則需要采用分段線性或 LUT 法。LUT 法的 TM 取決于多種因素,如應(yīng)用復(fù)雜性、工程師技能、可用于構(gòu)建 LUT 的軟件工具等。因此,這項(xiàng)參數(shù)無法以量化的方式進(jìn)行比較。不過,由于與具體的系統(tǒng)/平臺(tái)無關(guān),公式法的實(shí)施速度可能會(huì)快一些。

本文就應(yīng)在什么地方使用 LUT 取代公式的兩個(gè)示例及其涉及的權(quán)衡進(jìn)行了探討。所探討的案例中包含程序執(zhí)行的不同重點(diǎn)方面。第一個(gè)例子是含有復(fù)雜的數(shù)學(xué)等式的溫度感應(yīng)應(yīng)用。因?yàn)椴捎霉椒▉慝@得溫度值耗用了大量的存儲(chǔ)器,留給根據(jù)測得的溫度值增添其他功能的存儲(chǔ)空間則變得更少了。通常,溫度感應(yīng)是完整的感應(yīng)器系統(tǒng)的一部分,因此存儲(chǔ)器優(yōu)化在該應(yīng)用中非常重要。第二個(gè)例子是控制系統(tǒng)算法。在該例中,為避免系統(tǒng)不穩(wěn)定情況的出現(xiàn),執(zhí)行速度是最需要考慮的。

案例研究1:溫度測量

因其阻值隨溫度而發(fā)生變化,熱敏電阻通常被用來測量溫度。采用負(fù)溫度系數(shù)(NTC) 的熱敏電阻測得的溫度 (Tk) 與測得的阻抗 (RT) 呈反比關(guān)系,可表達(dá)為等式1 中的?Steinhart-Hart?公式。

[1]

等式中的 A、B、C 均為常數(shù)。為測得阻抗變化,可考慮圖 1 所示的系統(tǒng)。在此圖中,VT?為熱敏電阻兩端的電壓,Vref?為恒定參考電壓。ADC 的輸出是 VT?點(diǎn)模擬電壓的數(shù)字形式。固件根據(jù) ADC 測得的值,采用各種實(shí)施方案計(jì)算出相應(yīng)的溫度值。

.

圖?1:采用熱敏電阻的溫度感應(yīng)系統(tǒng)方框圖

圖中文字:thermistor:熱敏電阻

????????????????? firmware data processing:固件數(shù)據(jù)處理

????????????????? temperature value?溫度值

公式法:

在公式法中,熱敏電阻的阻值使用標(biāo)準(zhǔn)的分壓方程式計(jì)算,如等式 2 所示。

[2]

這里的 VGND?和 Vref?可在程序中定義為常數(shù),也可測量得出。將測量得出的值代入等式 2,可以消除因參考電壓變化、ADC 增益和偏置變化引起的誤差。在本文中,假定參考電壓、ADC 是理想的,且Vref?和 VGND均為常數(shù)。在計(jì)算出阻值后,就可以使用等式 1 計(jì)算出溫度值。

因?yàn)榈仁?1 不是簡單線性等式,在采用公式法的情況下,有效的存儲(chǔ)器利用和執(zhí)行的速度都很重要。這個(gè)等式必須加入較大的數(shù)學(xué)庫。是否因?yàn)榫榷邮茌^大的存儲(chǔ)器占用和較慢的反應(yīng)速度,取決于應(yīng)用的需要。在醫(yī)療或太空設(shè)備中,精度非常重要,而在家用電器中,精度并不是最重要的因素,比如我們?cè)诎脖O到y(tǒng)、爐具或者轎車中所見到的溫度測量。在這些應(yīng)用中,如果外部溫度是 70 度,而感應(yīng)系統(tǒng)顯示 71 度,并不會(huì)導(dǎo)致致命的結(jié)果。消費(fèi)者也不愿意化更多的錢購買功能更強(qiáng)大的芯片來獲得這種精度。

針對(duì)熱敏電阻的 LUT

熱敏電阻的電壓會(huì)一直對(duì)應(yīng)一個(gè)唯一的阻值,也就是唯一的溫度值。例如,如果 NTC 熱敏電阻在 25 攝氏度的阻值為?RT=10 KΩ,參考電阻為?Rref=10 KΩ 時(shí),則意味著 25 攝氏度時(shí)的電壓?VT=Vref/2。在溫度為 50 攝氏度時(shí),RT=5 KΩ,不過?Rref?和?Vref?保持不變,故VT=Vref/3。因此,VT=Vref/3 就意味著?T=50 °C,而VT=Vref/2 意味著?T=25 °C。這樣就可以根據(jù)測得電壓對(duì)應(yīng)的溫度值使用等式編制一張表格,存儲(chǔ)在存儲(chǔ)器中作為 LUT。然后使用測得的電壓值作為索引來解析LUT,進(jìn)而獲得對(duì)應(yīng)的溫度值。決定溫度步長的LUT 的大小會(huì)影響測量的精度。如果要求的溫度范圍為?–40 ~ 125 °C,則在步長為?1 °C?的情況下需要有 166 條目的 LUT,如果是?0.5 °C,就需要 332 條目的 LUT。因此在精度、測量范圍和存儲(chǔ)器使用方面存在大量的權(quán)衡空間。在公式法下,不管要求的精度和測量范圍如何,存儲(chǔ)器使用都是固定的。

比較

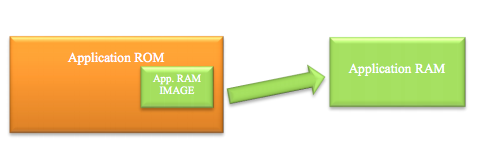

包含 LUT 法和公式法的項(xiàng)目都在賽普拉斯軟件 PSoC Designer 中借助 CY8C27x43 芯片得到了實(shí)施。LUT 的大小如前所述,為 166 條樣本。LUT 法使用的 ROM 為1,000 字節(jié),而在公式法中為 3,780 字節(jié)。如果項(xiàng)目在帶有 4K 存儲(chǔ)器的芯片上實(shí)施,則剩下的閃存對(duì)任何復(fù)雜系統(tǒng)均不敷使用。

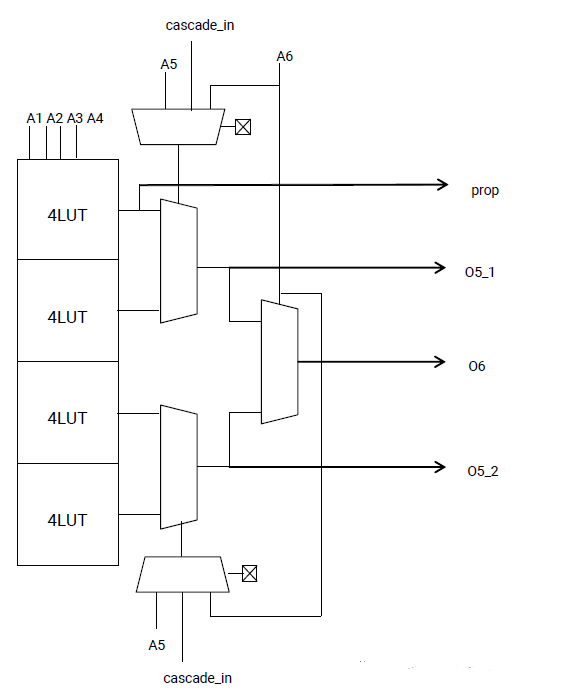

為比較執(zhí)行速度,分別運(yùn)行了兩種方法。如圖 2 所示,每種方法運(yùn)行完畢后,都會(huì)觸發(fā)一個(gè)引腳。

圖?2:熱敏電阻感應(yīng)系統(tǒng)的執(zhí)行時(shí)間

對(duì)應(yīng)執(zhí)行公式法耗用時(shí)間的信號(hào)電平較低,對(duì)應(yīng)執(zhí)行 LUT 法耗用時(shí)間的信號(hào)電平較高。如圖所示,LUT 法耗用的時(shí)間為 8μs,公式法耗用的時(shí)間為?468 μs。雖然速度方面的比較取決于處理器時(shí)鐘速率和用于實(shí)施的 CPU 時(shí)鐘周期,但本案例大致說明了兩者之間的差異。顯而易見,在本應(yīng)用中,LUT 法可以將執(zhí)行時(shí)間降低 50 倍。

案例研究2:PID 系統(tǒng)

比例-積分-微分 (PID) 系統(tǒng)是最常見的反饋控制系統(tǒng)(如穩(wěn)壓器等)。采用專門的硬件,可以獲得最快的控制環(huán)路響應(yīng)時(shí)間。不過,如果采用微處理器來實(shí)施 PID 系統(tǒng),可以支持更多調(diào)試和調(diào)整 (adaptation) 功能。本案例研究的兩種實(shí)施方法均采用 SoC。圖 3 所示的是 PID 系統(tǒng)的實(shí)施方框圖。

圖?3:PID?系統(tǒng)方框圖

圖中文字:plant:設(shè)備

????????????????? error:誤差

????????????????? firmware data processing:固件數(shù)據(jù)處理

????????????????? output:輸出

PID 穩(wěn)壓器系統(tǒng)具有需要的置位點(diǎn)?Vset?和實(shí)際輸出電壓?Vout。需要的信號(hào)和輸出信號(hào)之間的差就是誤差值e。控制環(huán)路然后運(yùn)用等式 3 所示的閉合環(huán)路系統(tǒng)等式來讓誤差值為 0:[3]這里的?Kp、Ki和Kd?均為常數(shù)。

公式法

在 PID 系統(tǒng)的軟件實(shí)施方案中,積分/差分是通過對(duì)上一誤差值和新的誤差值進(jìn)行累加/累減來實(shí)現(xiàn)的。這些值然后與等式 4 所示的相應(yīng)常數(shù)相乘。

[4]

這里的?ErrorI?是添加到現(xiàn)有誤差值中的上一累加誤差值,ErrorD?是從現(xiàn)有誤差值中減去的上一累減誤差值。得出的新值存儲(chǔ)為上一誤差值并用于下一個(gè)執(zhí)行周期。由于等式中有乘法運(yùn)算,因此執(zhí)行速度較慢。

LUT 法

在 LUT 法中,程序不使用乘法,其使用的是存儲(chǔ)在表中的預(yù)先生成的誤差值與常數(shù)相乘的積。測得的誤差值被用作在對(duì)應(yīng)的表中獲得輸出的索引。因此,誤差值僅限于整數(shù)值而非浮點(diǎn)數(shù),因此也就限制了精度。采用這種方法的指令如等式 5 所示:

[5]

這里?TableP、TableI和?TableD分別為包含?KP*Error、Ki*ErrorI和?Kd*ErrorD值的 LUT。

比較

PID 系統(tǒng)的實(shí)施是采用賽普拉斯軟件 PSoC Designer 在 CY8C27x43 芯片中進(jìn)行的。為實(shí)施 LUT 法,使用了各存有 60 個(gè)值的三張表,使用的 ROM 為 1,150 字節(jié)。對(duì)同一應(yīng)用,公式法需使用 1,800 字節(jié)的 RAM。兩種方法的執(zhí)行時(shí)間如圖 4 所示。

圖?4:PID?系統(tǒng)的執(zhí)行時(shí)間

上圖波形與圖 2 相似,高電平信號(hào)對(duì)應(yīng)的是 LUT 法的執(zhí)行速度,低電平信號(hào)對(duì)應(yīng)的是公式法的執(zhí)行速度。顯而易見,執(zhí)行速度提升了 4 倍。

結(jié)論:

本次探討及案例研究顯示,LUT 法確實(shí)能夠加快程序執(zhí)行的速度。對(duì)于具體的應(yīng)用,程序執(zhí)行中還有其他需要在選擇實(shí)施方法之前加以權(quán)衡的問題。最終選擇哪種方法則取決于應(yīng)用的規(guī)范。不過,如果旨在加快執(zhí)行速度并減少存儲(chǔ)器占用,則化費(fèi)時(shí)間構(gòu)建 LUT 也是在所不惜的。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論