1.引言

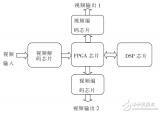

本文針對紅外圖像處理系統(tǒng)的實時性要求,提出了基于DSP+FPGA+ASIC的圖像處理架構(gòu)。

隨著紅外焦

2010-07-22 15:18:50 796

796 本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進行視頻處理的方案,實現(xiàn)視頻采集、處理到傳輸?shù)恼麄€過程。

2014-10-23 15:35:49 6040

6040

DSP+FPGA架構(gòu)的最大特點是結(jié)構(gòu)靈活、有較強的通用性、適合于模塊化設(shè)計,從而能夠提高算法效率,同時其開發(fā)周期短、系統(tǒng)易于維護和升級,適合于實時視頻圖像處理。

2015-02-03 15:20:47 1166

1166

設(shè)計了一種基于FPGA的實時視頻圖像采集處理電路系統(tǒng)。采用FPGA作為整個系統(tǒng)的控制和圖像數(shù)據(jù)處理中心。DDR2 SDRAM為高速儲存模塊核心器件,CMOS 7670為視頻圖像采集器件。

2018-02-10 02:43:55 19311

19311

各種關(guān)于FPGA 視頻 圖像處理的論文....希望更多人加入到這個方向上來,

2017-08-17 09:13:47

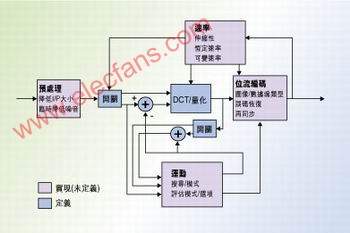

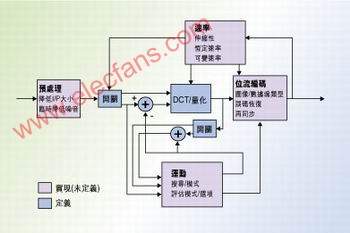

使用FPGA進行圖像和視頻處理的原理、結(jié)構(gòu)、方法和流程,實現(xiàn)視頻處理中的重要模塊設(shè)計;同時,針對不同的設(shè)計目標進行優(yōu)化,另外采用新型的EDA工具進行設(shè)計、仿真和驗證,掌握最前沿的設(shè)計方法。 FPGA圖像

2009-07-16 14:05:25

想學習FPGA視頻圖像處理,不知道該如何著手,有沒大神指導迷津,或者有什么這方面的書籍推薦的!

2015-07-28 21:35:31

架構(gòu)、嵌入式系統(tǒng)、實時操作系統(tǒng)、數(shù)字信號處理、圖像與視頻處理和數(shù)字通信等,可以實現(xiàn)片上課程理念。七、教學大綱基于Xilinx FPGA的DSP系統(tǒng)設(shè)計與實現(xiàn)的課程安排如下: 第一天 課程目標

2009-07-21 09:22:42

來說,濾除噪聲、擴展對比度、銳化以及色彩增強等處理能顯著提升視覺效果。這里設(shè)計一個基于FPGA的實時視頻圖像處理系統(tǒng),包含增強對比度擴展和色飽和度兩種處理方法,相比于DSP和ASIC方案來說,FPGA在性能和靈活性方面具有絕對優(yōu)勢,應(yīng)用FPGA設(shè)計視頻通信系統(tǒng)更普遍。

2019-08-22 08:22:29

VerilogHDL來描述并直接用硬件實現(xiàn)。即使一些模塊是預制的IP模塊,這個任務(wù)仍然是集成這些模塊到一個完整的設(shè)計之中。Helion是一家致力于利用FPGA和DSP從事圖像信號處理領(lǐng)域開發(fā)的公司。他們

2012-08-11 11:27:45

格式不變,因此在將數(shù)據(jù)保存到 SRAM 以前,需要將奇數(shù)場和偶數(shù)場的數(shù)據(jù)還原成一幅完整的圖像。如果傳輸格式是 YUV,需要轉(zhuǎn)化為便于 DSP 處理的 RGB 格式。FPGA 需要完成如下任務(wù):(1)將

2018-12-11 09:47:09

圖像處理用FPGA好一點還是用DSP好一點?

2021-10-22 06:35:01

我在做fpga與dsp的SRIO通信,我用的是論壇上提供的SRIO test程序,目前dsp端能夠實現(xiàn)端口0的外部回環(huán)測試。fpga端的協(xié)議還沒做通,我想用dsp直接給fpga發(fā)包,fpga根據(jù)收到

2018-06-21 10:45:13

用無線攝像頭把攝到的即時視頻通過無線發(fā)送,發(fā)到單片機,再用液晶顯示即時圖像,求思路。(不準備用WIFI)諸位大神求思路!

2013-09-25 21:31:58

架構(gòu)、嵌入式系統(tǒng)、實時操作系統(tǒng)、數(shù)字信號處理、圖像與視頻處理和數(shù)字通信等,可以實現(xiàn)片上課程理念。七、教學大綱基于Xilinx FPGA的DSP系統(tǒng)設(shè)計與實現(xiàn)的課程安排如下:第一天 課程目標

2009-07-21 09:20:11

申請理由:學習DSP 和FPGA DSP優(yōu)越的計算能力 超高的編解碼速度 和FPGA 聯(lián)合使用 取長補短 快速實現(xiàn)視頻傳輸不是夢 。第一次申請。現(xiàn)在進行FPGA 的視頻傳輸部分項目描述:項目描述:先

2015-09-10 11:18:56

申請理由:TMS320C6748是TI公司推出的高速DSP,將其應(yīng)用于微光視頻圖像的實時處理,對于提高系統(tǒng)的實時性和采集具有十分重要的意義,同時也可以講更加復雜的算法加入其中,對于微光視頻圖像處理

2015-10-09 15:12:31

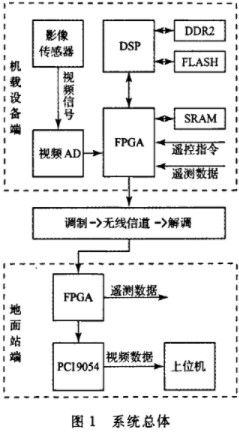

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進行視頻處理的方案,實現(xiàn)視頻采集、處理到傳輸?shù)恼麄€過程。實時視頻圖像處理中,低層的預處理算法處理的數(shù)據(jù)量大,對處理速度要求高,但算法相對比較簡單,適合于用

2019-07-01 07:38:06

針對視頻的輸出顯示要求,重點介紹了基于雙線性插值算法的實現(xiàn)。ModelSim的仿真結(jié)果表明,該算法符合多屏幕顯示系統(tǒng)的要求。關(guān)鍵詞 視頻監(jiān)控;視頻圖像處理;雙線性插值;FPGA;多屏幕

2019-06-28 07:06:54

為解決高速數(shù)字圖像處理系統(tǒng)和實時性相沖突的要求,設(shè)計了以多DSP(數(shù)字信號處理器TMS320C6416)和現(xiàn)場可編程門陣列(FPGA)相結(jié)合的實時圖像處理系統(tǒng)。重點介紹了該系統(tǒng)的硬件資源選擇、基本組

2021-04-28 06:14:48

,數(shù)字信號處理與數(shù)字圖像處理沒有太大區(qū)別),就意味著可以用FPGA做硬件設(shè)計來實現(xiàn)DSP芯片的功能,當然,相比較專業(yè)的DSP芯片 成本太高,因此你也沒必要選擇FPGA+DSP,就選擇DSP芯片,算法...

2021-07-28 09:16:02

本帖最后由 mr.pengyongche 于 2013-4-30 03:15 編輯

隨著計算機和數(shù)字圖像處理技術(shù)的飛速發(fā)展,視頻監(jiān)控技術(shù)應(yīng)用廣泛。傳統(tǒng)的視頻監(jiān)控系統(tǒng)都是用單一攝像頭對某一固定

2012-12-12 17:00:21

的重點是以DSP+FPGA為核心的視頻處理模塊的設(shè)計與實現(xiàn),可以完成多路視頻的切換選擇輸出控制和視頻縮放顯示的功能,同時具備通信控制等功能。

2019-06-20 06:34:25

,FPGA協(xié)同DSP完成時序邏輯控制和組合邏輯控制。處理后的圖像可以通過1394接口輸出。該系統(tǒng)主要由FPGA和DSP實現(xiàn),設(shè)計靈活,具有很強的重構(gòu)性。http://www.tjjbhg.com/soft/3/2011/20110224188688.html

2014-11-05 14:44:51

為了實現(xiàn)—是彈武器瞄準自動化,本文設(shè)計了基于DSP和FPGA的高速高精確度雙通道CCD圖像采集系統(tǒng),采用QUartuBn在AJtera的FPGA器件CYCLONEII上設(shè)計了CCD驅(qū)動時序電路,采用

2014-11-07 14:54:07

電視圖像或紅外兩個波段,實現(xiàn)圖像跟蹤各項功能。本文提出的跟蹤算法與設(shè)計的跟蹤裝置可在一定程度上解決視頻跟蹤精度低、處理速度慢的問題,同時本視頻跟蹤裝置也可作為進一步研究圖像處理與跟蹤控制的平臺。

2019-06-26 06:09:46

基于DSP的圖像處理系統(tǒng)的應(yīng)用研究摘要 本文介紹了一種基于FPGA+DSP結(jié)構(gòu)的具有通用性、可擴充性的高速數(shù)字圖像處理系統(tǒng)硬件平臺。重點介紹了以高速數(shù)字信號處理器TMS320DM642

2012-12-19 11:05:08

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進行視頻處理的方案,實現(xiàn)視頻采集、處理到傳輸?shù)恼麄€過程。 實時視頻圖像處理中,低層的預處理算法處理的數(shù)據(jù)量大,對處理速度要求高,但算法相對比較簡單,適合于

2019-06-28 08:10:26

圖像數(shù)據(jù)處理的工作原理是什么?基于FPGA+DSP的圖像處理系統(tǒng)待如何去設(shè)計?

2021-06-02 06:54:28

數(shù)據(jù)量特別大、運算復雜,單純依靠通用PC很難達到實時性要求,不能滿足現(xiàn)行高速三維圖像處理應(yīng)用。 本系統(tǒng)中,采用FPGA實現(xiàn)底層的信號預處理算法,其處理數(shù)據(jù)量很大,處理速度高,但算法結(jié)構(gòu)相對

2019-06-24 06:11:03

片TI的KeyStone系列多核浮點/定點DSP TMS320C6678作為核心處理單元,來完成視覺圖像處理算法,采用1片Xilinx的Kintex-7系列FPGA XC7K325T作為視頻協(xié)處理單元

2017-12-16 15:51:55

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進行視頻處理的方案,實現(xiàn)視頻采集、處理到傳輸?shù)恼麄€過程。 實時視頻圖像處理中,低層的預處理算法處理的數(shù)據(jù)量大,對處理速度要求高,但算法相對比較簡單,適合于

2019-06-19 06:12:05

基于FPGA和視頻解碼芯片的實時圖像采集系統(tǒng)設(shè)計,介紹了CCD圖像傳感器和ADV7181B解碼芯片的I2C配置原理。給出了乒乓緩存的原理與實現(xiàn)方法,同時給出了ADV7181B與FPGA等芯片組成視頻處理電路的設(shè)計和FPGA的程序實現(xiàn)方法。

2017-11-17 13:59:48

本帖最后由 lee_st 于 2017-10-31 08:26 編輯

基于FPGA的視頻圖像處理系統(tǒng)

2017-10-30 17:26:16

基于FPGA的視頻圖像處理系統(tǒng)

2015-05-27 20:34:49

基于FPGA的視頻圖像處理系統(tǒng)。

2015-05-23 12:18:23

。基于DSP方式在運算速度、數(shù)據(jù)吞吐量等方面有限制。本設(shè)計基于FPGA實現(xiàn),邊緣檢測采用流水線結(jié)構(gòu)。實驗結(jié)果表明,該系統(tǒng)十分適合視頻數(shù)據(jù)的處理。

2019-09-24 06:55:15

視頻采集是進行圖像及圖形處理的第一步,目前視頻采集系統(tǒng)一般由FPGA和DSP組成,FPGA作為視頻采集控制芯片,DSP作為圖像處理與成像控制芯片。隨著FPGA技術(shù)的發(fā)展,片內(nèi)的邏輯單元越來越多,片內(nèi)的DSP資源也越來越豐富,因此可直接在FPGA片內(nèi)進行圖像處理。

2019-08-14 07:17:12

本人想做數(shù)字圖像處理方面的課題,不知道DSP和FPGA的器件怎么選擇,希望有經(jīng)驗的大神給點建議,我做的這個課題是用FPGA和DSP處理圖像 dsp作為主處理器,負責主要的算法,FPGA負責從處理

2012-08-06 10:54:12

怎么實現(xiàn)基于DSP的視頻圖像壓縮系統(tǒng)的設(shè)計?

2021-06-08 06:02:18

老師要我們做一個雙目機器人,我負責障礙物識別這一塊,計劃用DSP做,可是我只有51,微機原理,C和C++這些書本知識,我該怎么學DSP視頻圖像處理呢?學習硬件知識計劃20天,軟件算法30天。大家?guī)蛶兔Γ瑤臀乙?guī)劃一下,我都不知道該如何開始啊!(第一次接觸DSP >_

2015-01-14 13:55:40

這幾年有點背,逐漸遠離主流話題,所以有人就有了這樣的問題:DSP會被FPGA取代嗎?小編總結(jié)了各個網(wǎng)友的回答: 網(wǎng)友一:獨立的DSP不會被FPGA替代,但是會被增強了信號處理功能的ARM處理器替代

2021-07-16 08:12:03

,如果能整出不需要浮點運算的神經(jīng)網(wǎng)絡(luò),那么FPGA在這方面的應(yīng)用將會更大。

前些年用matlab和opencv做圖像處理。近一段時間通過FPGA處理攝像頭視頻數(shù)據(jù),有太多感觸,復雜的算法先不提

2023-06-08 15:55:34

看到ADI的blackfin系列的DSP基本都有40位ALU,不知道這個在做視頻處理時有什么優(yōu)勢?剛開始接觸視頻處理方面,對這個的基礎(chǔ)算法不太清楚,不知這個40位有什么特殊之處?如果用FPGA代替DSP外接40位DDR是否有用?

2018-09-30 11:37:09

在可編程邏輯中實現(xiàn)可配置軟核處理器有哪些好處?怎樣建立起處理器和主機pc之間的通信?怎樣用DSP功能去提高圖像處理?

2021-04-14 06:52:33

誰有基于fpga的視頻圖像處理的資料嗎,分享一下,十分感謝!!!!!!

2016-11-03 18:25:38

采用FPGA 實現(xiàn)視頻和圖像處理設(shè)計

2015-10-26 21:10:06

基于FPGA的小型微光視頻圖像增強處理系統(tǒng)Mini Low-level-light Video Image Enhancement Processing System Based on FPGA

摘要:為微光視頻圖像的實時增強設(shè)計了一套可應(yīng)用于空間狹小環(huán)境中

2009-01-11 12:11:18 34

34 在研究視頻圖像實時處理系統(tǒng)的基礎(chǔ)上, 以TI 公司的DSP 芯片(TMS320C5000)為硬件開發(fā)平臺,以Code Composer Studio 為軟件開發(fā)環(huán)境,通過硬件設(shè)計和軟件編程實現(xiàn)視頻圖像中動態(tài)目標的

2009-07-08 15:11:00 25

25

通過對CMOS 圖像傳感器輸出的黑白電視信號進行視頻采集, 獲得數(shù)字圖像信號, 實現(xiàn)數(shù)字圖像的處理。該系統(tǒng)采用PC 機和基于DSP 的數(shù)字信號處理板(數(shù)字板) 構(gòu)成主從式成像系統(tǒng)。

2009-07-28 14:10:03 22

22 設(shè)計一種基于DSP和FPGA架構(gòu)的通用圖像處理平臺,運用FPGA實現(xiàn)微處理器接口設(shè)計,并對圖像數(shù)據(jù)進行簡單預處理,利用DSP進行復雜圖像處理算法和邏輯控制,實現(xiàn)圖像數(shù)據(jù)的高速傳輸

2010-12-25 17:06:54 60

60 基于DSP+FPGA+ASIC的實時圖像處理系統(tǒng)

1.引言

隨著紅外焦平面陣列技術(shù)的快速發(fā)展,紅外成像系統(tǒng)實現(xiàn)了高幀頻、高分辨率、高可靠性及微型化,在目標跟蹤

2010-01-13 10:39:49 1115

1115

基于DSP和FPGA的通用圖像處理平臺設(shè)計

摘要:設(shè)計一種基于DSP和FPGA架構(gòu)的通用圖像處理平臺,運用FPGA實現(xiàn)微處理器接口設(shè)計,并對圖像數(shù)據(jù)進行簡單預處理,利用DSP

2010-02-01 11:10:21 1379

1379

隨著數(shù)字融合的進一步發(fā)展,系統(tǒng)的設(shè)計和實現(xiàn)需要更大的靈活性,以解決將完全不同的標準和要求整合為同類產(chǎn)品時引發(fā)的諸多問題。本文介紹FPGA在視頻處理中的應(yīng)用,與A

2010-08-19 11:47:53 724

724

捅要:為了實現(xiàn)是彈武器瞄準自動化,本文設(shè)計了基于DSP和FPGA的高速高精確度雙通道CCD圖像采集系統(tǒng),采用QUartuBn在AJtera的FPGA器件CYCLONEII上設(shè)計了CCD驅(qū)動時序電路,采用PsPICE設(shè)計了可以

2011-02-25 13:48:05 187

187 在以DSP為核心的視頻處理系統(tǒng)中,視頻采集的方法通常可以分為兩大類:自動的視頻采集和基于DSP的視頻采集。前者通常采用CPLD/FPGA控制視頻解碼芯片,通過FIFO或者雙口RAM向DSP傳送數(shù)據(jù)

2011-09-14 17:05:31 2302

2302

針對圖像處理要求運行復雜靈活的圖像處理算法和大數(shù)據(jù)量的數(shù)據(jù)傳輸處理的要求,提出了一種基于DSP和FPGA架構(gòu)的嵌入式圖像處理系統(tǒng),簡要介紹了系統(tǒng)的工作原理,詳細介紹了系統(tǒng)硬

2011-12-05 14:12:28 62

62 為了提高算法效率,實時處理圖像信息,本處理系統(tǒng)是基于DSP+FPGA混用結(jié)構(gòu)設(shè)計的。業(yè)務(wù)板以FPGA為處理核心,實現(xiàn)數(shù)字視頻信號的實時圖像處理,DSP實現(xiàn)了部分的圖像處理算法和FPGA的控

2012-10-16 11:02:47 2706

2706

FPGA實現(xiàn)的視頻圖像縮放顯示,下來看看。

2016-08-29 15:02:03 29

29 基于FPGA和DSP的圖像多功能卡的設(shè)計與實現(xiàn)

2016-09-22 12:32:08 28

28 基于FPGA+DSP實時圖像采集處理系統(tǒng)設(shè)計

2017-01-03 11:41:35 9

9 基于FPGA的視頻圖像處理系統(tǒng)設(shè)計_李蓮

2017-03-19 11:38:26 21

21 基于雙DSP和雙FPGA的高速圖像處理系統(tǒng)設(shè)計_吳雷

2017-03-16 09:28:51 2

2 基于FPGA和DSP的高速圖像處理系統(tǒng)

2017-10-19 13:43:31 19

19 基于DSP和FPGA的模塊化實時圖像處理系統(tǒng)設(shè)計

2017-10-23 14:09:42 9

9 所處理的數(shù)據(jù)量少,算法結(jié)構(gòu)復雜,適于運算速度快,尋址靈活的DSP數(shù)字信號處理器進行處理。這里提出了一種FPGA+DSP相結(jié)合的實時圖像處理系統(tǒng),并應(yīng)用于傳像光線束傳遞圖像。CMOS實際采集的是光線束的出端圖像,FPGA將CMOS采集的Bayer格式的

2017-10-26 15:44:56 2

2 所處理的數(shù)據(jù)量少,算法結(jié)構(gòu)復雜,適于運算速度快,尋址靈活的DSP數(shù)字信號處理器進行處理。這里提出了一種FPGA+DSP相結(jié)合的實時圖像處理系統(tǒng),并應(yīng)用于傳像光線束傳遞圖像。CMOS實際采集的是光線束的出端圖像,FPGA將CMOS采集的Bayer格式的

2017-10-31 17:00:34 12

12 為解決高速數(shù)字圖像處理系統(tǒng)和實時性相沖突的要求,設(shè)計了以多DSP(數(shù)字信號處理器TMS320C6416)和現(xiàn)場可編程門陣列(FPGA)相結(jié)合的實時圖像處理系統(tǒng)。重點介紹了該系統(tǒng)的硬件資源選擇、基本組

2017-11-18 12:34:02 4034

4034

通過研究視頻圖像處理和視頻圖像幀格式以及FIF0緩存技術(shù),提出了基于FPGA的視頻圖像處理系統(tǒng)設(shè)計。該設(shè)計運用幀間差分法、同步FIF0緩存設(shè)計,有效避免了圖像處理系統(tǒng)設(shè)計中亞穩(wěn)態(tài)和異步信號處理等時序

2017-11-22 09:13:03 4629

4629 本文主要介紹了一種基于DSP+FPGA的實時圖像去霧增強系統(tǒng)設(shè)計,FPGA通常作為一種調(diào)度使用,圖像處理算法實現(xiàn)主要靠高速處理信號處理芯片DSP完成,在跟蹤等領(lǐng)域圖像數(shù)據(jù)只需單向進入DSP,處理后輸出相應(yīng)參數(shù)即可,在實時視頻圖像處理中大量圖像數(shù)據(jù)只需通過EMIF輸入,且輸出數(shù)據(jù)量較小可以實時完成。

2017-12-25 10:24:21 3380

3380

本文主要介紹了一種基于DSP+FPGA視頻圖像采集處理系統(tǒng)的設(shè)計與實現(xiàn),DSP-BF561作為主處理器,負責整個算法的調(diào)度和數(shù)據(jù)流的控制,完成圖像數(shù)據(jù)的采集與顯示及核心算法的實現(xiàn),FPGA作為DSP的協(xié)處理器,依托其高度的并行處理能力,完成圖像預處理中大量的累乘加運算。實驗證明系統(tǒng)達到了實時性要求。

2017-12-25 10:39:47 4504

4504

本文主要介紹了一種基于FPGA+DSP的視頻控制的智能交通燈設(shè)計。該交通燈由視頻采集、圖像處理和控制模塊組成,使用FPGA核心搭建專用高速視頻采集模塊,使用DSP處理器進行實時圖像運算,通過圖像算法提取車流量信息,最終結(jié)合模糊算法實現(xiàn)智能控制。

2018-01-09 14:15:41 1853

1853

,設(shè)計中所使用的獨立的邏輯電路較多,有的甚至使用專用的DSP芯片去處理視頻畫面的分割。雖然可以滿足對視頻圖像數(shù)據(jù)處理速度的要求,但是還需要外加CPU去協(xié)調(diào)系統(tǒng)工作,使得整個系統(tǒng)仍顯得體積較大,而且系統(tǒng)

2018-06-15 10:15:00 3148

3148

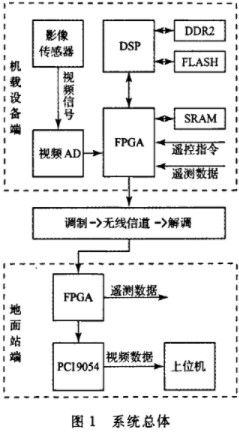

本文設(shè)計并實現(xiàn)了一種基于FPGA和DSP的機載高清視頻圖像系統(tǒng),包括機載設(shè)備端和地面站端兩部分,最高支持分辨率為1 280× 720,每秒25幀的MPEG-4實時視頻編解碼,碼速率在5 Mbps以下。并可通過上行遙控指令動態(tài)切換圖像分辨率和視頻碼率,同時實現(xiàn)了視頻數(shù)據(jù)與遙測數(shù)據(jù)的組幀傳輸。

2019-07-04 08:16:00 2043

2043

關(guān)鍵詞:Bayer , dsp , FPGA , 圖像預處理 高分辨率圖像實時處理在通信、醫(yī)學、軍事、航天航空、信息安全等領(lǐng)域有著廣泛的應(yīng)用和發(fā)展。在圖像實時處理的過程中,下層圖像預處理的數(shù)據(jù)量

2018-10-22 22:00:01 392

392 本文檔的主要內(nèi)容詳細介紹的是FPGA視頻教程之FPGA在視頻圖像處理領(lǐng)域的應(yīng)用視頻資料說明。

2019-04-04 16:40:46 35

35 為有效提高視頻監(jiān)控應(yīng)用領(lǐng)域中多屏幕畫面顯示的清晰度、分辨度等問題,提出了一種基于FPGA的實時視頻圖像處理算法。

2019-09-13 14:53:00 3490

3490 已成為視覺測量領(lǐng)域的一個發(fā)展趨勢。本文主要研究高速實時圖像處理系統(tǒng)中的圖像采集、處理技術(shù),采用FPGA和通用DSP相結(jié)合的方法,充分發(fā)揮FPGA加通用DSP結(jié)構(gòu)的靈活性及實時處理能力。

2020-07-28 17:03:04 1135

1135

Signal Processor)處理系統(tǒng)和FPGA(Field Program—mable Gate Arrays)邏輯控制系統(tǒng)設(shè)計中的關(guān)鍵技術(shù)問題,以及JPEG圖像壓縮算法的實現(xiàn)問題.系統(tǒng)主要由視頻解碼芯片、FPGA以及DSP等組成,具有功能集成、結(jié)構(gòu)簡單、編程靈活的特點,能夠實現(xiàn)對大量細胞進

2021-01-25 16:04:00 4

4 為了改善紅外圖像的成像質(zhì)量,根據(jù)紅外圖像的特點,提出了一種改進的拉普拉斯銳化算法——受限拉普拉斯銳化算法,并采用DSP+FPGA的架構(gòu)進行實時處理。對普通拉氏銳化算法和受限拉氏銳化算法的處理效果進行比較。受限拉氏銳化算法有效地控制了圖像的噪聲,使處理后的圖像邊緣更加清晰,又保護了圖像的細節(jié)。

2021-01-25 16:04:00 6

6 介紹了一種以DSP為核心的圖像系統(tǒng)中,以FPGA為數(shù)據(jù)采集邏輯控制單元,用DSP控制實現(xiàn)了黑白全電視信號圖象數(shù)據(jù)采集。在介紹了系統(tǒng)組成原理的基礎(chǔ)上,詳細討論了采集部分的結(jié)構(gòu)和FPGA的控制邏輯

2021-01-26 15:02:00 2

2 針對兩軸電視經(jīng)緯儀動基座跟蹤目標時,視軸無法隔離載體擾動造成圖像旋轉(zhuǎn)現(xiàn)象,提出一種基于數(shù)學平臺的電子消旋方法,采用捷聯(lián)式慣導+DSP+FPGA的硬件系統(tǒng)通過反向旋轉(zhuǎn)和雙線性插值對圖像進行消旋和填充

2021-02-01 16:11:03 3

3 ITU-656標準數(shù)字視頻格式,用VHDL硬件描述語言實現(xiàn)整個消像旋算法的FPGA設(shè)計。實驗結(jié)果表明,旋轉(zhuǎn)角度在0°~360°之間,能實時消除探測器轉(zhuǎn)動引起的圖像旋轉(zhuǎn),旋轉(zhuǎn)后圖像清晰穩(wěn)定。因而基于FPGA和DSP實現(xiàn)實時圖像消旋(旋轉(zhuǎn))的方法具有很大的實際應(yīng)用

2021-02-04 16:46:00 10

10 ,使用~tera的Quartus II軟件,完成了其中的核心模塊——F盯算法的硬件實現(xiàn),提高了處理速度;并運用DSP處理器,設(shè)計了一個基于FPGA的實時數(shù)字圖像處理系統(tǒng).文中給出了系統(tǒng)的硬件電路和軟件算法模塊.仿真和調(diào)試結(jié)果表明:用FPGA與高速數(shù)字信

2021-02-05 15:54:00 139

139 該文在闡述了灰度圖像順序形態(tài)變換的基礎(chǔ)上,介紹了順序形態(tài)變換硬件實現(xiàn)的圖像處理系統(tǒng).該系統(tǒng)采用DSP+FPGA的框架結(jié)構(gòu),利用FPGA的可重構(gòu)特性將其中一片FPGA作為協(xié)處理器可以實現(xiàn)不同的圖像處理

2021-04-01 11:21:46 8

8 今天給大俠帶來基于FPGA的數(shù)字視頻信號處理器設(shè)計,由于篇幅較長,分三篇。今天帶來第三篇,下篇,程序測試與運行。話不多說,上貨。 之前也有圖像處理相關(guān)方面的文章,這里超鏈接幾篇,給各位大俠作為

2021-07-13 09:30:01 2457

2457

電子發(fā)燒友App

電子發(fā)燒友App

評論