摘要:介紹了相乘微分型AFC環解調FSK信號的原理,分析了環路的控制模型。采用模塊化的設計思想,利用VHDL語言設計了相乘微分型AFC環路,闡述了關鍵部件的設計方法。在Xilinx的FPGA器件XC3S200-4FT200上對AFC環進行了實現,利用Modelsim6.0軟件進行了仿真測試。仿真結果表明,環路工作穩定,滿足性能要求。

1 引言

FSK(Frequency Shift Keying ,頻移鍵控)是繼ASK(Amplitude Shift Keying,振幅鍵控)之后出現比較早的一種調制方式。由于FSK的抗衰落能力較強,因而在一些衰落信道的傳輸中得到了廣泛的應用[1]。近年來,數字調頻技術有了相當大的發展。CPFSK(Continuous Phase Frequency Shift Keying ,連續相位頻移鍵控)在調制指數h=0.7及采用相干檢測及延遲判決的條件下,功率與頻帶利用方面可以達到比BPSK(Binary Phase Shift Keying,二進制相移鍵控)好1dB的水平。MSK(Minimum Shift Keying,最小頻率鍵控)在功率與頻帶的利用方面都與4PSK相當,而且它的頻譜特性比PSK信號優越,已在數字衛星通信系統中采用[2]。

FSK信號的解調方法很多,總的來講可以分為相干解調法和非相干解調法兩類。相干解調法是指需要獲取相干載波信號的解調方法,非相干解調法則不需在解調前獲取相干載波。從抗干擾性能看,相干解調法是最佳的,但從FSK信號中提取相干載波比較困難,實現技術相對較為復雜,所需硬件資源也較多,故目前多采用非相干解調法。文獻[1]給出的一種最佳非相干解調器結構,在相同誤碼率的條件下,所需的信噪比只比相干解調法高1~2dB。非相干解調法的種類很多,如基于FFT的頻譜分析法[3、4]、基于自適應濾波的解調法[5]、差分檢波算法[6]、AFC(Automatic Frequency Control,自動頻率控制)環解調法等。

近年來,隨著可編程邏輯器件的發展,采用FPGA實現信號解調等數字系統具有速度快、使用靈活、可編程配置等一系列優點,已逐漸成為數字通信系統設計與實現的首選方案。本文主要討論相乘微分型AFC環解調FSK信號的原理及FPGA(Field Programmable Gate Array,現場可編程門陣列)實現方法。

2 AFC環解調FSK信號的工作原理

2.1 相乘微分型AFC環原理

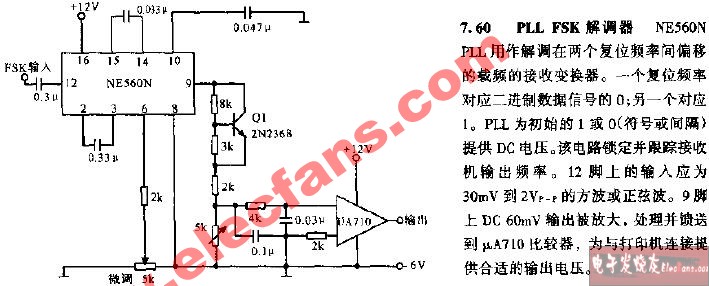

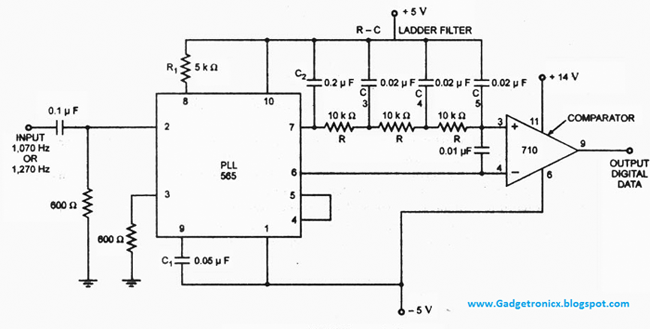

AFC環是一個負反饋系統,從電路結構上看,AFC環主要有3種結構形式[7]:相乘微分型、延遲叉積型以及離散傅立葉變換型。本文只討論應用比較廣泛的相乘微分型AFC環路。

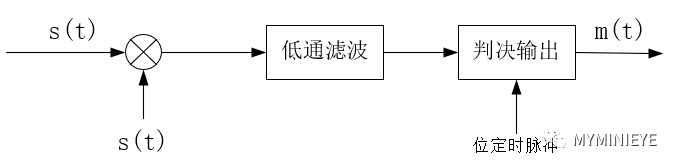

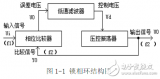

相乘微分型AFC環路的結構如圖1所示[7]。如果接收信號與本振信號存在頻差,則在一定時間間隔內必然存在相差,將鑒相器輸出的相位誤差信號微分后,得到反映頻差的誤差信號,此信號經環路濾波器平滑處理后,控制VCO(Voltage Controlled Oscillator,壓控振蕩器)的振蕩頻率向輸入信號頻率靠近,最終使得頻差近似為零。

設輸入信號

濾波判決,即可完成FSK信號的解調。

2.2 AFC環的數學模型分析

由相乘微分型AFC環路的工作原理可知,AFC環是一個頻率負反饋系統,可以得到圖2所示的AFC環路的頻率控制模型。環路中,鑒頻器的輸出電壓與頻率誤差信號成正比。對于無線通信中常用的鎖相環路來講,VCO的輸出信號對相位信號有一個積分關系,壓控振蕩器是鎖相環路中的固有積分環節[9];在AFC環路中,VCO的輸出信號與信號頻率成正比,環路不再具有積分環節,因此,整個AFC環不是一個二階線性系統,而是更為簡單的一階線性系統。

?

AFC環路的工作過程完全可以采用通用的一階線性環路模型來進行分析。根據一階線性環路的工作原理可知[8],環路鎖定的條件是環路增益K 必須大于固有頻差Δω ,且環路增益越大,則捕獲及鎖定時間越短。由圖2可以看出,環路增益由鑒頻器、濾波器、VCO增益組成,控制環路總增益的方法比較靈活,可以通過增加環路中任何一個環節的增益來實現提高環路總增益的目的。

3 AFC環的VHDL設計

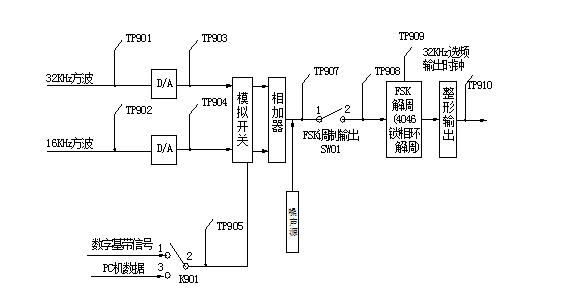

工程實例中,輸入數據為連續相位的2FSK信號,量化位數為8比特,原始數據速率為4Mbit/s,采樣速率為32MHz,載波頻率為6MHz,調制指數為0.715,FPGA系統時鐘速率為32MHz。

3.1 環路參數設計

(1) 濾波器參數設計

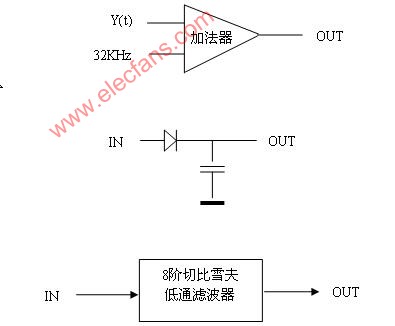

由圖1所示,AFC環中有3個濾波器,其中兩個正交支路的低通濾波器完全相同,用于濾除前級混頻后的高頻分量;環路濾波器用于濾除鑒頻器(由微分器及乘法器組成)輸出產生的高頻分量,產生VCO的控制信號。低通濾波器通帶截止頻率選擇與信號帶寬一致,考慮發射端成形濾波器的作用,本實例中取3.6MHz。過渡帶帶寬的選擇原則為[9]:一是必須確保濾除相鄰的A/D鏡像頻率成分;二是需要濾除數字下變頻引入的倍頻分量,本實例中取8.4MHz。

根據AFC環的工作原理,鑒頻器的輸出信號反映了原始調制數據的變化情況,為進一步簡化解調器結構,可以將環路濾波器也設計成FIR低通濾波器,這樣就可以直接從環路濾波器的輸出信號中獲取解調數據。環路濾波器的帶寬、過渡帶等參數與混頻器的低通濾波器保持一致。

采用MATLAB很容易根據濾波器參數設計出FIR濾波器的系數并畫出頻率響應圖,如圖3。

設計出FIR濾波器系數后,還需要對其進行量化處理,以適應FPGA處理。13比特量化后的濾波器系數如下:

h_pm=[ 20,77,28,-197,-319,123,1145,2047,2047,1145,123,-319,-197,28,77,20]

由于中頻信號的采樣位數為8比特,本地振蕩器的輸出載波信號也選用8比特。根據二進制乘法原理,考慮節約寄存器字長,同時保留全部有效數據位,AFC環前端混頻乘法器為8 × 8的乘法器,取低15比特的有效位輸出數據。混頻器的低通濾波器取全部的28比特有效位輸出數據。環路濾波器的濾波器系數與混頻器中的濾波器完全相同,但輸入輸出數據位寬不同,輸入數據位寬由積分器及后端的加法器決定。本實例中,環路濾波器輸入有效數據位寬取17比特,輸出信號取全部30比特有效數據。

(2) 微分器參數設計

采用FPGA進行數學意義上的微分運算十分困難。根據微分的運算規則,可以采用一種簡單的近似處理方法,即通過求取前后兩個數據之差來代替微分運算。前后兩個數據之間的時間間隔為一個系統時鐘周期,則有

根據式(6)可知,采用前后兩個數據之差來代替微分運算,相當于數學上的微分運算乘以系統時鐘速率這個常數,反映在整個AFC環路上則相當于環路增益乘了一個常數。

由圖1所示,微分運算后還需要進行乘加運算,考慮到FPGA芯片中集成的硬件乘法器IP核大多數都是18x18比特的,綜合考慮運算速度、硬件資源及運算精度,微分器后面直接采用18x18比特的乘法器,且取36比特輸出數據,這樣乘法后面的減法運算不再需要進行符號位擴展,可直接相減。

根據上面的分析,環路濾波器的輸入數據位寬為36比特。如果采用所有36比特數據作為濾波器輸入,則需耗費大量的硬件資源,濾波器輸出數據位寬也將達到49比特。這樣多的數據位寬雖然可以獲得極高的運算精度,但所需的代價是硬件資源的成倍增加,以及運算速度的降低。綜合考慮各種因素的影響,該實例采用17比特有效數據作為環路濾波器的輸入,濾波器的有效輸出數據位寬為30比特。

(3) NCO參數設計及環路增益計算

FPGA中可以采用NCO(Numerical Controlled Oscillator,數字控制振蕩器)來實現VCO的功能。NCO的參數設計比較簡單,驅動時鐘頻率取系統時鐘即可,為32MHz;頻率字位寬取環路濾波器輸出的有效數據位寬,為30比特;頻率字更新周期取一個系統時鐘周期;輸出的本地載波信號數據位寬與輸入數據位寬相同,為8比特。則NCO的頻率分辨率

解調,環路增益K 只要大于1.43M即可, K 值越大,則環路鎖定速度越快。

對于AFC環來講,整個AFC環路為線性一階環,環路的增益實際上就是NCO的輸入電壓幅值與頻率字更新周期的乘積。考慮到微分運算對環路增益的貢獻,由于NCO的輸入數據有效位寬為30比特,則環路總增益因此,環路能夠穩定跟蹤FSK信號的變化,解調出原始數據。

3.2 環路的VHDL設計

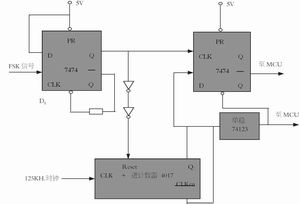

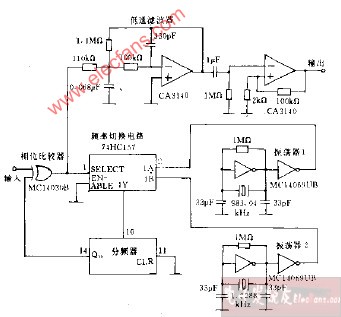

根據圖1的結構,在完成AFC環路各部件的參數設計之后,本文采用VHDL語言對相乘微分型AFC環進行了設計,圖4是AFC環頂層文件用Synplify Pro綜合后的RTL原理圖。由圖4中可以清楚地看出系統由1個NCO模塊(u0),2個8×8 bit的乘法器模塊mult8_8(u1,u2),2個低通濾波器模塊fir_lpf(u3,u4),1個環路濾波器模塊(u5),1個鑒頻器模塊FrequencyD(U6)以及少量邏輯電路組成。其中的nco模塊、乘法器模塊、低通濾波器模塊、環路濾波器模塊均由ISE提供的IP核直接產生。鑒頻器由兩個微分器、兩個乘法器及一個減法器組成,其中微分器采用前后兩個數據相減的方法獲取。

4 AFC環的FPGA實現及仿真測試

本實例的目標器件為XC6SLX16-2CSG225,FPGA實現后,查找表資源(Slice LUTs)占用了491個(5%),存儲塊資源(RAMB8BWERs)占用了1個(1%),乘法器DSP資源(DSP48A1s)占用了28個(87%),全局時鐘資源(BUFG/BUFGMUXs)占用了1個(6%)。最高系統時鐘頻率可達83.25MHz,顯然滿足工程實例中要求的32MHz。從系統所占用的資源來看,普通邏輯資源占用較少,乘法器資源用得比較多,乘法器資源主要用于濾波器等乘法運算。

進行系統的FPGA測試之前,首先需要編寫測試激勵文件代碼產生測試數據。測試數據通過MATLAB軟件仿真產生,并將量化后的數據寫入TXT文本文件中,激勵文件通過讀取TXT文件內容產生測試數據。

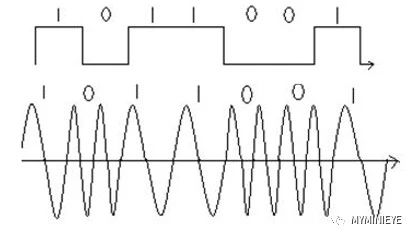

圖5為采用Modelsim 6.0軟件仿真AFC解調FSK信號的工作波形圖。從仿真圖中可以清楚地看出環路濾波器的輸出信號,即FSK的解調信號dout呈現規則波形,只需對解調信號進行抽樣判決即可完成FSK信號的數據解調。

5 結束語

FSK信號的解調方法很多,非相干解調法因為實現簡單,性能優良而得到了更為廣泛的應用。本文對相乘微分型AFC環的模型進行了討論。在進行環路的FPGA實現時,關鍵在于設計環路各部件的參數,以及運算中數據有效字長的處理。仿真結果表明,設計的相乘型AFC環可以有效解調FSK信號。

電子發燒友App

電子發燒友App

評論