如何檢測(cè)I2C的開(kāi)始條件和結(jié)束條件:

開(kāi)始條件檢測(cè):

(1)盡量選用帶復(fù)位輸人的I2C從器件,從I2C總線死鎖產(chǎn)生的原因可以發(fā)現(xiàn)I2C總線死鎖的一個(gè)必要條件是主設(shè)備復(fù)位了而從設(shè)備沒(méi)有復(fù)位。

如果從設(shè)備選用帶復(fù)位輸入的芯片,將主從設(shè)備的復(fù)位信號(hào)連接在一起,當(dāng)外部產(chǎn)生復(fù)位事件時(shí),主從設(shè)備同時(shí)復(fù)位,這樣就不會(huì)發(fā)生I2C總線死鎖現(xiàn)象了。

這種方法的缺點(diǎn)也是顯而易見(jiàn)的,首先,大部分I2C從器件都沒(méi)有復(fù)位輸入,器件選型受到了很大的限制;其次,這種對(duì)于主設(shè)備集成看門(mén)狗引起的復(fù)位也沒(méi)有效果。

(2)將所有的從I2C設(shè)備的電源連接在一起,通過(guò)M0S管連接到主電源,而MOS管的導(dǎo)通關(guān)斷由I2C主設(shè)備來(lái)實(shí)現(xiàn)一般來(lái)說(shuō),I2C主設(shè)備都是具有運(yùn)算單元的處理器。控制功能可以通過(guò)處理器的GPIO來(lái)實(shí)現(xiàn)。

每次主設(shè)備復(fù)位時(shí),運(yùn)行程序控制GPIO關(guān)斷MOS,使從設(shè)備失去電源。然后延時(shí)一段時(shí)間后再導(dǎo)通MOS管,給從設(shè)備上電,從而達(dá)到讓從設(shè)備強(qiáng)制復(fù)位的效果。

這種方法能彌補(bǔ)第一種方法的不足,但是會(huì)增加電源設(shè)計(jì)的復(fù)雜性,影響Layout設(shè)計(jì)時(shí)電源的完整性;同時(shí)還需要更改處理器的底層boot代碼,影響底層軟件的通用性和可移植性。

結(jié)束條件檢測(cè):

在I2C主設(shè)備中增加I2C總線恢復(fù)程序。

每次I2C主設(shè)備復(fù)位后,如果檢測(cè)到SDA數(shù)據(jù)線被拉低,則控制I2C中的SCL時(shí)鐘線產(chǎn)生9個(gè)時(shí)鐘脈沖(針對(duì)8位數(shù)據(jù)的情況),這樣I2C從設(shè)備就可以完成被掛起的讀操作,從死鎖狀態(tài)中恢復(fù)過(guò)來(lái)。

這種方法有很大的局限性,因?yàn)榇蟛糠种髟O(shè)備的I2C模塊由內(nèi)置的硬件電路來(lái)實(shí)現(xiàn)。軟件并不能夠直接控制SCL信號(hào)模擬產(chǎn)生需要時(shí)鐘脈沖。使用此種方法可以使用IO模擬I2C,SCL時(shí)鐘易控制。

I2C總線SDA\SCL以及開(kāi)始終止條件

I2C只用兩條線(SDA和SCL)在連接到總線上的設(shè)備之間傳送數(shù)據(jù)。每一個(gè)設(shè)備都由唯一的地址來(lái)識(shí)別(不管是微處理器、LCD驅(qū)動(dòng)器、存儲(chǔ)器或者鍵盤(pán)接口),并且可以依照設(shè)備的功能作為發(fā)送器或者接收器使用.LCD驅(qū)動(dòng)器可能只是個(gè)接收器,而存儲(chǔ)器可以發(fā)送和接受數(shù)據(jù)。除了發(fā)送器和接收器,當(dāng)傳送數(shù)據(jù)時(shí)設(shè)備還可以作為主機(jī)或者從機(jī)。主機(jī)就是初始化數(shù)據(jù)傳輸和產(chǎn)生時(shí)鐘信號(hào)的設(shè)備,在那個(gè)時(shí)刻,任何被尋址的設(shè)備都是從機(jī)。

I2C總線是一個(gè)多主機(jī)總線。意味著可以連接多個(gè)可以控制總線的設(shè)備到總線上。主機(jī)通常是微控制器,我們可以考慮以下兩個(gè)連接到總線上的微處理器之間的數(shù)據(jù)傳輸?shù)那闆r。

這個(gè)例子中突出了I2C總線中的主從和接收器-發(fā)送器之間的關(guān)系。注意這些關(guān)系不是固定的,僅依賴(lài)于當(dāng)前時(shí)刻數(shù)據(jù)傳輸?shù)姆较颉?shù)據(jù)傳輸?shù)倪^(guò)程如下:

1.假定微控制器A向微控制器B發(fā)送數(shù)據(jù)

微控制器A(主機(jī))尋址微控制器B(從機(jī))

微控制器A(主機(jī)-發(fā)送器)發(fā)送數(shù)據(jù)到微控制器B(從機(jī)-接收器)

微控制器A結(jié)束數(shù)據(jù)傳輸

2.假定微控制器A從微控制器B接收數(shù)據(jù)

微控制器A(主機(jī))尋址微控制器B(從機(jī))

微控制器A(主機(jī)-接收器)從微控制器B(從機(jī)-發(fā)送器)接收數(shù)據(jù)

微控制器A結(jié)束數(shù)據(jù)傳輸

甚至在這種情況下,主機(jī)(微控制器A)產(chǎn)生時(shí)序并終止傳輸。

在多個(gè)微控制器連接到I2C總線上時(shí)意味著可能有多個(gè)主機(jī)嘗試初始化數(shù)據(jù)傳輸。為了避免由此引發(fā)的混亂,設(shè)計(jì)了一個(gè)仲裁機(jī)制。它依靠線與邏輯連接所有I2C接口道I2C總線。

如果有多個(gè)主機(jī)嘗試發(fā)送信息到總線上,在其它產(chǎn)生“0”的情況下,首先產(chǎn)生“1”的主機(jī)會(huì)丟擲仲裁。仲裁時(shí)的時(shí)鐘信號(hào)是用線與連接到SCL線的主機(jī)產(chǎn)生的時(shí)鐘的同步結(jié)合。

I2C總線上的主機(jī)設(shè)備通常負(fù)責(zé)產(chǎn)生時(shí)鐘,當(dāng)傳輸數(shù)據(jù)時(shí)每個(gè)主機(jī)產(chǎn)生自己的時(shí)鐘信號(hào)。只有在低速?gòu)脑O(shè)備控制時(shí)鐘線或者仲裁發(fā)生時(shí),主機(jī)的總線時(shí)鐘才會(huì)被改變。

下表總結(jié)了I2C總線中的一些配置選擇:

[1]這里也指被當(dāng)作從機(jī)的主機(jī)

[2]時(shí)鐘拉伸是部分從機(jī)的特性。如果在系統(tǒng)中沒(méi)有從機(jī)可以拉伸時(shí)鐘(將SCL拉低),主機(jī)一定需要設(shè)計(jì)處理程序

[3]‘Bit banging’(軟件模擬)多個(gè)主機(jī)系統(tǒng)應(yīng)該考慮START字節(jié)

SDA和SCL信號(hào)

SDA和SCL都是雙向線路,通過(guò)電流源或者上拉電阻連接到一個(gè)正向電壓。(見(jiàn)下圖)當(dāng)總線空閑時(shí),兩條線都是高電平。連接到總線的設(shè)備的輸出級(jí)必須是OD(漏極開(kāi)路)或者OC(集電極開(kāi)路)門(mén)才能執(zhí)行線與功能。在標(biāo)準(zhǔn)模式下I2C總線傳輸數(shù)據(jù)可以達(dá)到100kb/s的速度,而在快速模式下達(dá)到400kb/s的速度,快速plus模式下是1Mb/s的速度,告訴模式下是3.4Mb/s的速度。總線的電容限制連接到總線上的接口數(shù)量。

對(duì)于一個(gè)單一主機(jī)的應(yīng)用,如果總線上沒(méi)有設(shè)備可以拉低時(shí)鐘那么主機(jī)的SCL輸出應(yīng)該是push-pull(推挽)驅(qū)動(dòng)設(shè)計(jì)。

SDA和SCL的邏輯電平

由于有各種不同的工藝的設(shè)備(CMOS NMOS 雙極性)可以連接到I2C總線,低電平和高電平不是固定的而是依賴(lài)于相對(duì)應(yīng)的VDD的電平。

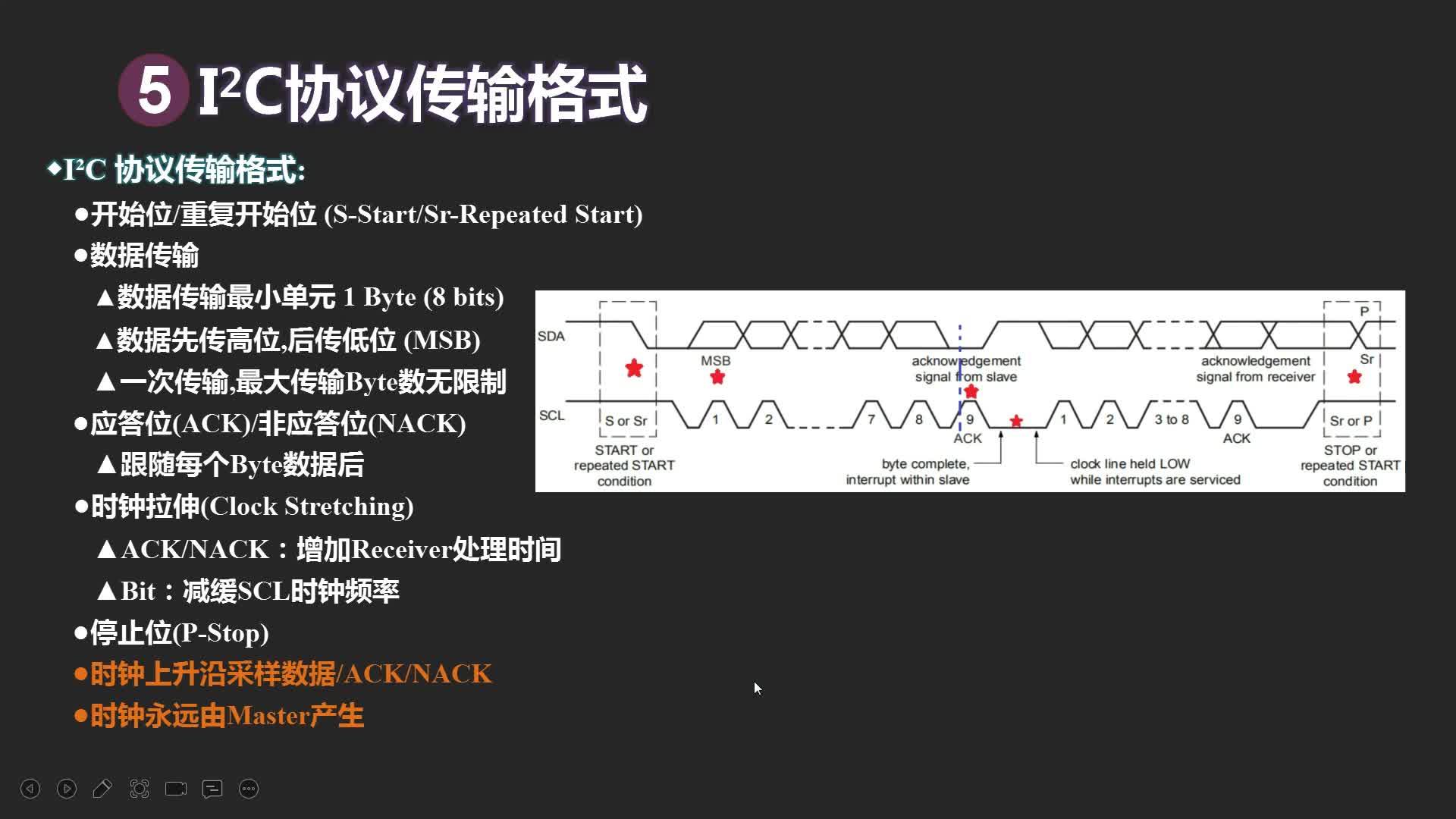

數(shù)據(jù)有效性

在時(shí)鐘為高期間SDA線上的數(shù)據(jù)必須穩(wěn)定。只有在SCL線上的時(shí)鐘信號(hào)低時(shí)數(shù)據(jù)線才可以改變高低狀態(tài)。每個(gè)數(shù)據(jù)位傳輸都需要一個(gè)時(shí)鐘產(chǎn)生。

開(kāi)始和終止條件

所有的傳輸都由一個(gè)START(S)開(kāi)始,有一個(gè)STOP(P)終止。

START條件是當(dāng)SCL高時(shí)SDA從高到低

STOP條件是SCL高時(shí)SDA從低到高

開(kāi)始條件和終止條件一直由主機(jī)產(chǎn)生。在開(kāi)始條件后總線就處于忙狀態(tài)。在終止條件后隔上一個(gè)固定時(shí)間總線就處于空閑狀態(tài)。如果沒(méi)有終止條件產(chǎn)生,而是一個(gè)重復(fù)的開(kāi)始條件(Sr),那總線依舊是忙狀態(tài)。這種情況下S和Sr在功能上是一樣的。

如果連接到總線的設(shè)備包含了必須的接口硬件那么開(kāi)始條件和終止條件的檢測(cè)時(shí)很容易的。但是沒(méi)有這樣接口的微控制器在每個(gè)時(shí)鐘周期內(nèi)至少要采樣兩次SDA線來(lái)識(shí)別有沒(méi)有電平變化.

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論