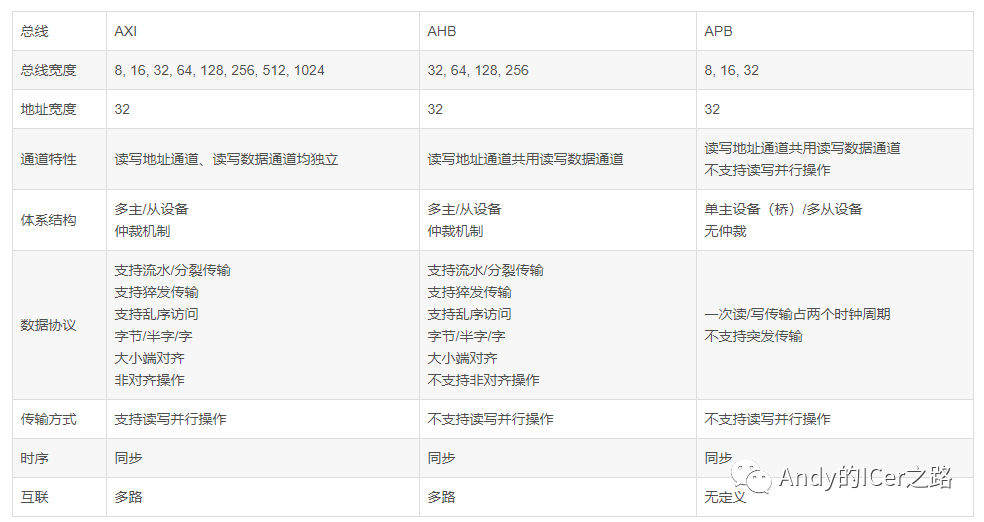

帶寬/BandWidth?和延遲/Latency?是衡量總線性能最重要的兩個(gè)因素。

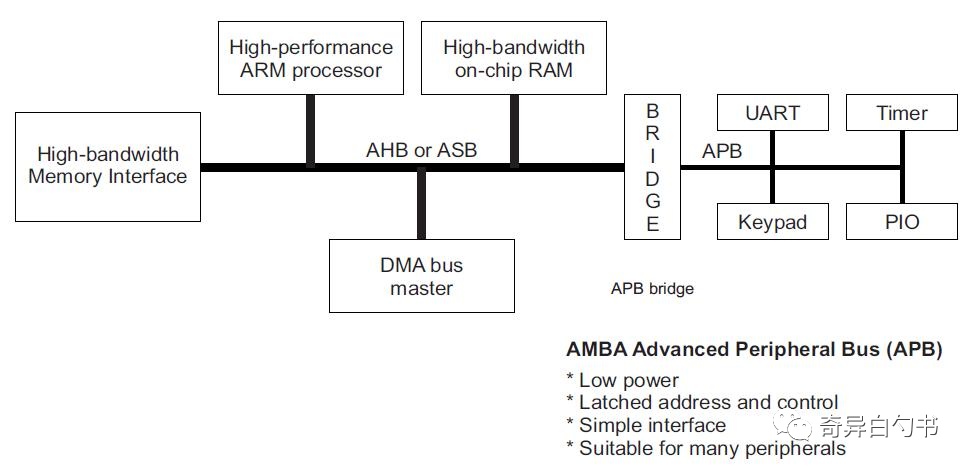

1.1 What is AMBA??

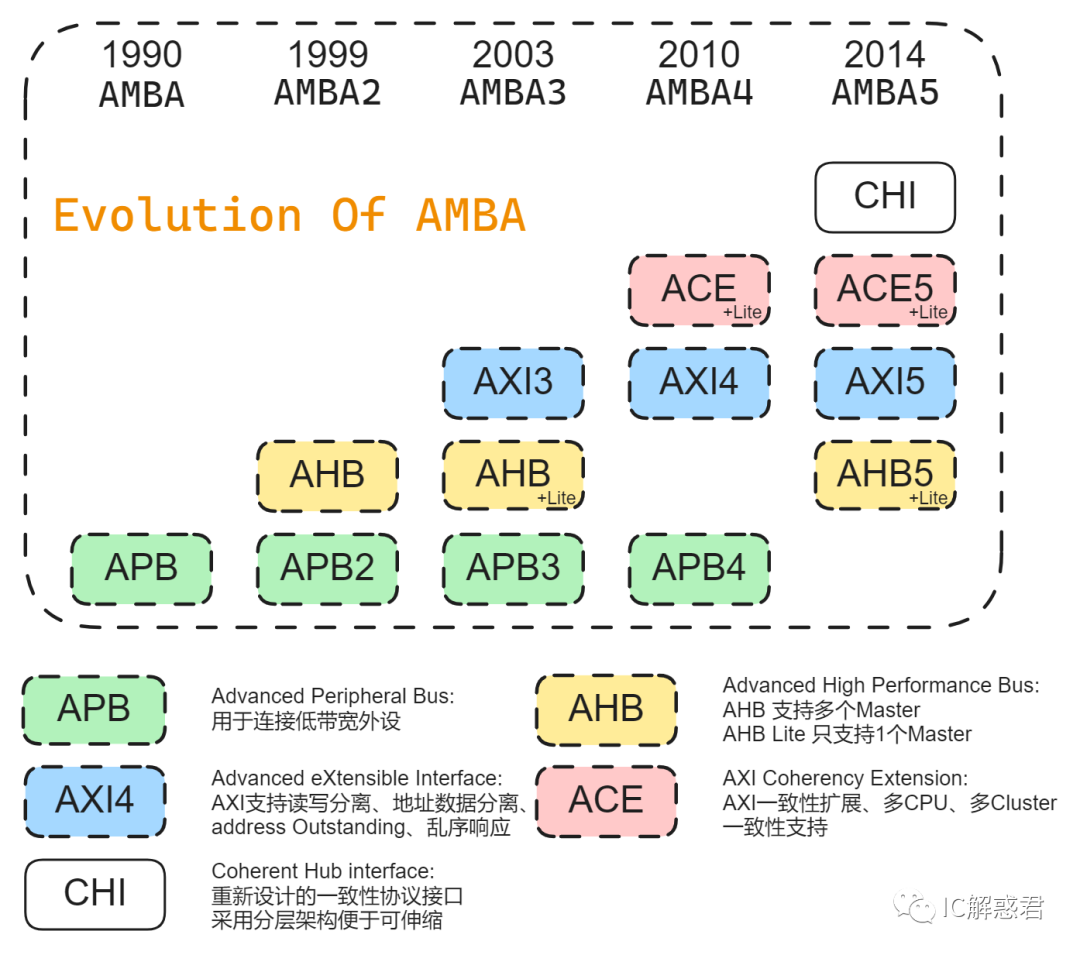

AMBA全稱Advanced Microcontroller Bus Architecture(高級(jí)微控制總線架構(gòu)),是一種開(kāi)放的、標(biāo)準(zhǔn)的片上互聯(lián)總線規(guī)范協(xié)議簇。從本質(zhì)上來(lái)說(shuō),AMBA協(xié)議簇定義了片上功能模塊是如何進(jìn)行相互通信。同時(shí)隨著時(shí)間演化,已經(jīng)從AMBA到現(xiàn)在的AMBA5。協(xié)議簇的演化路徑如下圖所示:

1.2?Example for AMBA

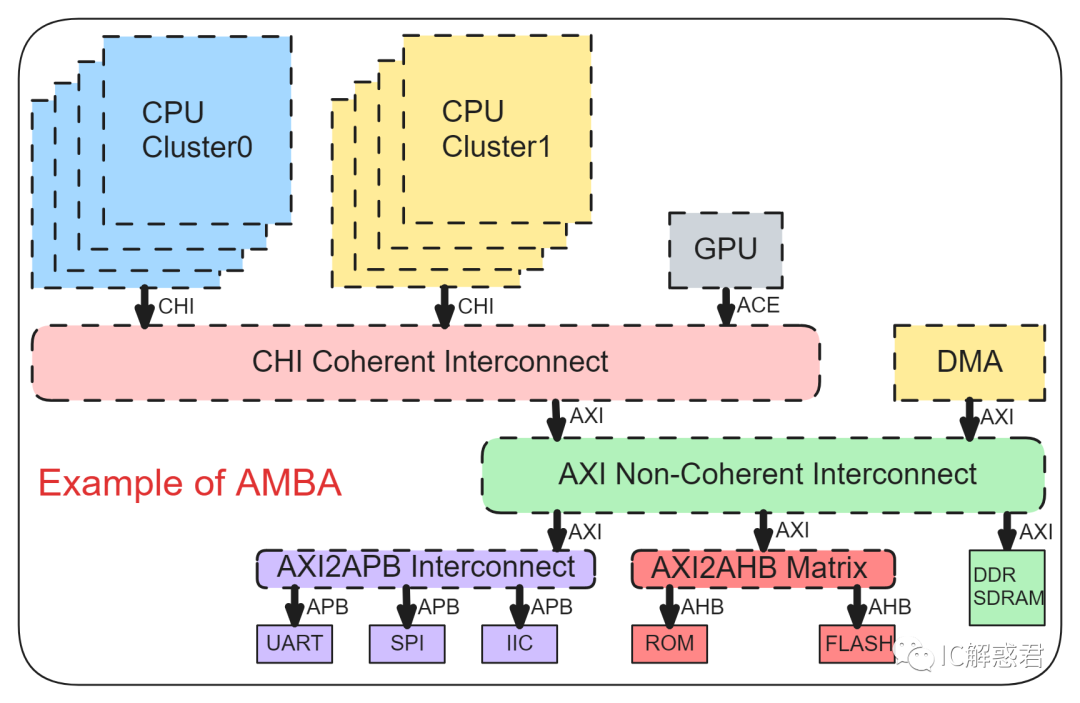

如上圖所示的SoC設(shè)計(jì)實(shí)例。通過(guò)AMBA協(xié)議連接了各個(gè)功能模塊,比如CPU、GPU、DMA、DDR等。AMBA協(xié)議通過(guò)簡(jiǎn)化和規(guī)范了模塊接口信號(hào),使得IP設(shè)計(jì)更加靈活兼容的同時(shí)也促進(jìn)了IP的多次復(fù)用。

1.3 This text Focus on

本文主要集中在AMBA協(xié)議中的AXI4協(xié)議。之所以選擇AXI4作為講解,是因?yàn)檫@個(gè)協(xié)議在SoC、IC設(shè)計(jì)中應(yīng)用比較廣泛。

2.1?Brief Introduction of?AXI4?

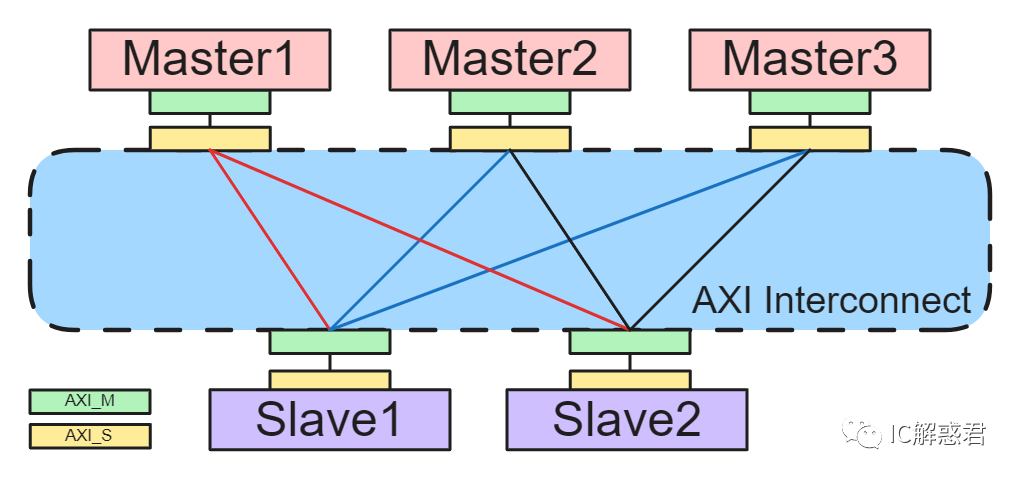

AXI協(xié)議描述了單向數(shù)據(jù)傳輸的過(guò)程,在使用AXI協(xié)議構(gòu)建的系統(tǒng)中,有兩種AXI接口:Manager(Master)、Subordinate(Slave)。AXI Manager接口只能和AXI Subordinate接口連接。AXI Manager(AXI_M)接口發(fā)起AXI讀寫(xiě)命令,AXI?Subordinate接口接收到AXI讀寫(xiě)命令之后給出響應(yīng)。

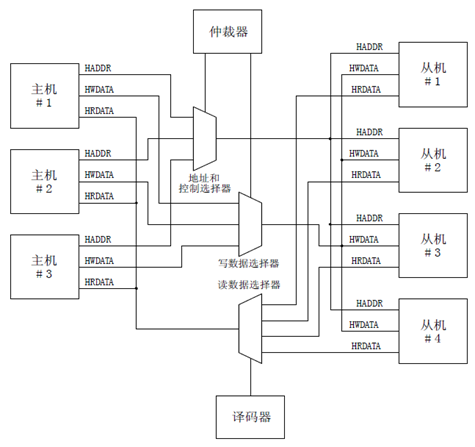

AXI協(xié)議是一個(gè)點(diǎn)對(duì)點(diǎn)接口規(guī)范,而不是SoC互聯(lián)總線協(xié)議。所以如果想要連接多個(gè)AXI Master和多個(gè)AXI Slave時(shí),就需要實(shí)現(xiàn)互聯(lián)總線結(jié)構(gòu)。如下圖所示:

上文提到,AXI協(xié)議本身只規(guī)定了點(diǎn)對(duì)點(diǎn)接口之間的信號(hào)個(gè)數(shù)、時(shí)序特性。所以上圖多個(gè)Master的AXI Interconnect模塊只是在接口上遵守了AXI協(xié)議,互聯(lián)總線內(nèi)部的拓?fù)浣Y(jié)構(gòu)、仲裁機(jī)制、路由機(jī)制、流控機(jī)制等和AXI協(xié)議本身沒(méi)有關(guān)系,取決于設(shè)計(jì)者的思路和應(yīng)用場(chǎng)景。

PS : 可以用Synopsys?DesignWare?、Arm Socrates等工具生成符合應(yīng)用場(chǎng)景(PPA)的AXI接口的互聯(lián)總線。

2.2?AXI Channel Overview

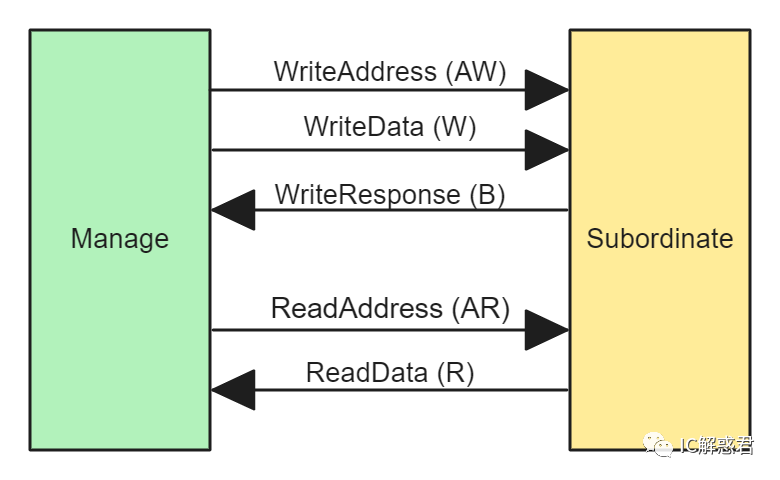

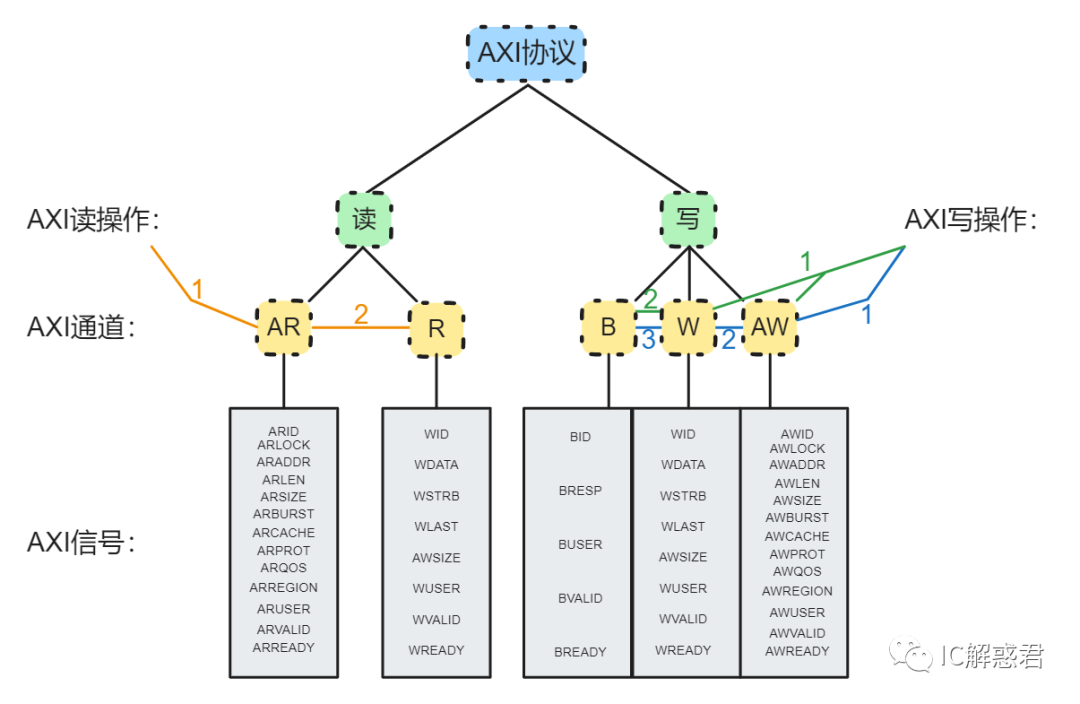

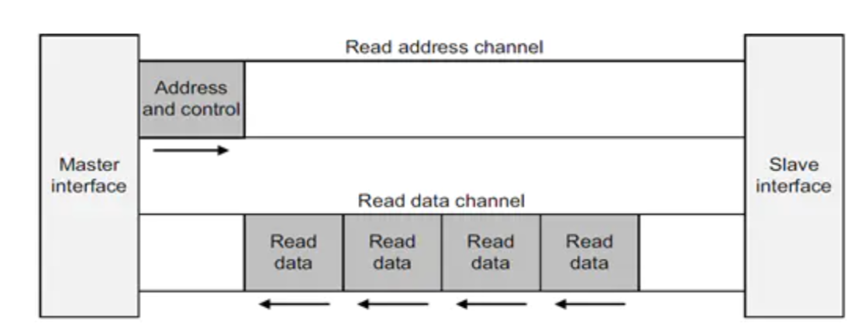

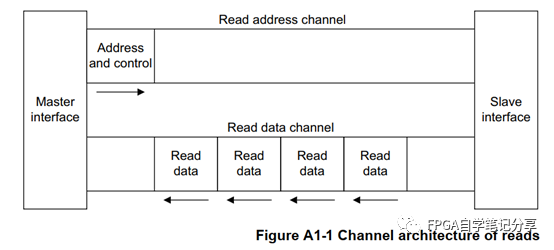

AXI協(xié)議規(guī)定了AXI Manager和AXI Subordinate之間點(diǎn)對(duì)點(diǎn)的信號(hào)個(gè)數(shù)、時(shí)序特性。AXI協(xié)議用于AXI?Manager和AXI?Subordinate接口之間數(shù)據(jù)的傳輸。AXI協(xié)議將所有的信號(hào)分成五個(gè)通道,分別是寫(xiě)地址通道(AW)、寫(xiě)數(shù)據(jù)通道(W)、寫(xiě)響應(yīng)通道(B)、讀地址通道(AR)、讀數(shù)據(jù)通道(R)。如下圖所示:

寫(xiě)數(shù)據(jù): 1. Manager 通過(guò)Write Address(AW)通道向Subordinate發(fā)出想要寫(xiě)數(shù)據(jù)的地址 2. Manager 通過(guò)Write Data(W)通道向Subordinate發(fā)出寫(xiě)數(shù)據(jù)

3. Subordinate收到地址和數(shù)據(jù)后完成寫(xiě)入操作,并通過(guò)Write Response(B)通道告訴Manager當(dāng)前的地址和數(shù)據(jù)寫(xiě)入是否成功(寫(xiě)響應(yīng)) ? ? 讀數(shù)據(jù): 1.?Manager 通過(guò)Read?Address(AR)通道向Subordinate發(fā)出想要讀數(shù)據(jù)的地址

2.?Subordinate收到地址后,通過(guò)Read Data(R)通道向Manager返回需要的數(shù)據(jù)(讀數(shù)據(jù))。

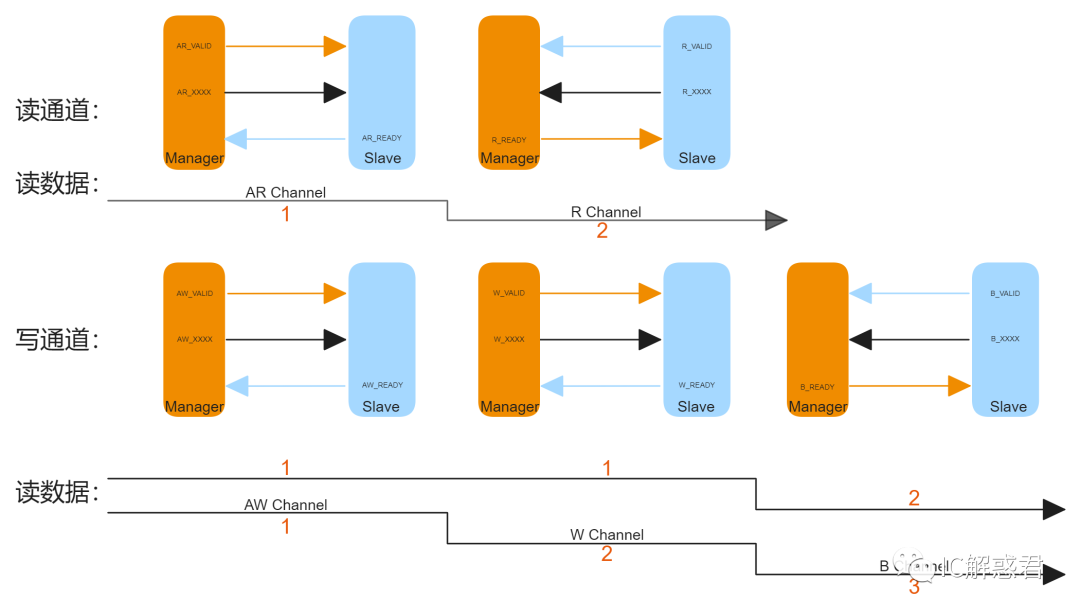

PS?: AXI?Manager在發(fā)起寫(xiě)操作的時(shí)候,可以先發(fā)寫(xiě)地址,再發(fā)寫(xiě)數(shù)據(jù),最后等待寫(xiě)響應(yīng)。同時(shí),AXI?Manager也可以同時(shí)發(fā)出寫(xiě)地址和寫(xiě)數(shù)據(jù),最后等待寫(xiě)響應(yīng),如上圖所示。 PS?: AXI協(xié)議所定義的讀寫(xiě)通道并不對(duì)稱,可以看到寫(xiě)數(shù)據(jù)包含三個(gè)通道(AW、W、B),讀數(shù)據(jù)包含兩個(gè)通道(AR、R)。因?yàn)镾lave返回的讀命令響應(yīng)可以伴隨著數(shù)據(jù)一起返回。 ? 2.2?AXI Channel Transfer Overview ? 上文提到,AXI協(xié)議將信號(hào)分為五個(gè)通道。讀寫(xiě)操作需要五個(gè)通道的配合完成;對(duì)于寫(xiě)操作,需要AW、W、B通道配合。對(duì)于讀操作,需要AR、R通道配合。 而對(duì)于每個(gè)通道的數(shù)據(jù)傳輸,需要通道內(nèi)信號(hào)在時(shí)間上組合來(lái)完成數(shù)據(jù)傳輸。如下圖示,AXI協(xié)議中的五個(gè)通道,每個(gè)通道中都有相同的握手機(jī)制。 ?

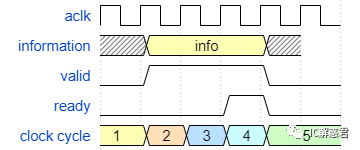

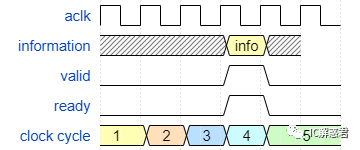

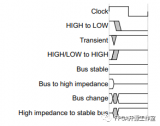

2.3?AXI Channel Transfer Timing Overview ? 上文提到,AXI協(xié)議中的通道的數(shù)據(jù)傳輸是依靠握手機(jī)制。source通過(guò)拉高Valid信號(hào)指示有數(shù)據(jù)發(fā)送。而destination拉高Ready信號(hào)表示可以接收數(shù)據(jù)。只有source和destination同時(shí)有效,數(shù)據(jù)才能完成傳輸。 ?

如圖1所示,source有數(shù)據(jù)發(fā)送,在T2周期拉高valid信號(hào)并保持發(fā)送的數(shù)據(jù)。在T4周期,destination拉高ready信號(hào)表示可以接收數(shù)據(jù)。數(shù)據(jù)在T5周期被完整傳輸。這里的valid和ready同時(shí)為1且時(shí)長(zhǎng)1周期的握手,稱為1次Transfer。

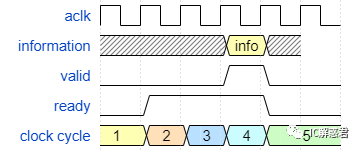

如圖2所示,在T2周期,destination拉高ready信號(hào)表示可以接收數(shù)據(jù),此時(shí)source并沒(méi)有數(shù)據(jù)發(fā)送,直到T4周期source有數(shù)據(jù)發(fā)送便拉高valid信號(hào),在T5周期完成一次數(shù)據(jù)傳輸(Transfer)。

如圖3所示,source和destination同時(shí)在T4周期作用,完成一次數(shù)據(jù)傳輸(Transfer)。

PS?:?source和destination之間沒(méi)有任何關(guān)系。當(dāng)source有數(shù)據(jù)發(fā)送,拉高valid信號(hào);當(dāng)destination可以接受數(shù)據(jù),拉高ready信號(hào)。source和destination根據(jù)自己的情況拉高信號(hào)向?qū)Ψ奖砻饕鈭D。

PS?: 為了避免死鎖產(chǎn)生,需要遵從source不能根據(jù)destination的ready信號(hào)來(lái)操作valid信號(hào),但是ready信號(hào)可以根據(jù)valid信號(hào)來(lái)設(shè)置。舉例來(lái)說(shuō),source和destination可以認(rèn)為是談戀愛(ài)的雙方:

1. source可以主動(dòng)表達(dá)自己心意,destination也可以主動(dòng)表示自己心意,兩者沒(méi)有依賴關(guān)系可以達(dá)到目的。

2. source可以向destination表達(dá)自己心意,destination根據(jù)source表達(dá)過(guò)來(lái)的心意可以回復(fù)source也能達(dá)到目的。

3. 當(dāng)source等待destination主動(dòng)表達(dá)心意,destination也等待source主動(dòng)表達(dá)心意,沒(méi)有人主動(dòng)表達(dá)自己的心意,那么就會(huì)陷入互相等待形成死鎖(事則不成)。

PS?: source有數(shù)據(jù)發(fā)送時(shí),拉高valid信號(hào)。此時(shí)source只有等待destination接受這筆數(shù)據(jù)才可以拉低valid信號(hào)(圖1)(發(fā)數(shù)據(jù)要慎重,一旦發(fā)起必須等到對(duì)方接受才能恢復(fù),即valid:?發(fā)數(shù)據(jù),須慎重,一旦發(fā),必須接,接完后,才能動(dòng))

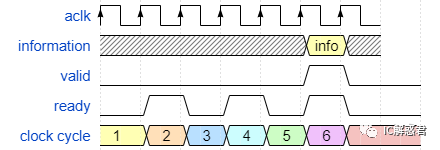

PS?:?destination比較靈活,可以根據(jù)自身情況拉高拉低ready信號(hào)。但是當(dāng)valid為1時(shí),destination拉高ready信號(hào)時(shí),必須接受這筆數(shù)據(jù)才可以拉低ready信號(hào)(ready:?接數(shù)據(jù),隨意動(dòng),源有效,必須接,接完后,才能動(dòng))。如下圖,在T2、T4周期使用ready表示自己可以接收數(shù)據(jù),但在下一周期又認(rèn)為自己接受不了而拉低ready信號(hào)。在T6周期,valid和ready都拉高的時(shí)候,必須接收這筆數(shù)據(jù)才能進(jìn)行下面操作。

?

2.4?AXI Channel Transcation?Timing Overview

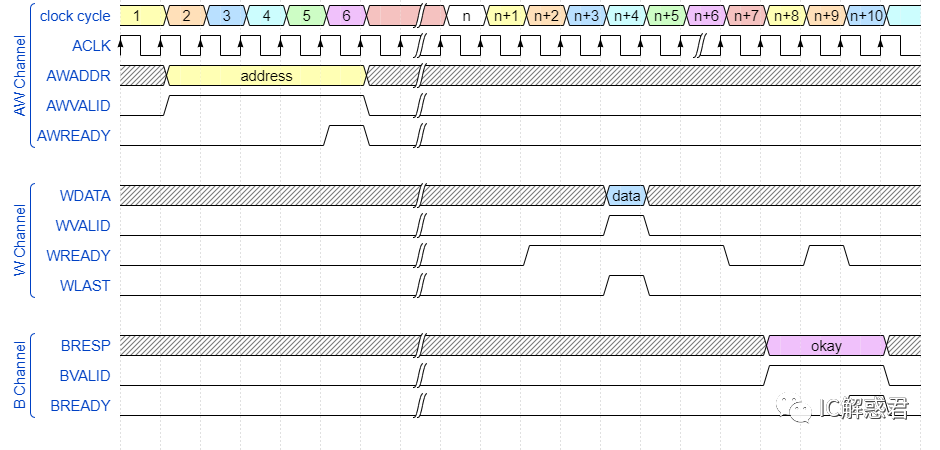

2.41 Write Transcation : single data

寫(xiě)操作時(shí)序圖1:?jiǎn)螖?shù)據(jù)

如上文所示,Manager向Subordinate寫(xiě)數(shù)據(jù)時(shí),Manager先發(fā)送寫(xiě)地址,再發(fā)送寫(xiě)數(shù)據(jù),最后等待Subordinate的響應(yīng)。時(shí)序圖如下:

如上圖所示,每個(gè)通道傳輸?shù)臄?shù)據(jù)不一致,但是都通過(guò)相似的握手信號(hào)來(lái)完成數(shù)據(jù)的交互。從AW通道的地址信號(hào)開(kāi)始,接著W通道的數(shù)據(jù)到最后的B通道的響應(yīng),這一完整的過(guò)程稱為一次Transaction。

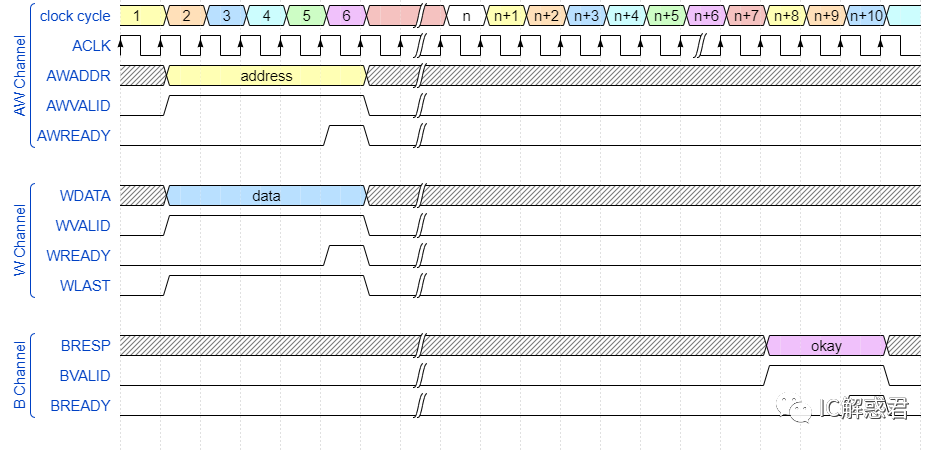

寫(xiě)操作時(shí)序圖2:?jiǎn)螖?shù)據(jù)

如上文所示,Manager向Subordinate寫(xiě)數(shù)據(jù)時(shí),Manager同時(shí)發(fā)送寫(xiě)地址和寫(xiě)數(shù)據(jù),最后等待Subordinate的響應(yīng)。時(shí)序圖如下:

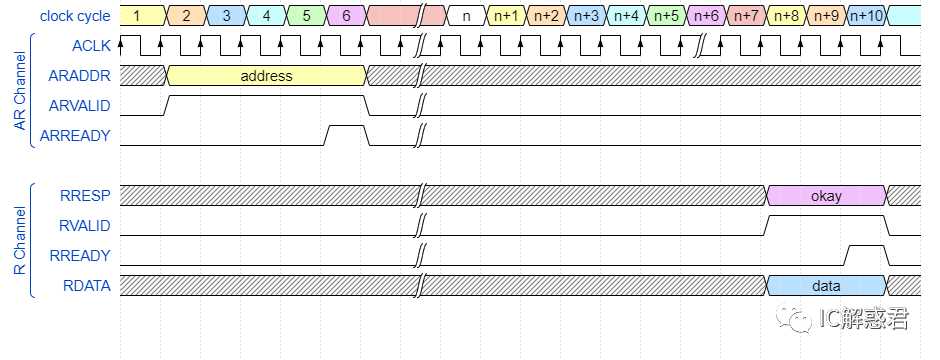

2.42?Read?Transcation : single data

讀操作時(shí)序圖:?jiǎn)螖?shù)據(jù)

如上文所示,Manager向Subordinate讀數(shù)據(jù)時(shí),Manager先發(fā)送讀地址,然后等待Subordinate的響應(yīng)。時(shí)序圖如下:

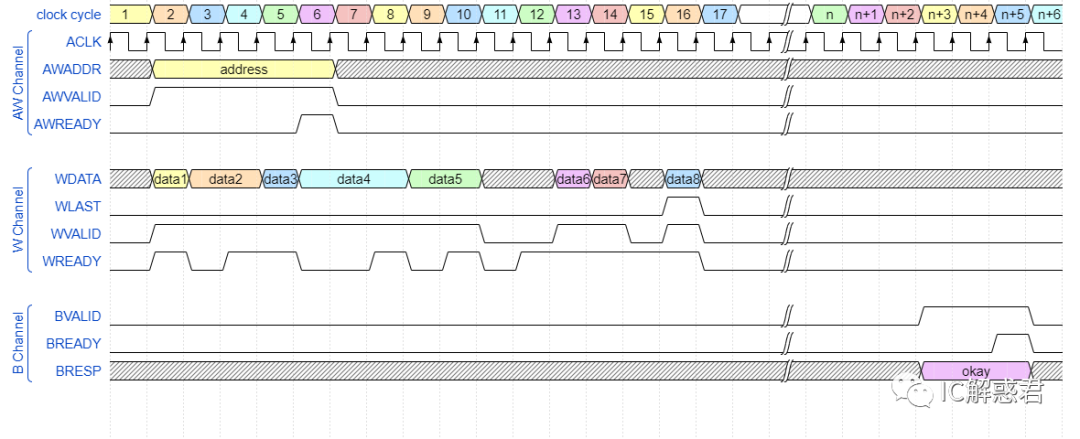

2.43?Write?Transcation : multi?data

寫(xiě)操作時(shí)序:多數(shù)據(jù)

如上文所示,Manager向Subordinate寫(xiě)多個(gè)數(shù)據(jù),Manager發(fā)送寫(xiě)地址和寫(xiě)數(shù)據(jù),等待Subordinate的響應(yīng)。時(shí)序圖如下:

在這里,從第一個(gè)寫(xiě)數(shù)據(jù)到最后一個(gè)寫(xiě)數(shù)據(jù)(data1~data8),在一個(gè)Transaction中,整個(gè)W通道的數(shù)據(jù)過(guò)程稱為一次寫(xiě)B(tài)urst;寫(xiě)B(tài)urst內(nèi)部每一拍的數(shù)據(jù)稱為一個(gè)寫(xiě)B(tài)eat。

?

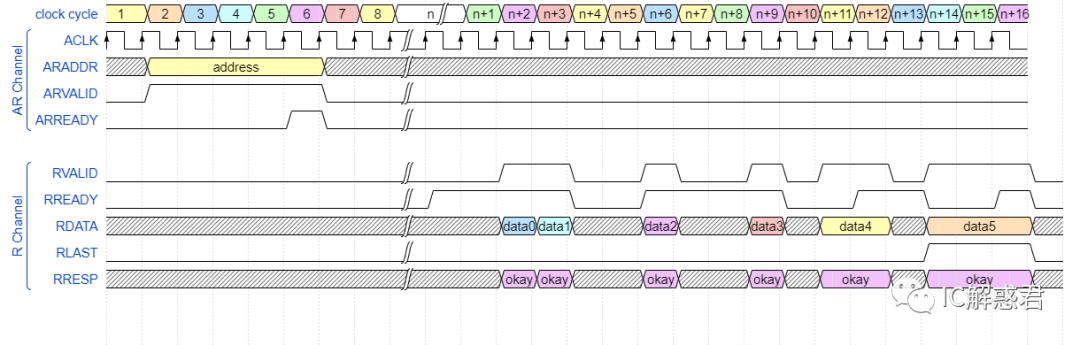

2.44 Read?Transcation : multi?data

讀操作時(shí)序:多數(shù)據(jù)

如上文所示,Manager向Subordinate讀數(shù)據(jù)時(shí),Manager先發(fā)送讀地址,然后等待Subordinate的響應(yīng)。時(shí)序圖如下:

對(duì)比讀操作和寫(xiě)操作的波形可以明顯看出讀寫(xiě)通道的不對(duì)稱。可以看到每一個(gè)讀數(shù)據(jù)都有一個(gè)匹配的讀響應(yīng)伴隨,讀響應(yīng)借助讀數(shù)據(jù)通道返回。而寫(xiě)操作波形圖中,有專門(mén)的通道(B通道)進(jìn)行寫(xiě)操作的響應(yīng)。

寫(xiě)響應(yīng)在寫(xiě)數(shù)據(jù)操作完成之后返回一個(gè)寫(xiě)響應(yīng),而對(duì)讀操作來(lái)說(shuō),伴隨著每個(gè)數(shù)據(jù)都有一個(gè)讀響應(yīng)。這也能體現(xiàn)兩者不對(duì)稱。

在這里,從第一個(gè)讀數(shù)據(jù)到最后一個(gè)讀數(shù)據(jù)(data0~data5),在一個(gè)Transaction中,整個(gè)R通道的數(shù)據(jù)過(guò)程稱為一次讀Burst;讀Burst內(nèi)部每一拍的數(shù)據(jù)稱為一個(gè)讀Beat。

這也就是AMBA spec提到的AXI協(xié)議是基于Burst的傳輸(The AXI protocol is burst-based)。

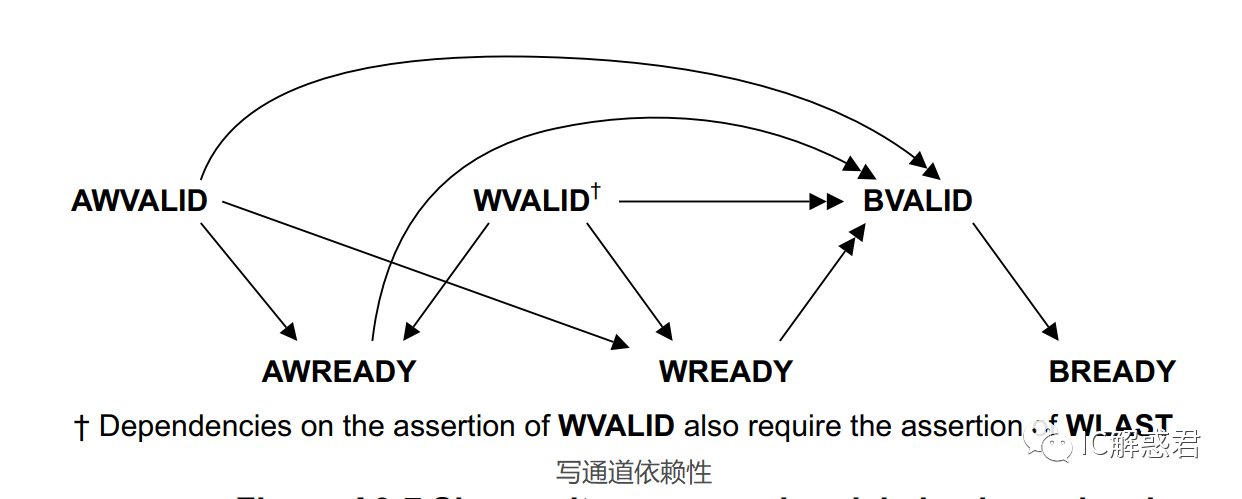

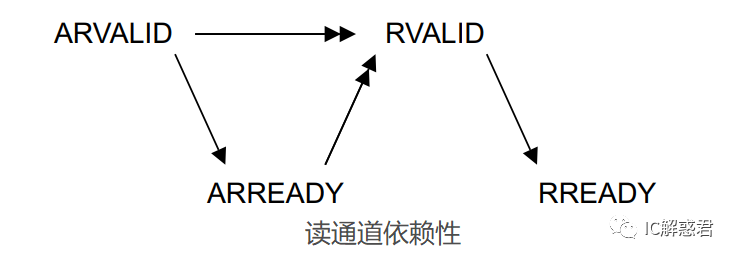

3.?AXI Channel dependencies

雖然這一節(jié)會(huì)提及通道依賴性,但其實(shí)來(lái)說(shuō),通道依賴性已經(jīng)在上文中完整體現(xiàn),即:

1.寫(xiě)通道的依賴性:寫(xiě)操作由地址和數(shù)據(jù)開(kāi)始,到寫(xiě)響應(yīng)完成。這就定義了第一條依賴性:寫(xiě)響應(yīng)要在地址和數(shù)據(jù)之后。

2.讀通道的依賴性:讀操作由讀地址開(kāi)始,到讀數(shù)據(jù)和讀響應(yīng)完成。這就定義了第二條依賴性:讀數(shù)據(jù)和讀響應(yīng)要在讀地址之后。

上面通道依賴性很好理解,只有當(dāng)slave收到命令之后才能給出響應(yīng):對(duì)于寫(xiě)通道的依賴性就是寫(xiě)地址和寫(xiě)數(shù)據(jù)都到達(dá)slave,這時(shí)候slave完成寫(xiě)操作并給出寫(xiě)響應(yīng)。對(duì)于讀通道的依賴性就是讀地址到達(dá)slave后,slave返回讀取的數(shù)據(jù)和讀響應(yīng)。如下AMBA spec原圖所示:

除過(guò)上圖所示的依賴特性,在AXI4協(xié)議里面沒(méi)有規(guī)定其他任何的依賴關(guān)系。

審核編輯:黃飛

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論