賽靈思的 Vivado HLS 工具有助于降低無(wú)線去程網(wǎng)絡(luò)基礎(chǔ)設(shè)施不斷攀升的成本。

無(wú)線網(wǎng)絡(luò)運(yùn)營(yíng)商面臨的巨大挑戰(zhàn)在于維持盈虧底線的同時(shí)要增大網(wǎng)絡(luò)的容量和密度。針對(duì)無(wú)線接口的壓縮方案可減少所需的去程網(wǎng)絡(luò)基礎(chǔ)設(shè)施投資,有助于應(yīng)對(duì)這種挑戰(zhàn)。

我們使用 Vivado ?Design Suite 的高層次綜合 (HLS) 工具來(lái)評(píng)估針對(duì) E-UTRA I/Q 數(shù)據(jù)的開(kāi)放無(wú)線電設(shè)備接口 (ORI) 標(biāo)準(zhǔn)壓縮方案,以估計(jì)其對(duì)信號(hào)保真度的影響、造成的時(shí)延及其實(shí)現(xiàn)成本。我們發(fā)現(xiàn)賽靈思的 Vivado HLS 平臺(tái)能夠高效評(píng)估和實(shí)現(xiàn)所選壓縮算法。

無(wú)線帶寬壓力

無(wú)線帶寬需求的不斷增加催生了對(duì)新的網(wǎng)絡(luò)功能的需求,例如更高階的 MIMO(多輸入多輸出)配置和載波聚合。這樣導(dǎo)致網(wǎng)絡(luò)日趨復(fù)雜,從而要求運(yùn)營(yíng)商做出架構(gòu)調(diào)整,例如進(jìn)行基帶處理集中化以優(yōu)化網(wǎng)絡(luò)資源的使用。 在降低基帶處理成本的同時(shí),基帶處理資源的共享會(huì)增加去程網(wǎng)絡(luò)的復(fù)雜性。

這些去程網(wǎng)絡(luò)負(fù)責(zé)在基帶單元 (BBU) 與遠(yuǎn)程射頻單元 (RRH) 之間傳輸天線載波調(diào)制信號(hào),在光纖上使用通用公共無(wú)線接口 (CPRI) 協(xié)議是這種網(wǎng)絡(luò)最常見(jiàn)的實(shí)現(xiàn)途徑。CPRI 協(xié)議需要恒定的比特率,并且經(jīng)過(guò)多年的發(fā)展,該協(xié)議規(guī)范已提高了最大數(shù)據(jù)速率以滿足不斷增長(zhǎng)的帶寬需求。網(wǎng)絡(luò)運(yùn)營(yíng)商正在尋求合適的技術(shù)以便能夠在顯著提高數(shù)據(jù)速率的同時(shí)不增加所使用的光纖數(shù)量,從而維持蜂窩基站當(dāng)前資本支出與運(yùn)營(yíng)支出不變。

為提供長(zhǎng)期解決方案,網(wǎng)絡(luò)運(yùn)營(yíng)商正在研究可選的網(wǎng)絡(luò)布局,包括重新設(shè)計(jì)基帶處理與射頻單元之間的接口結(jié)構(gòu)以減少去程帶寬。 然而,重新布局網(wǎng)絡(luò)功能可能導(dǎo)致其更難以滿足一些無(wú)線接口規(guī)范的嚴(yán)格性能要求。

減少帶寬的另一種方法是針對(duì)接近或超過(guò)可用吞吐量的無(wú)線接口實(shí)現(xiàn)壓縮/解壓縮 (codec) 方案。可實(shí)現(xiàn)的壓縮率取決于具體的無(wú)線信號(hào)特性,例如噪聲等級(jí)、動(dòng)態(tài)范圍以及過(guò)采樣率等。

讓我們仔細(xì)研究一下針對(duì) E-UTRA IQ 數(shù)據(jù)的 ORI 標(biāo)準(zhǔn)壓縮方案——傳輸調(diào)制符號(hào)的真實(shí)和虛擬組件。圖 1 的簡(jiǎn)化應(yīng)用實(shí)例說(shuō)明了 CPRI IQ 輸入和輸出接口中壓縮和解壓縮模塊的位置在濾波器設(shè)計(jì)過(guò)程中對(duì)特定的通道特性進(jìn)行探索,以最大程度減少因下面下采樣和上采樣引起的信號(hào)丟失。

IQ 壓縮算法

ORI 標(biāo)準(zhǔn)是在 CPRI 規(guī)范的基礎(chǔ)上進(jìn)行了完善和改進(jìn),旨在支持開(kāi)放 BBU/RRH 接口。在最新版本中,ORI 為 10、15 或 20 MHz 的通道帶寬指定了有損時(shí)域 E-UTRA 數(shù)據(jù)壓縮技術(shù)。將固定 3/4 速率重采樣與 15 位 IQ 樣本的非線性量化相結(jié)合,可將帶寬要求降低 50%,例如,有助于通過(guò)單條 9.8 Gbps CPRI 鏈路,實(shí)現(xiàn)覆蓋兩個(gè)分區(qū)的 8 x 8 MIMO 配置。

重采樣階段涉及到對(duì)輸入 I 和 Q 數(shù)據(jù)流進(jìn)行內(nèi)插操作,使內(nèi)插數(shù)據(jù)通過(guò)低通濾波器,并對(duì)輸出數(shù)據(jù)流進(jìn)行抽取操作。在濾波器設(shè)計(jì)過(guò)程中對(duì)特定的通道特性進(jìn)行探索,以最大程度減少因下采樣和上采樣階段引起的信號(hào)丟失。例如,以 30.72 MHz 速率采樣的 20 MHz E-UTRA 下行鏈路通道可輸出 18.015 MHz 的 OFDMA 有效帶寬,這意味著在 3/4 采樣率下可實(shí)現(xiàn)理想的無(wú)損低通濾波器響應(yīng)。

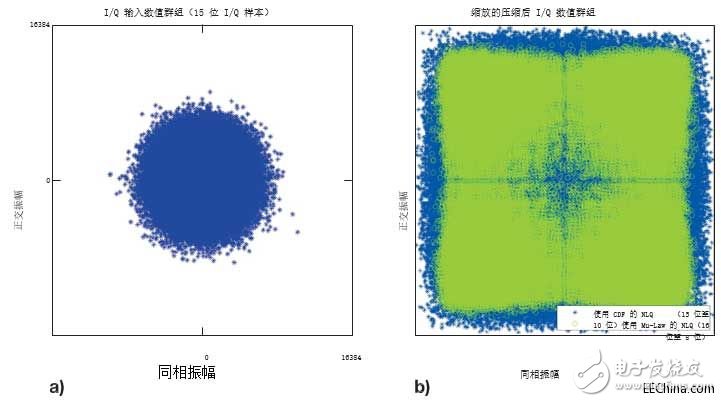

非線性量化 (NLQ) 過(guò)程將正態(tài)分布的 15 位基帶 IQ 樣本轉(zhuǎn)化為 10 位量化值。NLQ 使用具有指定標(biāo)準(zhǔn)偏差的累積分布函數(shù) (CDF) 來(lái)描述精細(xì)粒度下出現(xiàn)頻率比較高(而非出現(xiàn)頻率比較低)的振幅,以將量化誤差減至最小。如圖 2b 中的結(jié)果所示,量化后數(shù)值群組對(duì)減小后數(shù)值范圍的填充比例明顯高于圖 2a 所示的輸入數(shù)值群組,因此,與其他線性量化方案相比,量化后數(shù)值群組可將量化誤差減至最小。通常,I 與 Q 樣本實(shí)現(xiàn)在查找表中,它們利用其對(duì)應(yīng)的分布函數(shù)單獨(dú)進(jìn)行量化。我們將 ORI IQ 壓縮性能與 ITU-T Recommendation G.711 指定的 Mu-Law 壓縮算法實(shí)現(xiàn)方案進(jìn)行對(duì)比。同屬于非線性量化技術(shù),Mu-Law 利用對(duì)數(shù)函數(shù)在可用數(shù)值范圍內(nèi)對(duì)量化值進(jìn)行重新分布。不同于考慮輸入樣本統(tǒng)計(jì)分布的 CDF 量化法,通過(guò) Mu-Law 量化的輸出與對(duì)應(yīng)輸入樣本值和指定壓縮值成函數(shù)關(guān)系。

為了比較 50% 的等效壓縮比,我們考慮 16 位至 8 位 Mu-Law 編碼器。由于不需要重采樣,因此從時(shí)延和實(shí)現(xiàn)資源成本方面考慮,Mu-Law 壓縮是一款低成本解決方案,能夠在設(shè)計(jì)復(fù)雜性與可實(shí)現(xiàn)的重建信號(hào)保真度之間進(jìn)行權(quán)衡。

采用 CPRI IQ 壓縮技術(shù)的簡(jiǎn)化無(wú)線系統(tǒng)

圖 1 — 采用 CPRI IQ 壓縮技術(shù)的簡(jiǎn)化無(wú)線系統(tǒng)

20 MHz E-UTRA DL 通道參考輸入幀的 IQ 數(shù)值群組 (a),以及壓縮后 IQ 數(shù)據(jù) (b) 經(jīng)擴(kuò)展用以說(shuō)明每個(gè)數(shù)值群組 。..

圖 2–20 MHz E-UTRA DL 通道參考輸入幀的 IQ 數(shù)值群組 (a),以及壓縮后 IQ 數(shù)據(jù) (b) 經(jīng)擴(kuò)展用以說(shuō)明每個(gè)數(shù)值群組的有效數(shù)值范圍使用情況

向上擴(kuò)展編解碼架構(gòu)

對(duì)于原型配置,我們計(jì)劃將壓縮算法向上擴(kuò)展,以充分利用 9.8304 Gbps CPRI 鏈路(線路比特率選項(xiàng) 7)。ORI 壓縮 E-UTRA 樣本規(guī)范允許我們通過(guò)單個(gè) 9.8G CPRI 鏈路傳輸 16 條壓縮 IQ 通道(32 條 I 與 Q 通道單獨(dú)壓縮)。目標(biāo)吞吐量為每個(gè) CPRI 時(shí)鐘輸出三個(gè)壓縮樣本,這已足夠完全打包 32 位賽靈思 LogiCORE? IP CPRI IQ 接口,提供所需的 737.28 Msps 的壓縮 IP 輸出。

以單個(gè)時(shí)鐘域?yàn)槟繕?biāo),我們需要構(gòu)建重采樣濾波器以滿足每個(gè)時(shí)鐘周期三個(gè)樣本的輸出速率。用 0 的補(bǔ)碼對(duì)輸入樣本流進(jìn)行內(nèi)插計(jì)算允許我們忽略無(wú)用的輸入樣本。輸出流變?yōu)樽訛V波器內(nèi)插速率的函數(shù),每個(gè)子濾波器都使用 FIR 系數(shù)子集(系數(shù) / 插值速率的總數(shù))。共四個(gè)并行濾波器,每個(gè)都在一個(gè)通道子集上運(yùn)行,使得整體吞吐量相當(dāng)于每個(gè)時(shí)鐘周期要求 3 個(gè)壓縮樣本。除高吞吐量以外,所建議的架構(gòu)還能縮短重采樣時(shí)延,因?yàn)槊總€(gè)子濾波器中僅使用一小部分系數(shù)。

對(duì)于壓縮路徑,我們使用累積分布函數(shù) (CDF) 計(jì)算 NLQ 量化表。假設(shè) IQ 分布是對(duì)稱的,我們將 NLQ 查找表的大小縮減至 214 條 9 位量化值。由于我們的設(shè)計(jì)需要每時(shí)鐘周期三個(gè)并行查找表,因此我們利用相同量化值實(shí)現(xiàn)三個(gè)并行查找表。可以

使用預(yù)期或觀察的標(biāo)準(zhǔn)偏差值為 I 和 Q 樣本單獨(dú)計(jì)算量化等級(jí)。 或者,以實(shí)際的信號(hào)級(jí)測(cè)量值或更高層次的網(wǎng)絡(luò)參數(shù)為依據(jù),單獨(dú)量化通道子集。解壓縮時(shí),我們使用分位函數(shù)(逆向 CDF)來(lái)計(jì)算逆向 NLQ 表。表的大小被限定在 29 個(gè) 14 位數(shù)值。

我們使用由 MATLAB? LTE 系統(tǒng)工具箱生成的 20 MHz LTE E-UTRA FDD 通道激勵(lì)來(lái)測(cè)試已實(shí)現(xiàn)的編解碼算法。然后,我們使用 Keysight VSA 來(lái)解調(diào)捕捉到的 IQ 數(shù)據(jù),并通過(guò)測(cè)量輸出波形誤差矢量幅度 (EVM) 以量化壓縮和解壓縮階段引起的信號(hào)失真。我們將已公布的輸出 EVM 測(cè)量值(體現(xiàn)理想信號(hào)與測(cè)量信號(hào)的差異)與參考輸入信號(hào) EVM 進(jìn)行比較。

高級(jí)建模與實(shí)現(xiàn)流程

我們使用GNU Octave 語(yǔ)言,并利用其信號(hào)處理和統(tǒng)計(jì)程序包開(kāi)發(fā)單通道壓縮及解壓縮模型,啟動(dòng)實(shí)現(xiàn)過(guò)程。除提供有用的驗(yàn)證參考數(shù)據(jù)點(diǎn)以外,模型輸出還生成了一組 FIR 濾波器系數(shù)和量化表。

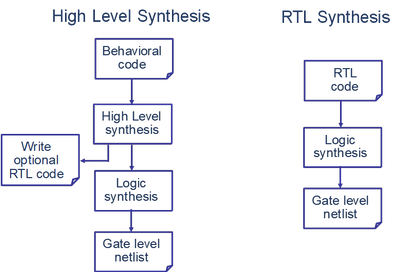

Vivado HLS 工具從高級(jí)數(shù)學(xué)模型中提供明顯的傳輸路徑,從潛在的硬件性能和成本方面評(píng)估提議的架構(gòu)。我們建立了 C++ 測(cè)試臺(tái),以利用壓縮和解壓縮函數(shù)對(duì)輸入數(shù)據(jù)流進(jìn)行運(yùn)算。由于我們會(huì)將這些函數(shù)置于 CPRI 鏈路的相對(duì)端,因此便單獨(dú)對(duì)其進(jìn)行綜合。利用 HLS 流及簡(jiǎn)單 C++ 循環(huán)管理下的交錯(cuò)通道數(shù)據(jù)流,我們實(shí)現(xiàn)了所有內(nèi)、外部函數(shù)接口。

IQ 編解碼架構(gòu)所示為(僅下行鏈路中)編解碼器 IP 接口處的樣本處理速率

圖 3–IQ 編解碼架構(gòu)所示為(僅下行鏈路中)編解碼器 IP 接口處的樣本處理速率

我們利用 Vivado HLS FIR IP 來(lái)開(kāi)發(fā)重采樣濾波器的原型設(shè)計(jì)。為滿足設(shè)計(jì)的高吞吐量要求,我們實(shí)現(xiàn)并行單速率 FIR 濾波器,并采用基于循環(huán)的濾波器輸出抽取功能。

通過(guò)實(shí)現(xiàn)多相重采樣濾波器,可獲得更高效的資源節(jié)約型重采樣濾波器。多通道分級(jí)采樣速率轉(zhuǎn)換濾波器就是一種支持 ORI 重采樣速率的開(kāi)箱即用型選擇;賽靈思應(yīng)用指南 XAPP1236 “使用 Vivado 高層次綜合以實(shí)現(xiàn)多通道分級(jí)采樣速率轉(zhuǎn)換濾波器設(shè)計(jì)。”對(duì)該濾波器進(jìn)行了介紹。

當(dāng)驗(yàn)證數(shù)據(jù)集較大時(shí),快速 C 級(jí)仿真的優(yōu)勢(shì)就變得愈發(fā)明顯。對(duì) IQ 壓縮算法進(jìn)行評(píng)估時(shí)最能體現(xiàn)這一點(diǎn),因?yàn)椋辽傩枰型暾臒o(wú)線電數(shù)據(jù)幀(307,200 個(gè) IQ 樣本 / 通道),才能利用 VSA 工具進(jìn)行 EVM 測(cè)量。我們發(fā)現(xiàn),C 仿真與 C/RTL 協(xié)同仿真相比,仿真速度可提升兩個(gè)數(shù)量級(jí);對(duì)于本壓縮 IP 測(cè)試而言,相比于協(xié)同仿真運(yùn)行時(shí)間的 9 小時(shí),C 仿真僅需 5 分鐘。

HLS 測(cè)試臺(tái)還具備另一個(gè)重要優(yōu)勢(shì),即利用文件和 HLS 流可方便地使用輸入數(shù)據(jù)和捕捉輸出數(shù)據(jù)。結(jié)果是可提供一個(gè)接口以利用 VSA 工具進(jìn)行數(shù)據(jù)分析,或者在 C++ 測(cè)試臺(tái)中直接與 Octave 模型輸出進(jìn)行比較。

性能測(cè)量

Keysight VSA 測(cè)量結(jié)果顯示,具有 144 個(gè) FIR 系數(shù)的編解碼器配置具備 0.29% 的平均 EVM。與 EVM RMS 為 0.18% 的初始輸入數(shù)據(jù)相比,因壓縮-解壓縮處理鏈而多出的 EVM 部分為 0.23%。相比之下,同等輸入數(shù)據(jù)集下 Mu-Law 壓縮算法實(shí)現(xiàn)的平均 EVM 為 1.07%。

根據(jù) Mu-Law 壓縮法所減少的時(shí)延和資源使用成本來(lái)看,當(dāng)可以將整個(gè) LTE 下行信號(hào)處理鏈的 8% EVM 預(yù)算中的 1% 分配給 IQ 壓縮時(shí),Mu-Law 壓縮就會(huì)優(yōu)于 ORI IQ 壓縮方案。然而,任何附加信號(hào)失真都意味著要為剩余系統(tǒng)組件設(shè)定更嚴(yán)格的性能目標(biāo)。數(shù)字前端器件及功率放大器等組件的成本增加可能會(huì)抵消潛在的 IQ 壓縮成本優(yōu)勢(shì)。

Vivado 高層次綜合依據(jù)啟動(dòng)間距確認(rèn)了所需吞吐量——頂層任務(wù)準(zhǔn)備好接受新輸入數(shù)據(jù)之前的時(shí)鐘周期數(shù)量。同時(shí),經(jīng)過(guò)我們的驗(yàn)證,導(dǎo)出的 Vivado IP Integrator 內(nèi)核滿足目標(biāo) Kintex? UltraScale? 平臺(tái)的時(shí)序要求。

我們將研究范圍限定在少量的配置和輸入數(shù)據(jù)向量。然而,一旦系統(tǒng)模型和對(duì)應(yīng)的 C 語(yǔ)言模型就位,即可在幾分鐘內(nèi)自定義、實(shí)現(xiàn)與評(píng)估備選配置。

設(shè)計(jì)備選方案

從設(shè)計(jì)工具角度來(lái)說(shuō),Vivado HLS 提供一個(gè)可行的硬件原型設(shè)計(jì)路徑。高級(jí)測(cè)試平臺(tái)很適合需要在多種設(shè)計(jì)與驗(yàn)證工具間傳輸數(shù)據(jù)流的設(shè)計(jì)框架。這種測(cè)試平臺(tái)的主要優(yōu)勢(shì)在于能夠?qū)τ布到y(tǒng)模型快速執(zhí)行 C 語(yǔ)言仿真。對(duì)于 IQ 壓縮及類似應(yīng)用而言,仿真運(yùn)行時(shí)涉及頻繁的高級(jí)參數(shù)或輸入數(shù)據(jù)集變化,使得快速反饋成為重要因素。

測(cè)量結(jié)果顯示,所建議的 ORI 壓縮方案可為 20 MHz E-UTRA 下行鏈路通道實(shí)現(xiàn)低于 0.25% 的信號(hào)失真。盡管壓縮性能取決于輸入通道特性,ORI 壓縮方案仍可選擇最佳的濾波器設(shè)計(jì)與量化器參數(shù)組合,以提供性能調(diào)節(jié)范圍。

我們?cè)驮O(shè)計(jì)針對(duì)所有 16 個(gè)天線載波數(shù)據(jù)流使用通用的靜態(tài)設(shè)計(jì)參數(shù)集。真實(shí)系統(tǒng)中,信號(hào)特性可以是事先知道的,或者是可以測(cè)量并用來(lái)調(diào)節(jié)設(shè)計(jì)的。或者,可通過(guò)重新配置量化表來(lái)動(dòng)態(tài)調(diào)節(jié)壓縮性能,以維持所要求的最低信號(hào)保真度。

除壓縮性能外,還要考慮執(zhí)行壓縮和解壓縮所需的實(shí)現(xiàn)資源和附加時(shí)延引起的成本。重采樣濾波器尺寸與時(shí)延占總編解碼器成本的主體;更大的 EVM 容差應(yīng)考慮到具有較少濾波器系數(shù)的設(shè)計(jì)。

考慮到產(chǎn)品上市時(shí)間因素,賽靈思創(chuàng)建了基于 ORI 的 IQ 編解碼器概念驗(yàn)證。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論