完善資料讓更多小伙伴認識你,還能領(lǐng)取20積分哦,立即完善>

標簽 > 賽靈思

提供賽靈思公司最新的技術(shù)和產(chǎn)品信息,工程師最喜歡的賽靈思技術(shù)社區(qū)

文章:1699個 瀏覽:132178次 帖子:56個

了解系統(tǒng)監(jiān)控儀System Monitor的各種功能

了解System Monitor的各種功能以及如何利用它來在各種應(yīng)用程序/市場中增加重要價值。

如何運行UltraScale PCI Express解決方案的四個主要數(shù)據(jù)接口

了解UltraScale PCI Express解決方案的四個主要數(shù)據(jù)接口如何運行。 具有四個獨立的數(shù)據(jù)接口簡化了用戶設(shè)計并提高了整體PCI Expr...

2018-11-29 標簽:數(shù)據(jù)賽靈思pci 3842 0

全新的軟件定義規(guī)范環(huán)境如何實現(xiàn)“軟”定義網(wǎng)絡(luò)

本視頻由賽靈思公司副總裁Nick Possley向您介紹全新的軟件定義規(guī)范環(huán)境如何實現(xiàn)“軟”定義網(wǎng)絡(luò)('Softly'定義網(wǎng)絡(luò),SDNet),以及該技術(shù)...

2018-11-29 標簽:賽靈思軟件網(wǎng)絡(luò) 2380 0

了解UltraScale DSP架構(gòu)如何降低設(shè)計功耗

了解UltraScale DSP架構(gòu)及其如何幫助降低設(shè)計功耗,以及UltraScale時鐘架構(gòu)中的省電功能。 您還將學(xué)習(xí)估算DSP和時鐘的功率......

采用XilinxVirtex-7 FPGA的12.5Gb/s HMC接口演示

觀看業(yè)界首款采用XilinxVirtex?-7 FPGA的12.5 Gb / s混合存儲器立方體(HMC)接口演示。

如何使用Vivado功能創(chuàng)建AXI外設(shè)

了解如何使用Vivado的創(chuàng)建和封裝IP功能創(chuàng)建可添加自定義邏輯的AXI外設(shè),以創(chuàng)建自定義IP。

如何使用Xilinx SDK啟動電路板及利用Zynq DRAM進行測試

在本視頻中,我們將學(xué)習(xí)如何使用Xilinx SDK啟動電路板,利用每個驅(qū)動程序提供的應(yīng)用示例并測試各種外設(shè)。 我們將詳細介紹Zynq DRAM測試,并...

Xilinx的Dave Tokic和ADI公司的Gerd Melder討論了如何協(xié)同工作使他們能夠?qū)崿F(xiàn)前進,并在軟件定義無線電等應(yīng)用中為客戶提供快速,有...

用于Zynq微處理器和可編程邏輯的新型操作系統(tǒng)Dyplo介紹

Xilinx的Dave Tokic與Topic Embedded Systems的創(chuàng)始人兼首席執(zhí)行官Rieny Rijnen進行了交談,他描述了Dypl...

2018-11-30 標簽:賽靈思操作系統(tǒng)微處理器 2884 0

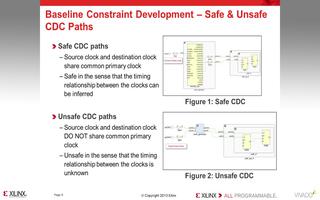

用于定時關(guān)閉的UltraFast Vivado設(shè)計方法

本培訓(xùn)中概述的方法將使您能夠?qū)崿F(xiàn)時序收斂的“簽核”質(zhì)量XDC約束。 無論復(fù)雜程度如何,這種方法還可以使您更快地實現(xiàn)時序收斂......

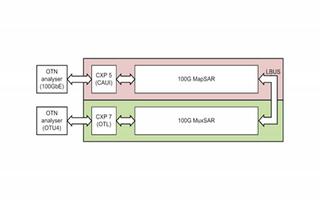

Xilinx的2x100G MuxMapSAR參考設(shè)計

了解Xilinx的2x100G MuxMapSAR參考設(shè)計,該設(shè)計在VC730 OTN測試開發(fā)平臺上運行。 (簡明版)

2018-11-29 標簽:賽靈思操作系統(tǒng)應(yīng)用程序 2063 0

如何使用Vivado中的Synopsys VCS仿真器進行仿真

了解如何使用Vivado中的Synopsys VCS仿真器使用MicrBlaze IPI設(shè)計運行仿真。 我們將演示如何編譯仿真庫,為IP或整個項目生成...

如何使用Synopsys VCS仿真器進行ZYNQ BFM IPI設(shè)計仿真

了解如何使用Vivado中的Synopsys VCS仿真器使用ZYNQ BFM IPI設(shè)計運行仿真。 我們將演示如何編譯仿真庫,為IP或整個項目生成仿...

UltraScale如何支持下一代Ultra系統(tǒng)

了解UltraScale如何支持下一代Ultra系統(tǒng)。

2019-01-08 標簽:視頻賽靈思ultrascale 2829 0

Kintex UltraScale器件的16.3 Gbps背板性能演示

本視頻向您展示了Kintex UltraScale器件的業(yè)界首個16.3 Gbps背板性能演示。

Xilinx高級副總裁Victor Peng討論了業(yè)界首個All Programmable ASIC級架構(gòu)背后的戰(zhàn)略。

Xilinx DDR4控制器和接口的速度運行是2400 Mb/s

在安捷倫最新的測試解決方案之一Infinium 90000X系列示波器上驗證,UltraScale FPGA上運行的2400 Mb / s DDR4內(nèi)存...

All Programmable架構(gòu)中應(yīng)用最先進的ASIC架構(gòu)優(yōu)化

推出ASIC級全可編程架構(gòu)

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |