完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > 賽靈思

提供賽靈思公司最新的技術(shù)和產(chǎn)品信息,工程師最喜歡的賽靈思技術(shù)社區(qū)

文章:1699個(gè) 瀏覽:132177次 帖子:56個(gè)

如何快速把握機(jī)器視覺的市場(chǎng)機(jī)會(huì)

網(wǎng)絡(luò)研討會(huì)將重點(diǎn)介紹Xilinx及其合作伙伴的IP核豐富套件如何通過生態(tài)系統(tǒng)使用戶能夠快速,輕松地把握在機(jī)器視覺市場(chǎng)的機(jī)會(huì)。

EC2 F1實(shí)例的設(shè)計(jì)流程與SDAccel優(yōu)勢(shì)的介紹

觀看此視頻,了解EC2 F1實(shí)例的開發(fā)人員設(shè)計(jì)流程概述。 了解SDAccel的優(yōu)勢(shì),包括標(biāo)準(zhǔn)OpenCL API及其與優(yōu)化RTL內(nèi)核的兼容性。

2018-11-21 標(biāo)簽:賽靈思api設(shè)計(jì) 2263 0

UltraFAST設(shè)計(jì)方法培訓(xùn)將幫助您時(shí)序收斂階段實(shí)現(xiàn)“Sign-off” 質(zhì)量XDC約束。另外,還幫助您顯著提高時(shí)序收斂實(shí)現(xiàn)效率,無論該設(shè)計(jì)有多么復(fù)雜。

Vivado:行業(yè)首款 SoC 增強(qiáng)型設(shè)計(jì)套件最新消息

交互式時(shí)鐘域的交叉分析:該功能支持設(shè)計(jì)人員在設(shè)計(jì)早期階段調(diào)試CDC問題。結(jié)合Vivado設(shè)計(jì)套件的交互式時(shí)序分析和交叉探測(cè)特性,CDC分析功能可提供強(qiáng)大...

2019-08-01 標(biāo)簽:賽靈思仿真器系統(tǒng)級(jí) 2255 0

基于 Zynq All Programmable SoC 的電機(jī)控制器

在本次網(wǎng)絡(luò)研討會(huì)中,Mathworks 的工程師會(huì)談到 SoC (片上系統(tǒng)) 的 軟硬件聯(lián)合設(shè)計(jì) 挑戰(zhàn),并為大家介紹如何采用 基于模型的設(shè)計(jì)方法 進(jìn)行 ...

UltraScale+器件設(shè)計(jì)的科學(xué)成果分享

加入Xilinx技術(shù)營銷工程師Eric Crabill,他分享了我們商用UltraScale +器件設(shè)計(jì)中應(yīng)用的科學(xué)成果,該器件具有出色的可靠性,可用性...

2018-11-21 標(biāo)簽:賽靈思設(shè)計(jì)器件 2246 0

此演示展示了Xilinx的400GE解決方案,該解決方案采用Xilinx Virtex UltraScale VU190器件,預(yù)先標(biāo)準(zhǔn)的400GE MA...

QDMA的驅(qū)動(dòng)在進(jìn)行版本升級(jí)時(shí),可能會(huì)對(duì)部分寄存器的數(shù)值進(jìn)行變更,用戶如果要進(jìn)行升級(jí),推薦升級(jí)到最新的Vivado和驅(qū)動(dòng)版本。如果驅(qū)動(dòng)和Vivado之間...

賽靈思對(duì)于HLS 設(shè)計(jì)流程-基本概念

Xilinx 戰(zhàn)略應(yīng)用高級(jí)工程師。專注于 C/C++ 高層次綜合,擁有多年利用 Xilinx FPGA 實(shí)現(xiàn)數(shù)字信號(hào)處理算法的經(jīng)驗(yàn),對(duì) Xilinx F...

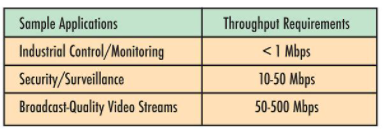

賽靈思嵌入式網(wǎng)絡(luò)解決方案的應(yīng)用研究

大多數(shù)嵌入式產(chǎn)品都需要某種形式的網(wǎng)絡(luò)或通信接口。以太網(wǎng)由于(Ethernet)成本低、幾乎無處不在,且可以利用TCP/IP等因特網(wǎng)協(xié)議連接因特網(wǎng),成為目...

批命令 A、開始-運(yùn)行:cmd 在DOS窗口輸入:“ compxlib –s mti_se –f all –l all –o c:\Modeltech ...

Kintex UltraScale器件的16.3 Gbps背板性能演示

本視頻向您展示了Kintex UltraScale器件的業(yè)界首個(gè)16.3 Gbps背板性能演示。

FPGA為復(fù)雜的算法提供計(jì)算效率的優(yōu)勢(shì)并且功耗低

在本次研討會(huì)當(dāng)中,賽靈思將要向您展示一種全新的方法,該方法可以使對(duì)硬件設(shè)計(jì)不太熟悉的設(shè)計(jì)者輕松而方便地釋放 FPGA 硬件加速的優(yōu)勢(shì),比如利用經(jīng)過硬件調(diào)...

關(guān)于CNN的當(dāng)前技術(shù)最新發(fā)展水平以及包括清華大學(xué)等在內(nèi)的研究結(jié)果

繼續(xù)使用定點(diǎn)算法 — 16 位定點(diǎn)解析可最大限度減少與 32 位定浮點(diǎn)計(jì)算有關(guān)的精確度退化問題,而且如果逐層使用動(dòng)態(tài)量化,8 位計(jì)算也能產(chǎn)生良好的結(jié)果。

米蘭理工大學(xué)NECSTLab的研究探索了如何提高個(gè)性化醫(yī)療系統(tǒng)的性能。

2019-01-09 標(biāo)簽:賽靈思 2169 0

Amazon EC2 F1實(shí)例上的機(jī)器學(xué)習(xí)演示

Amazon EC2 F1實(shí)例上的機(jī)器學(xué)習(xí)演示展示了超過10,000張圖像/秒。 這說明了與x86解決方案相比,F(xiàn)PGA池如何產(chǎn)生高性能,低功耗的解決方案。

2018-11-26 標(biāo)簽:fpga賽靈思機(jī)器學(xué)習(xí) 2162 0

使用Spartan-6 FPGA視頻平臺(tái)加速DTV設(shè)計(jì)中視頻算法的開發(fā)

使用Spartan-6 FPGA消費(fèi)類視頻套件加速DTV設(shè)計(jì)中高級(jí)視頻算法的開發(fā)。 與消費(fèi)者部門主管Harry Raftopoulos近距離觀看套件。

Xilinx教育生態(tài)系統(tǒng)是公私合作伙伴關(guān)系的一個(gè)明確的綜合模型,創(chuàng)建了一條管道,全面支持學(xué)生,同時(shí)加強(qiáng)他們?cè)诳茖W(xué),技術(shù),工程,藝術(shù)和數(shù)學(xué)方面的教育

了解如何為UltraScale +設(shè)計(jì)添加額外的安全級(jí)別。 該視頻演示了如何防止差分功耗分析(DPA),以在比特流配置之上增加額外的安全性。

2018-11-26 標(biāo)簽:賽靈思功耗設(shè)計(jì) 2134 0

了解如何為UltraScale +設(shè)計(jì)添加額外的安全級(jí)別。 該視頻演示了如何防止差分功耗分析(DPA),以在比特流配置之上增加額外的安全性。

2018-11-27 標(biāo)簽:賽靈思功耗設(shè)計(jì) 2122 0

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |