完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > rtl

RTL在電子科學(xué)中指的是寄存器轉(zhuǎn)換級(jí)電路(Register Transfer Level)的縮寫(xiě),也叫暫存器轉(zhuǎn)移層次。

文章:352個(gè) 瀏覽:60812次 帖子:96個(gè)

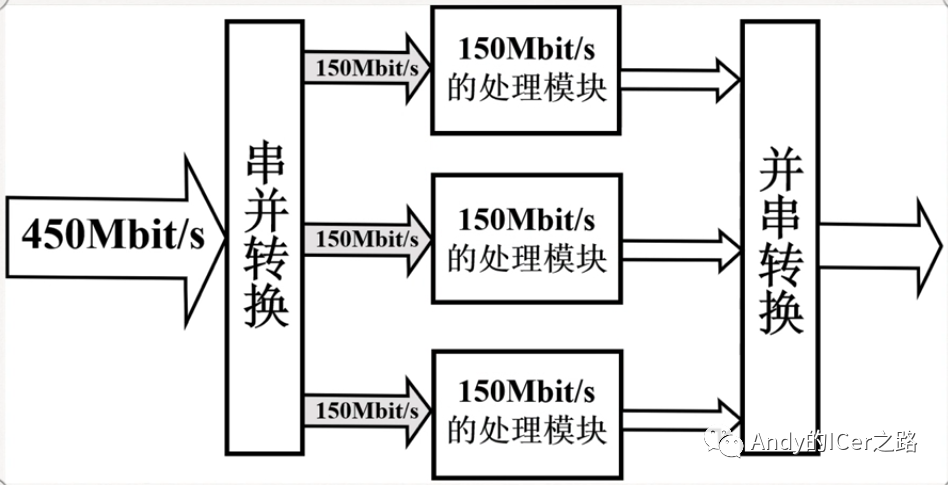

RTL設(shè)計(jì)指導(dǎo)原則之面積和速度互換

一般來(lái)說(shuō),面積是一個(gè)設(shè)計(jì)所消耗的目標(biāo)器件的硬件資源數(shù)量或者ASIC芯片的面積。

2023-06-05 標(biāo)簽:FPGA設(shè)計(jì)加法器RTL 1806 0

在verilog中雖然沒(méi)有system verilog的assertion,但是我們依舊可以使用display打印檢查各類錯(cuò)誤,在RTL級(jí)的仿真中能夠快...

2023-08-27 標(biāo)簽:芯片設(shè)計(jì)仿真器RTL 1752 0

把一個(gè)算法用RTL實(shí)現(xiàn),有哪些比較科學(xué)的步驟?

通常來(lái)講,我們做算法實(shí)現(xiàn),需要有對(duì)標(biāo)的算法模型,作為驗(yàn)證硬件邏輯設(shè)計(jì)是否正確的參考依據(jù)。

利用FPGA工具設(shè)置優(yōu)化FPGA HLS設(shè)計(jì)

高層次的設(shè)計(jì)可以讓設(shè)計(jì)以更簡(jiǎn)潔的方法捕捉,從而讓錯(cuò)誤更少,調(diào)試更輕松。然而,這種方法最受詬病的是對(duì)性能的犧牲。在復(fù)雜的 FPGA 設(shè)計(jì)上實(shí)現(xiàn)高性能,往往...

我們?cè)撊绾螒?yīng)對(duì)SOC中越來(lái)越龐大和復(fù)雜的SDC約束?

SOC設(shè)計(jì)變得越來(lái)越復(fù)雜,成本越來(lái)越高,設(shè)計(jì)和驗(yàn)證也越來(lái)越困難。

2024-03-13 標(biāo)簽:EDA工具SoC設(shè)計(jì)信號(hào)完整性 1730 0

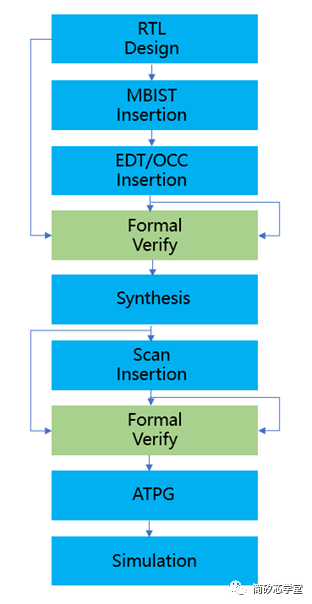

Formal Verify,即形式驗(yàn)證,主要思想是通過(guò)使用數(shù)學(xué)證明的方式來(lái)驗(yàn)證一個(gè)修改后的設(shè)計(jì)和它原始的設(shè)計(jì),在功能上是否等價(jià)。

如何用KrakenSDR制作被動(dòng)雷達(dá)呢?

提起與無(wú)線電有關(guān)的項(xiàng)目,我在紐約的家的確是個(gè)糟糕的實(shí)驗(yàn)地點(diǎn)。如果我們可以看到和聽(tīng)到無(wú)線電波,那么電子舞曲(EDM)狂歡派對(duì)會(huì)像一個(gè)剝奪感官的牢籠。

經(jīng)過(guò)幾周的更新,SV核心部分用戶自定義類型和包內(nèi)容已更新完畢,接下來(lái)就是RTL表達(dá)式和運(yùn)算符。

用于解碼器IP設(shè)計(jì)和合規(guī)性驗(yàn)證的比特流和軟件工具鏈DVK

DVK是用于解碼器IP設(shè)計(jì)和合規(guī)性驗(yàn)證的比特流和軟件工具鏈。它是芯片RTL設(shè)計(jì)、目標(biāo)設(shè)備集成(如智能手機(jī)、智能電視、機(jī)頂盒)、發(fā)貨給客戶前的軟件堆棧驗(yàn)證...

關(guān)于數(shù)字硬件建模SystemVerilog

經(jīng)過(guò)幾周的更新,SV核心部分用戶自定義類型和包內(nèi)容已更新完畢,接下來(lái)就是RTL表達(dá)式和運(yùn)算符。

SoC設(shè)計(jì)的IO PAD怎么移植到FPGA原型驗(yàn)證

FPGA原型驗(yàn)證系統(tǒng)要盡可能多的復(fù)用SoC相關(guān)的模塊,這樣才是復(fù)刻SoC原型的意義所在。

2023-04-19 標(biāo)簽:fpgaasicSoC設(shè)計(jì) 1640 0

決策語(yǔ)句(Decision statements)允許程序塊的執(zhí)行流程根據(jù)設(shè)計(jì)中信號(hào)的當(dāng)前值分支到特定語(yǔ)句。SystemVerilog有兩個(gè)主要的決策語(yǔ)...

RTL建模中廣泛使用的運(yùn)算符是條件運(yùn)算符,也稱為三元運(yùn)算符,該運(yùn)算符用于在兩個(gè)表達(dá)式之間進(jìn)行選擇——表5-2列出了用于表示條件運(yùn)算符的重點(diǎn)。

談?wù)剮追N芯片設(shè)計(jì)增加代碼復(fù)用性的方法

很多芯片在設(shè)計(jì)之初,就已經(jīng)考慮如何增加代碼的復(fù)用性,盡量減少工作量,降低錯(cuò)誤概率。

2023-09-12 標(biāo)簽:fpga加速器芯片設(shè)計(jì) 1633 0

相信不少人都聽(tīng)過(guò)verilog這個(gè)詞,今天我就想講一講我所理解的verilog是什么。

2023-12-04 標(biāo)簽:寄存器芯片設(shè)計(jì)Verilog 1632 0

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無(wú)刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺(jué) | 無(wú)人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹(shù)莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |