完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > Vitis

Vitis Model Composer 是一款 Xilinx 工具包,支持在 MATALB? 和 Simulink? 環(huán)境中進(jìn)行快速設(shè)計(jì)探索和驗(yàn)證,并加速 Xilinx 器件的量產(chǎn)。

Vitis Model Composer 是一款 Xilinx 工具包,支持在 MATALB? 和 Simulink? 環(huán)境中進(jìn)行快速設(shè)計(jì)探索和驗(yàn)證,并加速 Xilinx 器件的量產(chǎn)。

使用針對(duì) AI 引擎和可編程邏輯的優(yōu)化模塊,創(chuàng)建設(shè)計(jì)。可視化仿真結(jié)果并對(duì)其進(jìn)行分析,然后將得出的結(jié)果與使用 MALTAB? 和 Simulink? 生成的黃金參考進(jìn)行比較。

Vitis 統(tǒng)一軟件平臺(tái)包括:

AI開發(fā)平臺(tái)Vitis AI 2.5讓AI加速體驗(yàn)更上一層樓 Vitis AI新功能概述

Vitis AI 2.5 的模型庫增加了廣受歡迎的NLP及更多 CNN 模型,例如 Bert-base,Vision Transformer、端到端 O...

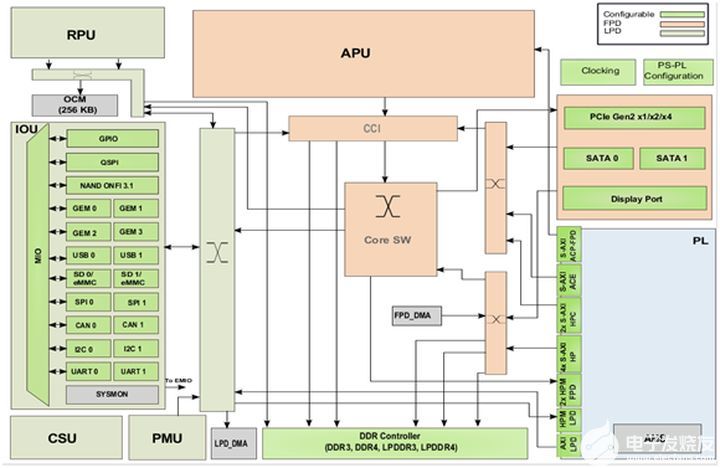

【ZYNQ Ultrascale+ MPSOC FPGA教程】第一章MPSoC芯片介紹

原創(chuàng)聲明: 本原創(chuàng)教程由芯驛電子科技(上海)有限公司(ALINX)創(chuàng)作,版權(quán)歸本公司所有,如需轉(zhuǎn)載,需授權(quán)并注明出處。 適用于板卡型號(hào): AXU2CGA...

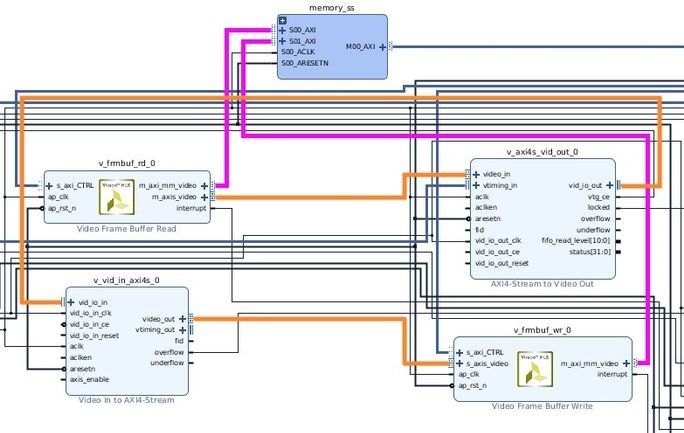

Video Frame Buffer IP初學(xué)者入門案例分析

Video Frame Buffer IP 簡(jiǎn)介 Video Frame Buffer Read/Write IP 支持您將視頻數(shù)據(jù)從存儲(chǔ)器域(AXI4...

周麗娜(Ally Zhou)女士擁有十多年 FPGA 設(shè)計(jì)、EDA 工具和多年客戶支持的經(jīng)驗(yàn)。Ally 曾先后在同濟(jì)大學(xué),芬蘭米凱利理工學(xué)院和復(fù)旦大學(xué)求...

這種方法還可以更好地與團(tuán)隊(duì)方法一起使用,并且可以創(chuàng)建可跨多個(gè)項(xiàng)目使用的加速內(nèi)核庫(IP)。另一個(gè)優(yōu)點(diǎn)是應(yīng)用于可編程邏輯實(shí)現(xiàn)的優(yōu)化駐留在 .xo 文件中,...

Vitis初探—1.將設(shè)計(jì)從SDSoC/Vivado HLS遷移到Vitis上的教程

本文介紹如何一步一步將設(shè)計(jì)從SDSoC/Vivado HLS遷移到Vitis平臺(tái)。

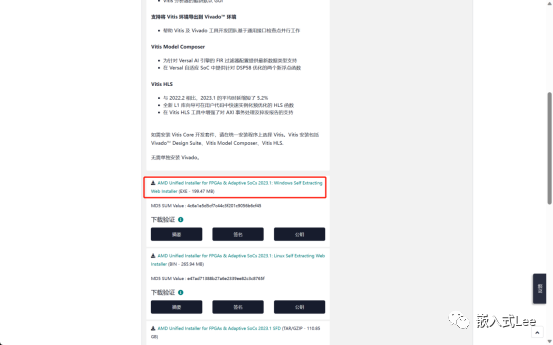

《基于“礦板”低成本學(xué)習(xí)Zynq系列》之三-vitis安裝

Xilinx提供了一整套開發(fā)環(huán)境用于其FPGA和SOC的開發(fā),主要包括硬件部分和軟件部分的開發(fā)工具,之前硬件部分是vivado軟件部分是sdk,現(xiàn)在統(tǒng)一...

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十七章Vitis準(zhǔn)備工程及注意事項(xiàng)

所有的工程目錄下都有個(gè)bootimage文件夾,存放了對(duì)應(yīng)的BOOT.bin文件,可將此文件拷貝到Vitis_image_download文件夾,覆蓋原...

Vitis統(tǒng)一軟件平臺(tái)文檔——應(yīng)用程序加速開發(fā)立即下載

類別:電子資料 2023-09-15 標(biāo)簽:fpga應(yīng)用程序UltraScale

在Kernel Estimate報(bào)告中,可以看到,Target Clock已經(jīng)按要求設(shè)置成200Mhz. 說明 Vitis_HLS是按照200Mhz的要...

Vitis軟件平臺(tái)、vitis實(shí)例、裸機(jī)SOC(SDK)程序移植教程

賽靈思公司(Xilinx)推出Vitis——這是一款統(tǒng)一軟件平臺(tái),可以讓包括軟件工程師和AI科學(xué)家在內(nèi)的廣大開發(fā)者都能受益于硬件靈活應(yīng)變的優(yōu)勢(shì)。歷經(jīng)5年...

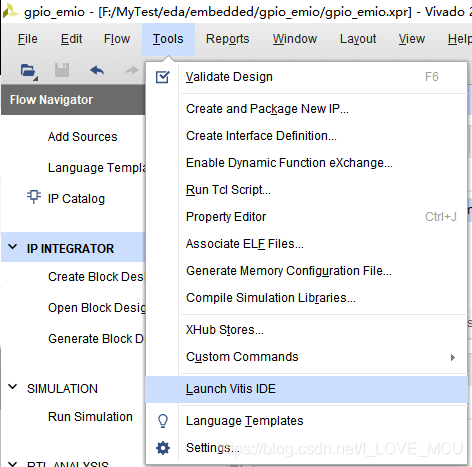

在學(xué)習(xí)ZYNQ嵌入式開發(fā)的過程中,正點(diǎn)原子的教程是采用SDK,而我下載的vivado2020.1已經(jīng)變成了vitis,所以寫一這篇博客,方便后續(xù)查閱。

如何在 Vitis 中使用 UIO 驅(qū)動(dòng)框架創(chuàng)建簡(jiǎn)單的 Linux 用戶應(yīng)用

Linux嵌入式設(shè)計(jì)中最基本的任務(wù)之一是創(chuàng)建用戶應(yīng)用程序。 在本篇博文中,我們將探討如何在 Vitis 中使用 UIO 驅(qū)動(dòng)框架創(chuàng)建簡(jiǎn)單的 Linux ...

從官網(wǎng)能夠很輕松的下載到vitis的安裝包,可以下載Installer進(jìn)行自動(dòng)下載安裝,也可以下載整個(gè)文件的壓縮包,通過其中的setup進(jìn)行安裝。

自從 Vitis 發(fā)布后,Xilinx 在 Github 上持續(xù)開源了很多資源,方便開發(fā)者進(jìn)行自己的設(shè)計(jì),減少產(chǎn)品上市時(shí)間。所以本期文章我們來看下如何獲...

利用Vitis HLS tcl shell一鍵跑通視覺加速例程

? 本文給想直接使用Vitis HLS 工具在 Standalone 模式下調(diào)用 Xilinx Vision Library L1 API 的小伙伴提供...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |