引言

本文介紹了幾種可實(shí)現(xiàn)4K2K顯示需求的超高清LED顯示屏的10Gbps光纖控制系統(tǒng)設(shè)計(jì)方案,其中XAUI分離式10Gbps單路光纖通訊方案性價(jià)比最高。

?

?

目前在市場(chǎng)上,夏普、東芝、三星、LG等公司相繼推出了4K2K超高清電視或裸眼3D電視(物理分辨率3840×2160),夏普的“ICC-4K”技術(shù)、東芝的“超解像”技術(shù)均可將當(dāng)前的1080p信號(hào)倍線到3840×2160,4K2K規(guī)格無(wú)論是水平方向還是在垂直方向,都是現(xiàn)有主流全高清顯示設(shè)備1920×1080p分辨率的2倍,總像素?cái)?shù)量達(dá)到了800萬(wàn)以上,是全高清的4倍。

而在LED全彩顯示領(lǐng)域,因具有無(wú)限拼接特點(diǎn),超過(guò)4K2K的LED顯示屏和3D LED顯示屏早已問(wèn)世。不過(guò)當(dāng)前市場(chǎng)主流LED顯示屏控制系統(tǒng)主要為近距離DVI輸入雙口千兆網(wǎng)模式和遠(yuǎn)距離2~3.125Gbps光纖通訊模式,8位色階輸入時(shí)單板支持的最大分辨率僅能達(dá)到1280×1024(60Hz,無(wú)壓縮),若要支持超高分辨率顯示,必須采用多卡或多控制器系統(tǒng),并搭配昂貴的視頻分割放大器才能實(shí)現(xiàn),但支持的源信號(hào)輸入依然是1280×1024。顯然,當(dāng)前的LED顯示屏控制系統(tǒng)已滯后于視頻和通信技術(shù)的發(fā)展,滿足不了市場(chǎng)和用戶的更高需求。為此,我們?cè)谘兄魄耙淮?~3.125Gbps LED顯示屏光纖控制器的基礎(chǔ)上,采用成熟的萬(wàn)兆網(wǎng)通訊技術(shù)和器件,設(shè)計(jì)了一種支持HDMI 1.4a音視頻輸入的超高清LED顯示屏10Gbps光纖控制系統(tǒng),大幅度提升了傳統(tǒng)LED顯示屏控制器的帶寬、功能和性價(jià)比。

總體設(shè)計(jì)方案

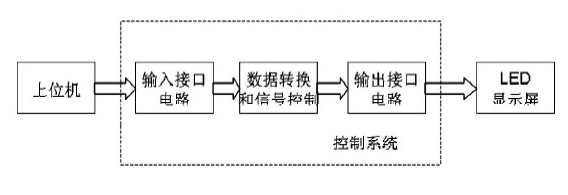

圖1所示為超高清LED顯示屏10Gbps光纖控制系統(tǒng)整體邏輯設(shè)計(jì),分為發(fā)送和接收兩部分,其中發(fā)送部分包括HDMI輸入口、DVI輸入口、USB接口、ADV7619、CP2102、FPGA、DDR、Flash、PCIe插口、外設(shè)和光纖通訊,接收部分包括光纖通訊(與發(fā)送部分完全相同)、FPGA、10~12路千兆網(wǎng)PHY輸出矩陣、DDR、Flash、外設(shè)、音頻輸出和多功能接口。

1. 音視頻輸入

音視頻輸入解碼芯片采用AMD公司的HDMI/DVI雙輸入ADV7619代替?zhèn)鹘y(tǒng)單視頻DVI芯片,支持HDMI 1.4a 36位色深1920×1080p高清電視、4k×2k超高清和3D電影視頻播放,支持HBR和DSD S/PDIF多種數(shù)字音頻格式。

2. 光纖通信

10Gbps光纖通訊設(shè)計(jì)是超高分辨率LED顯示屏單卡控制系統(tǒng)的關(guān)鍵環(huán)節(jié),其構(gòu)建和成本控制基于10G以太網(wǎng)技術(shù),尤其是10G以太網(wǎng)物理接口的發(fā)展。10G以太網(wǎng)標(biāo)準(zhǔn)IEEE 802.3ae定義了在光纖上傳輸10G以太網(wǎng)的標(biāo)準(zhǔn),傳輸距離從300m到80km。

其中IEEE 802.3ae根據(jù)光纖類型、傳輸距離等進(jìn)一步細(xì)分為7種類型。實(shí)際上目前建立在Cisco光學(xué)標(biāo)準(zhǔn)10GBASE-ZR上,可傳80km的1,550nm冷卻型電吸收調(diào)制激光器(Cooled EML)也已問(wèn)世。

在這些七種接口類型中,10GBASE-LX4使用了粗波分復(fù)用(CWDM)技術(shù),把12.5Gbps數(shù)據(jù)流分成4路3.125Gbps數(shù)據(jù)流在光纖中傳播,由于采用了8B/10B編碼,因此有效數(shù)據(jù)流量是10Gbps。這種接口類型的優(yōu)點(diǎn)是應(yīng)用場(chǎng)合比較靈活,既可以使用多模光纖,應(yīng)用于傳輸距離短對(duì)價(jià)格敏感的場(chǎng)合,也可以使用單模光纖,支持較長(zhǎng)傳輸距離的應(yīng)用。

10GBASE-SR、10GBASE-LR和10GBASE-ER的物理編碼子層(PCS)使用了效率較高的64B/66B編碼,在線路上傳輸?shù)乃俾适?0.3 Gbps。其中,10GBASE-SR使用850nm的激光器,在多模光纖上的傳輸距離是300m;10GBASE-LR和10GBASE-ER分別使用1,310nm和1,550nm的激光器,在單模光纖上的傳輸距離分別是10km和40km,適用于城域范圍內(nèi)的傳輸,是目前的主流應(yīng)用。

10GBASE-SW、10GBASE-LW和10GBASE-EW是應(yīng)用于廣域網(wǎng)的接口類型,其傳輸速率和OC-192 SDH(同步數(shù)字體系)相同,物理層使用了64B/66B的編碼,通過(guò)WIS把以太網(wǎng)幀封裝到SDH的幀結(jié)構(gòu)中去,并做了速率匹配,以便實(shí)現(xiàn)和SDH的無(wú)縫連接。

采用不同的萬(wàn)兆網(wǎng)絡(luò)通訊器件構(gòu)建超高分辨率LED顯示屏10Gbps光纖控制系統(tǒng),有以下幾種方案,分述如下。

XAUI分離式10Gbps單路光纖通訊方案:現(xiàn)在應(yīng)用比較廣泛的10G光模塊有以下幾種:300PIN、XENPAK、XPAK、X2、XFP和SFP+。其中300PIN屬于第一代模塊,主要應(yīng)用于SDH,把電接口改成10G以太網(wǎng)16位接口(XSBI)后也可應(yīng)用于10G以太網(wǎng);XENPAK是針對(duì)10G以太網(wǎng)推出的第一代光模塊,所需信號(hào)多,體積較大,價(jià)位也較高;XPAK和X2是XENPAK光模塊的直接改進(jìn)版,體積縮小了40%;XFP(遵從XFP MSA/INF-8077i協(xié)議),采用可達(dá)9.95~11.09Gbps高速串行電接口XFI,是一種外形緊湊、類似于千兆以太網(wǎng)SFP的小型化可拔插光模塊,由于內(nèi)含CDR,需要30位信號(hào)和161.25MHz的高頻時(shí)鐘輸入,故價(jià)格也不便宜,不利于10Gbps網(wǎng)絡(luò)的推廣;最新出現(xiàn)的SFP+(遵從IEEE 802.3ae、SFF-8431、SFF-8432協(xié)議)是在已成熟的1~4Gbps SFP光纖模塊基礎(chǔ)上推出的萬(wàn)兆光模塊,因信號(hào)減少到20位,單電源供電,采用9.5328~11.10Gbps高速串行電接口SFI,并將信號(hào)調(diào)制功能、MAC、串行/解串器、時(shí)鐘和數(shù)據(jù)恢復(fù)(CDR),以及電子色散補(bǔ)償(EDC)功能全部移到主板卡,憑借其小型化低成本等優(yōu)勢(shì)滿足了設(shè)備對(duì)光模塊高密度的需求,目前已經(jīng)取代XFP成為10G市場(chǎng)的主流。

10Gbps SFP+光纖模塊國(guó)內(nèi)生產(chǎn)商較多,包括華為、中興、思科、H3C、北電、網(wǎng)件、3COM、安捷倫、飛通、易飛揚(yáng)、吉訊科技、乘光網(wǎng)絡(luò)、貝嶺科技等。例如易飛揚(yáng)可傳300M的850nm VCSEL多模GPP-85192-SRC、可傳2KM的1,310nm DFB單模GPP-31192-02C、可傳10KM的GPP-31192-LRC/LRT SFP+光纖模塊等,一般都滿足:1. 光接口符合IEEE 802.3ae 10GBASE-LR;2. 電氣接口符合SFF-8431;3. 低功耗,熱插拔;4. PIN光電探測(cè)器;5. 全金屬外殼,卓越的EMI性能;6. 高級(jí)固件允許客戶系統(tǒng)加密,信息儲(chǔ)存于收發(fā)器中;7. 低成本高效益的SFP+解決方案,有利于更高端口密度和更大帶寬設(shè)計(jì);8. 適用10.3125Gbps 10GBASE-SR及其它光學(xué)鏈接。

目前國(guó)內(nèi)多模300M SFP+萬(wàn)兆光模塊價(jià)位在850元可買(mǎi)到,單模2KM SFP+萬(wàn)兆光模塊價(jià)位在1,250元左右,單模10KM SFP+萬(wàn)兆光模塊價(jià)位在1,500元左右,超過(guò)10KM則需采用其它類型的萬(wàn)兆光模塊如冷卻型萬(wàn)兆光模塊,價(jià)格就比較昂貴了。SFP+模塊電氣接口符合SFI電氣規(guī)范,收發(fā)器的差分輸入輸出阻抗是100歐姆,PECL/CML電平,內(nèi)部交流耦合。模塊提供差異終端匹配,減少了共模轉(zhuǎn)換對(duì)信號(hào)質(zhì)量的影響。SFI高速串行總線在改進(jìn)的FR4板材上布線長(zhǎng)度超過(guò)200mm,在標(biāo)準(zhǔn)FR4板材上布線長(zhǎng)度超過(guò)150mm,易于和FPGA匹配。從性價(jià)比和設(shè)計(jì)的簡(jiǎn)易性考慮,采用10Gbps SFP+模式作本設(shè)計(jì)最為適宜。單路10Gbps光纖通訊邏輯設(shè)計(jì)如圖2(a)所示。

SFP+光纖模塊要求萬(wàn)兆網(wǎng)PHY具有SFI高速串行接口,這類萬(wàn)兆網(wǎng)PHY品種較多,例如Vitesse的VSC8486、PHYNetLogic的AEL1010(具有13x13mm,144針,1毫米球間距PBGA超小型封裝)。

VSC8486是一個(gè)局域網(wǎng)/廣域網(wǎng)XAUI或XGMII收發(fā)器,3Gbps XAUI數(shù)據(jù)轉(zhuǎn)換成10Gbps的XFI/SFI串行數(shù)據(jù)流,還配備了一個(gè)額外的全速率數(shù)據(jù)口,可以用于旁路監(jiān)測(cè)或通道監(jiān)控應(yīng)用。VSC8486提供特殊的10Gbps混合信號(hào)數(shù)據(jù)性能輸出功能,可編程預(yù)加重,以延長(zhǎng)銅連接。VSC8486高速串行I/O支持由IEEE 802.3ae和T11 10 GFC定義的9.9Gbps、10.3Gbps和10.5Gbps速率,并完全符合Bellcore GR253定義的SONET抖動(dòng)規(guī)范。

VSC8486設(shè)備中有四個(gè)主要的數(shù)據(jù)處理模塊:XGXS、PCS、WIS和PMA。10GbE以太網(wǎng)的擴(kuò)展子層(XGXS)接收運(yùn)行在3.125Gbps的8B/10B數(shù)據(jù),解碼后發(fā)送到物理編碼子層(PCS)。該XGXS具有處理通道間超過(guò)60bit間格的抗扭曲能力。PCS根據(jù)IEEE 802.3ae第49條規(guī)定64B/66B算法,對(duì)來(lái)自XGXS的10Gbps數(shù)據(jù)進(jìn)行編碼。

PCS是一個(gè)可選的運(yùn)行在64B/66B速率的擴(kuò)展模式(E-PCS),這種擴(kuò)展模式使用一個(gè)替代的框架算法,增加了前向糾錯(cuò)FEC,提供約2.5dB的網(wǎng)絡(luò)電氣增益。PCS適用于局域網(wǎng)模式,但不適用于WAN模式。

PCS輸出數(shù)據(jù)到廣域網(wǎng)接口子層WIS(繞過(guò)局域網(wǎng)模式)。按IEEE 802.3ae第50條描述規(guī)定,WIS可對(duì)來(lái)自PCS的9.953Gbps數(shù)據(jù)和SONET STS-192C幀數(shù)據(jù)進(jìn)行選擇。此外,WIS模塊包含擴(kuò)展SONET和SDH的處理能力,允許系統(tǒng)充分利用有價(jià)值的性能監(jiān)測(cè)數(shù)據(jù)。最后,數(shù)據(jù)傳遞到物理介質(zhì)連接模塊PMA,PMA將內(nèi)部多路并行總線數(shù)據(jù)轉(zhuǎn)化為10Gbps的數(shù)據(jù)流。

10Gbps到XAUI數(shù)據(jù)通道的執(zhí)行操作和上述描述相反,其路徑上的顯著特點(diǎn)是擁有一個(gè)SONET兼容LOS監(jiān)測(cè)器和一個(gè)完全兼容XFI/SFI規(guī)格(包括強(qiáng)制的眼圖要求)的10Gbps接收器。

SFI集成式10Gbps單路光纖通訊方案:?jiǎn)温?0Gbps光纖通訊模式還有一種造價(jià)較高的全FPGA設(shè)計(jì)模式,外掛的10GbE PHY已嵌入FPGA內(nèi)部,利用FPGA的SFI高速串行總線,直接和SFP+模塊接口,邏輯設(shè)計(jì)見(jiàn)圖2(b),其詳述見(jiàn)下文FPGA信息處理。

4×3.125Gbps多路光纖通訊方案:4×3.125Gbps多路光纖通訊方案是一種低成本、可靈活在3.125、6.25、9.75、12.5Gbps帶寬中選擇應(yīng)用的單卡拼接方案,圖2(c)為邏輯設(shè)計(jì)。從圖可看出,它不需要外掛較昂貴的10Gbps串行器/解串器(SerDes),利用FPGA內(nèi)嵌的4個(gè)3.125Gbps SerDes直接和4個(gè)4.25Gbps SFP光纖模塊接口。SFP光纖模塊應(yīng)用廣泛,例如易飛揚(yáng)可傳500M的GP-854G-S5x(D) 4.25Gbps SFP多模光纖模塊,可傳10KM的GP-314G-L1x(D)單模光纖模塊等。FPGA可從Altera較低檔的60nm Cyclone IV GX(3.125Gbps)、28nm Cyclone V GX(3.125Gbps)中選用。這兩種芯片均具有利于設(shè)計(jì)的以下特點(diǎn):

1. 靈活而且容易配置的收發(fā)器數(shù)據(jù)通路,可實(shí)現(xiàn)工業(yè)標(biāo)準(zhǔn)和專用協(xié)議;2. 可編程預(yù)加重設(shè)置和可調(diào)差分輸出電壓(VOD),提高了信號(hào)完整性;3. 用戶可控的接收器均衡,增益達(dá)到7dB,補(bǔ)償物理介質(zhì)的頻率相關(guān)損耗;4. 收發(fā)器動(dòng)態(tài)重新配置,不需要對(duì)FPGA重新編程,支持同一通道上的多種協(xié)議和數(shù)據(jù)速率;5. 兼容PCI Express (PIPE)、XAUI和千兆以太網(wǎng)物理接口的專用電路;6. PIPE接口可直接連接嵌入式PCI Express Gen1和Gen2(2.5/5.0 Gbps)硬核知識(shí)產(chǎn)權(quán)(IP)或者軟核IP;7. 片內(nèi)電源去耦合功能,不需要板上去耦電容,簡(jiǎn)化了設(shè)計(jì),滿足了高頻時(shí)的瞬變電流要求。

4×3.125Gbps多路光纖通訊方案在萬(wàn)兆網(wǎng)網(wǎng)線和光纖通訊技術(shù)應(yīng)用成本較高的早期無(wú)疑是一個(gè)值得推薦的方案,然而隨著萬(wàn)兆網(wǎng)網(wǎng)線和光纖通訊技術(shù)應(yīng)用日益發(fā)展成熟和成本的快速下降,其優(yōu)越性已不明顯。同時(shí)4路光纖輸出占用了較大空間,加上HDMI/DVI、USB口和信號(hào)指示燈,很難做成插卡式,只能外置或舍棄DVI輸入口,要用DVI時(shí)采用DVI-HDMI轉(zhuǎn)換器。

2×6.25Gbps雙路光纖通訊方案:2×6.25Gbps兩路光纖通訊方案是在4×3.125Gbps多路光纖通訊方案上的改進(jìn),邏輯設(shè)計(jì)如圖2(d)所示。該方案利用FPGA內(nèi)嵌的2個(gè)6.25Gbps SerDes直接和2個(gè)6.25Gbps SFP+光纖模塊接口,例如易飛揚(yáng)可傳2KM的GPP-316G-02x 1,310nm單模SFP+模塊。FPGA可采用40nm Arria @II GX/GZ系列芯片,SerDes速率可達(dá)6.375Gbps。又如賽靈思Artix-7 FPGA中的GTP,也可達(dá)到6.6Gbps的速率。

該方案和4×3.125Gbps多路光纖通訊方案相比,全帶寬運(yùn)行時(shí)成本相差不大,但在設(shè)計(jì)的簡(jiǎn)易性和工作的可靠性上略勝一籌。由于該方案只有兩路光纖,占用空間較小,允許做成插卡式。

4×3.125Gbps多路和2×6.25Gbps兩路光纖通訊方案的優(yōu)點(diǎn)是可根據(jù)LED顯示屏的實(shí)際分辨率靈活構(gòu)建,在非全帶寬運(yùn)行時(shí)成本較低,缺點(diǎn)是布線相對(duì)復(fù)雜,在全帶寬多路運(yùn)行時(shí)成本未必占優(yōu)勢(shì),可靠性相對(duì)較低,并需要妥善解決各通道間的同步問(wèn)題。而XAUI分離式和SFI集成式10Gbps單路光纖通訊方案集成度高,單路帶寬即達(dá)到10Gbps,布線簡(jiǎn)單、可靠性也相對(duì)較高。從性價(jià)比和設(shè)計(jì)的難易程度各方面綜合考慮,顯然首推第一種分離式單路10Gbps光纖通訊方案為最優(yōu)方案。

3. FPGA信息處理

大規(guī)模可編程芯片F(xiàn)PGA是超高分辨率LED顯示屏控制系統(tǒng)設(shè)計(jì)的核心,所有信息包括高清音視頻接收、緩存、轉(zhuǎn)換、輸出、控制信號(hào)嵌入、狀態(tài)顯示、DDR、Flash和外部設(shè)備管理等均由FPGA進(jìn)行處理。與傳統(tǒng)的LED顯示屏控制系統(tǒng)比較,其最大不同在于10Gbps通訊。目前Altera、賽靈思、Lattice等主流FPGA制造商都能提供用于10GbE通訊的FPGA芯片,例如Altera的Stratix V(GX和GT)、Stratix IV(GX和GT)、Cyclone IV GX,Stratix II GX、Arria系列和HardCopy IV GX器件都有內(nèi)置收發(fā)器,為XAUI接口的實(shí)現(xiàn)提供專用模式。XAUI收發(fā)器模塊提供156.25MHz輸入?yún)⒖紩r(shí)鐘和并行接口,帶有4通道時(shí)鐘數(shù)據(jù)恢復(fù)(CDR)接收器和4通道收發(fā)器陣列以及交流耦合差分接口和差分PCML驅(qū)動(dòng)電路。收發(fā)器模塊嵌入了專用速率匹配和時(shí)鐘補(bǔ)償FIFO緩沖,還采用了1:16 SerDes、16:20變換器、8B/10B編碼和字對(duì)齊功能,所有這些功能都由專用XAUI狀態(tài)機(jī)進(jìn)行控制。每組四通道還內(nèi)置了通道對(duì)齊電路,以減小XAUI接口從XAUI源到宿的偏移。收發(fā)器可提供500%的預(yù)加重和高達(dá)17dB的均衡,以補(bǔ)償高頻損耗。

帶XAUI接口,并集成了物理編碼子層(PCS)、萬(wàn)兆以太網(wǎng)MAC的FPGA內(nèi)部邏輯結(jié)構(gòu)通過(guò)XAUI接口和各種10GbE PHY器件相連。FPGA和原始視頻源的接口采用Altera的Avalon-ST用戶界面,64位寬度,運(yùn)行在156.25MHz,具有10Gbps的全雙工吞吐速率,F(xiàn)PGA的MDIO接口提供了一個(gè)Avalon Memory-Mapped(Avalon-MM)內(nèi)存映射MDIO的橋梁,用于控制外部10GbE PHY。至于FPGA內(nèi)部的萬(wàn)兆以太網(wǎng)MAC,因LED顯示屏本身不是局域網(wǎng)終端,屬于點(diǎn)對(duì)點(diǎn)高速通訊范疇,與傳統(tǒng)千兆網(wǎng)控制系統(tǒng)一樣,無(wú)需遵從萬(wàn)兆以太網(wǎng)協(xié)議,故可不予采用而簡(jiǎn)化設(shè)計(jì)。FPGA具體的軟件設(shè)計(jì)可從網(wǎng)上參考或下載Altera公司的萬(wàn)兆以太網(wǎng)用戶手冊(cè)。

Stratix V(GX和GT)、Stratix IV(GX和GT)、Cyclone IV GX(F23和更大器件)、HardCopy IV GX、Arria II GX、Stratix II GX以及Arria GX器件中的收發(fā)器模塊符合所有的IEEE 802.3ae規(guī)范,包括沒(méi)有預(yù)加重時(shí)小于0.35單位間隔(UI)的抖動(dòng)發(fā)生,以及最大峰峰值大于0.60UI的抖動(dòng)容限。收發(fā)器模塊符合IEEE 802.3正弦抖動(dòng)容限模板要求。萬(wàn)兆以太網(wǎng)3.125Gbps×4通道單向數(shù)據(jù)傳送速率符合IEEE 802.3ae XAUI對(duì)物理層器件和上層器件鏈接的定義。

FPGA芯片技術(shù)發(fā)展很快,高檔FPGA芯片單個(gè)SerDes的速率已發(fā)展到100Gbps,某些高檔型號(hào)的FPGA已具備10.3Gpbs XFI/SFI高速串行接口,例如Altera 40nm的Stratix IV GX即內(nèi)嵌10Gbps PHY,可直接外掛10Gbps XFP/SFP+光纖模塊,達(dá)到設(shè)計(jì)的最簡(jiǎn)化。不利因素是此類FPGA芯片造價(jià)較高,目前主要用于通信、數(shù)字廣播、測(cè)試設(shè)備、大存儲(chǔ)系統(tǒng)高帶寬領(lǐng)域。另外賽靈思的Kintex-7和Virtex-7 FPGA中的GTX也提供了經(jīng)濟(jì)高效的12.5Gbps光學(xué)與背板應(yīng)用。

4. 其他模塊

采用Silicon Labs公司的USB轉(zhuǎn)UART橋接芯片CP2102代替?zhèn)鹘y(tǒng)的RS-232口實(shí)現(xiàn)PC和FPGA通訊。CP2102包含USB 2.0全速功能控制器,工作時(shí)作為一個(gè)虛擬COM口使用,且滿足RS-232總線的波特率要求。

為和傳統(tǒng)LED顯示屏模組掃描控制器所用的千兆網(wǎng)PHY兼容,分配器采用10~12路千兆網(wǎng)PHY構(gòu)成LED視頻輸出矩陣與LED顯示屏體的10~12個(gè)分區(qū)接口,足以支持4K2K、高色階或3D顯示。

音頻輸出、DDR、Flash、PCIe和外設(shè)部分的設(shè)計(jì)與常規(guī)設(shè)計(jì)相同,這里不再贅述。

結(jié)束語(yǔ)

綜上所述,超高清LED顯示屏10Gbps光纖控制系統(tǒng)具有多種設(shè)計(jì)方案,其中XAUI分離式10Gbps單路光纖通訊方案性價(jià)比最高。10Gbps光纖控制系統(tǒng)和傳統(tǒng)的2~3.125Gbps光纖控制方案相比,其優(yōu)勢(shì)在于:1. DVI視頻解碼器被支持HDMI 1.4a的HDMI/DVI雙輸入解碼芯片替代,支持4K2K超高分辨率顯示、高色階顯示、3D顯示和音頻通道;2. 低檔FPGA芯片被具有一至多個(gè)高速SerDes串口的中高檔FPGA芯片替代,支持10GbE網(wǎng)絡(luò)通訊和PCIe通訊;3. 通訊邏輯總帶寬達(dá)10~12.5Gbps,是2×1Gbps的5~6倍;4. 接收器采用12路千兆網(wǎng)PHY輸出矩陣,可支持10~12個(gè)LED顯示屏體分區(qū);5. 支持高保真立體聲音頻同步播放;6. 高帶寬支持發(fā)送端亮度、色度校正變換,簡(jiǎn)化了LED顯示屏的點(diǎn)校正應(yīng)用;7. 高度集成化設(shè)計(jì),性價(jià)比高;8. 理想的高檔LED和液晶拼接墻控制器產(chǎn)品,尤其適用于超高清多媒體播放。

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論