單穩(wěn)態(tài)觸發(fā)器原理及應(yīng)用

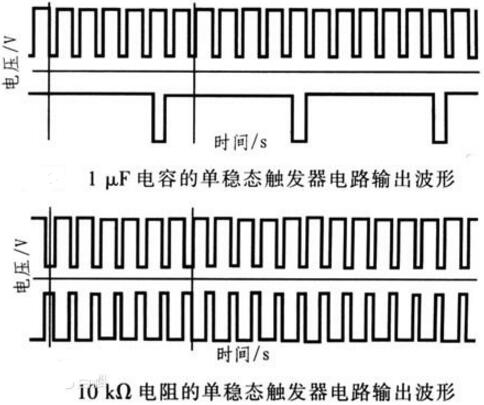

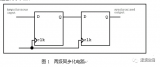

多諧振蕩器是一種自激振蕩電路。因?yàn)闆](méi)有穩(wěn)定的工作狀態(tài),多諧振蕩器也稱為無(wú)穩(wěn)態(tài)電路。具體地說(shuō),如果一開始多諧振蕩器處于0狀態(tài),那

2010-05-27 09:34:28 3842

3842

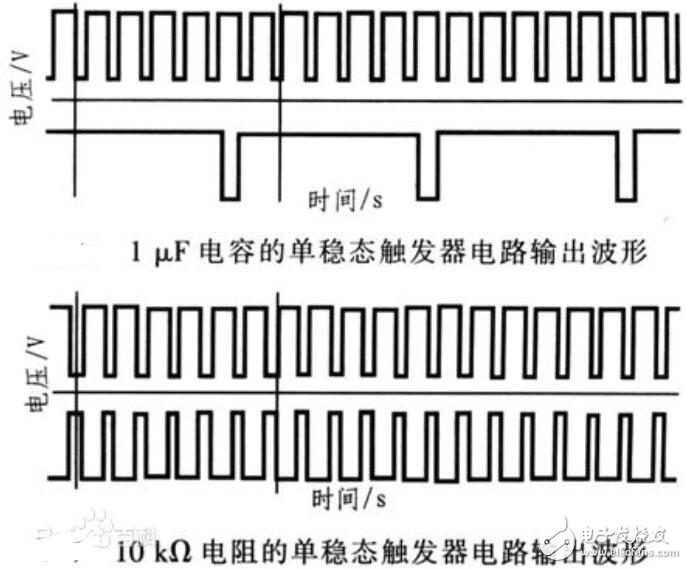

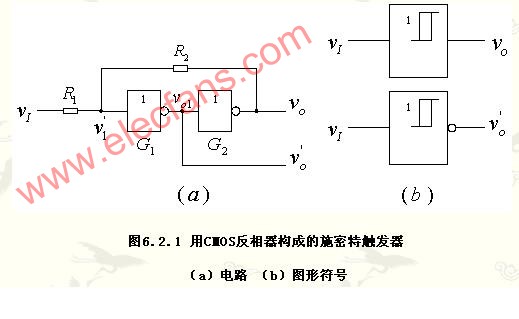

用CMOS與非門或者或非門都可以組成單穩(wěn)態(tài)觸發(fā)器,這種單穩(wěn)態(tài)觸發(fā)器在電路中廣泛地用于對(duì)脈沖信號(hào)的延

2010-12-01 13:49:36 9031

9031

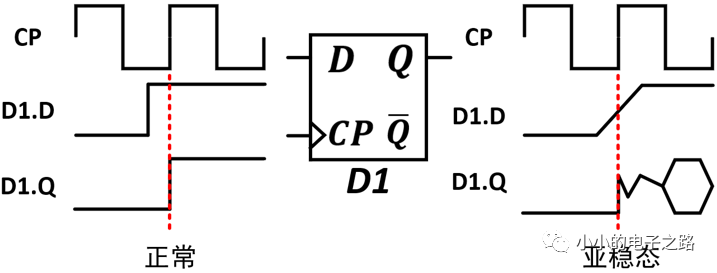

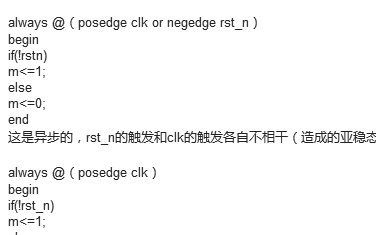

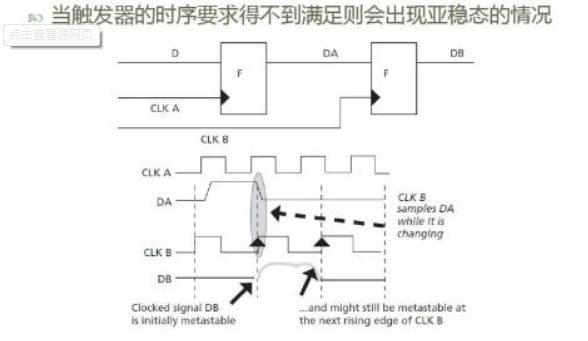

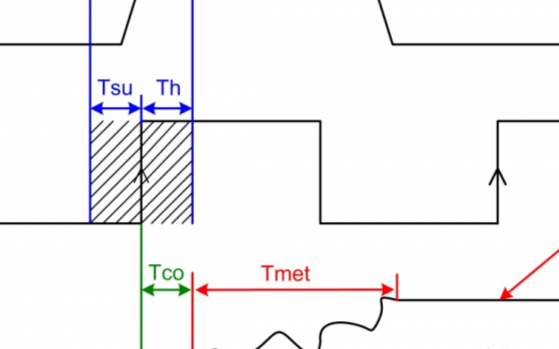

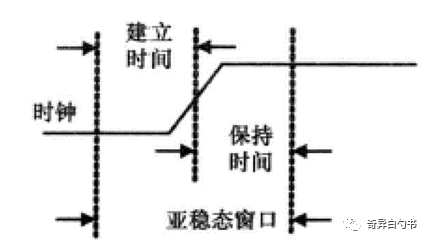

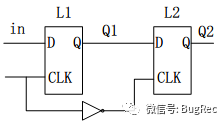

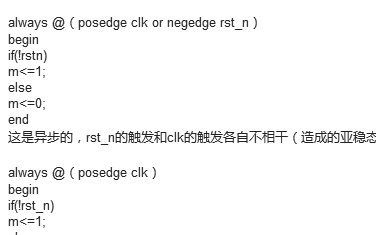

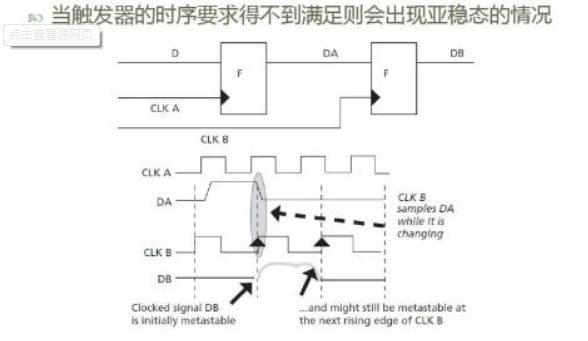

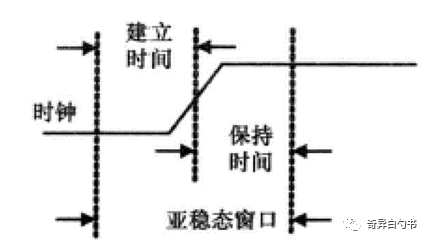

發(fā)生亞穩(wěn)態(tài)的原因是信號(hào)在傳輸?shù)倪^(guò)程中不能滿足觸發(fā)器的建立時(shí)間和保持時(shí)間。

2023-06-20 15:29:58 710

710

亞穩(wěn)態(tài)是指觸發(fā)器的輸入信號(hào)無(wú)法在規(guī)定時(shí)間內(nèi)達(dá)到一個(gè)確定的狀態(tài),導(dǎo)致輸出振蕩,最終會(huì)在某個(gè)不確定的時(shí)間產(chǎn)生不確定的輸出,可能是0,也可能是1,導(dǎo)致輸出結(jié)果不可靠。

2023-11-22 18:26:09 1115

1115

單穩(wěn)態(tài)觸發(fā)器,又稱為單穩(wěn)態(tài)多譜儀,是一種常用的數(shù)字電子元件。它具有兩個(gè)穩(wěn)定狀態(tài):穩(wěn)定狀態(tài)1和穩(wěn)定狀態(tài)2。 單穩(wěn)態(tài)觸發(fā)器是由幾個(gè)邏輯門組成的電子電路,其中最常見(jiàn)的是由兩個(gè)非門和一個(gè)門而構(gòu)成。非門的輸入

2023-12-08 10:44:45 859

859 亞穩(wěn)態(tài)是數(shù)字電路設(shè)計(jì)中最為基礎(chǔ)和核心的理論。同步系統(tǒng)設(shè)計(jì)中的多項(xiàng)技術(shù),如synthesis,CTS,STA等都是為了避免同步系統(tǒng)產(chǎn)生亞穩(wěn)態(tài)。異步系統(tǒng)中,更容易產(chǎn)生亞穩(wěn)態(tài),因此需要對(duì)異步系統(tǒng)進(jìn)行特殊的設(shè)計(jì)處理。學(xué)習(xí)SoC芯片設(shè)計(jì),歡迎加入啟芯QQ群:275855756

2013-11-01 17:45:15

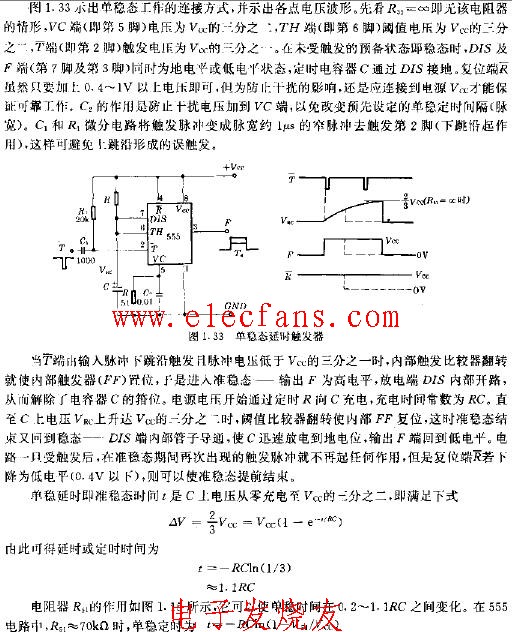

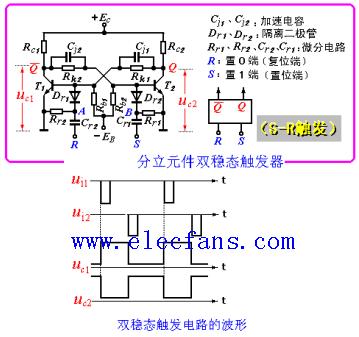

數(shù)字電路--觸發(fā)器雙穩(wěn)態(tài)觸發(fā)器

2017-02-05 14:16:51

穩(wěn)定狀態(tài),一種穩(wěn)態(tài)是T1管導(dǎo)通、T2管圖2截止,輸出u0為高電位;另一種穩(wěn)態(tài)是T1管截止,T2管導(dǎo)通,u0為低電位。觸發(fā)器的穩(wěn)定狀態(tài)決定于輸入u電位的高低,因此這種觸發(fā)器具有電位觸發(fā)特性。當(dāng)輸入ui為

2012-06-18 11:42:43

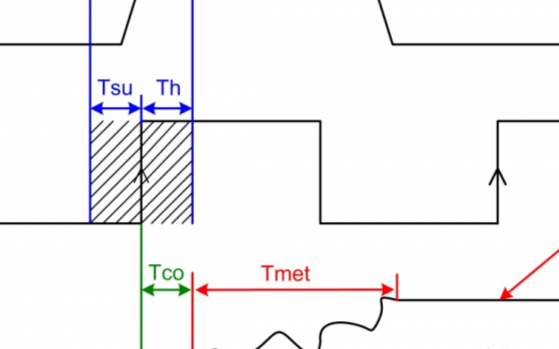

在 FPGA 系統(tǒng)中,如果數(shù)據(jù)傳輸中不滿足觸發(fā)器的 Tsu 和 Th 不滿足,或者復(fù)位過(guò)程中復(fù)位信號(hào)的釋放相對(duì)于有效時(shí)鐘沿的恢復(fù)時(shí)間(recovery time)不滿足,就可能產(chǎn)生亞穩(wěn)態(tài),此時(shí)觸發(fā)器

2020-10-22 11:42:16

的問(wèn)題。亞穩(wěn)態(tài)的特點(diǎn): 1. 增加觸發(fā)器進(jìn)入穩(wěn)定狀態(tài)的時(shí)間。 亞穩(wěn)態(tài)的壞處之一是會(huì)導(dǎo)致觸發(fā)器的TCO時(shí)間比正常情況要大。多出來(lái)的時(shí)間tR (resolution time) 就是亞穩(wěn)態(tài)持續(xù)的時(shí)間,參考圖1

2012-12-04 13:51:18

本帖最后由 eehome 于 2013-1-5 09:55 編輯

1. 應(yīng)用背景1.1亞穩(wěn)態(tài)發(fā)生原因在FPGA系統(tǒng)中,如果數(shù)據(jù)傳輸中不滿足觸發(fā)器的Tsu和Th不滿足,或者復(fù)位過(guò)程中復(fù)位信號(hào)

2012-04-25 15:29:59

1. 應(yīng)用背景1.1亞穩(wěn)態(tài)發(fā)生原因在FPGA系統(tǒng)中,如果數(shù)據(jù)傳輸中不滿足觸發(fā)器的Tsu和Th不滿足,或者復(fù)位過(guò)程中復(fù)位信號(hào)的釋放相對(duì)于有效時(shí)鐘沿的恢復(fù)時(shí)間(recovery time)不滿足,就可能

2012-01-11 11:49:18

說(shuō)起亞穩(wěn)態(tài),首先我們先來(lái)了解一下什么叫做亞穩(wěn)態(tài)。亞穩(wěn)態(tài)現(xiàn)象:信號(hào)在無(wú)關(guān)信號(hào)或者異步時(shí)鐘域之間傳輸時(shí)導(dǎo)致數(shù)字器件失效的一種現(xiàn)象。

2019-09-11 11:52:32

各位大哥,有誰(shuí)用altium designer 仿真過(guò)單穩(wěn)態(tài)觸發(fā)器的嗎?比如74ls123之類的,我在庫(kù)里怎么找不到仿真模型啊!是原本就不帶嗎?有沒(méi)有高手自己寫過(guò)啊!求幫助!

2012-03-01 15:15:18

要求的,進(jìn)而出現(xiàn)亞穩(wěn)態(tài)。但是有人認(rèn)為, “cnt”的值原來(lái)是零,“clr_cnt”只是把”cnt”的值清零, 這樣來(lái)說(shuō)觸發(fā)器“cnt”的輸入根本沒(méi)有發(fā)生過(guò)變化,怎么可能有亞穩(wěn)態(tài)事件? 而且故障出現(xiàn)的概率

2012-12-04 13:55:50

`作者:Primitivo Matas Sanz,技術(shù)專家,西班牙馬德里Telefonica I+D 公司,技術(shù)專家現(xiàn)身說(shuō)教,使用觸發(fā)器鏈(賽靈思FPGA 中ILOGIC 塊的組成部分)限制設(shè)計(jì)中

2012-03-05 14:11:41

是為了防止觸發(fā)器變成亞穩(wěn)態(tài)`timescale 1ns / 1psmodule key_test(inputclk,input [3:...

2021-07-30 06:44:48

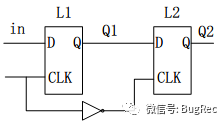

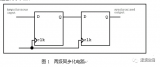

什么是同步邏輯和異步邏輯?同步電路和異步電路的區(qū)別在哪?為什么觸發(fā)器要滿足建立時(shí)間和保持時(shí)間?什么是亞穩(wěn)態(tài)?為什么兩級(jí)觸發(fā)器可以防止亞穩(wěn)態(tài)傳播?

2021-08-09 06:14:00

的分析一下。

背景

1、亞穩(wěn)態(tài)發(fā)生原因

在FPGA系統(tǒng)中,如果數(shù)據(jù)傳輸中不滿足觸發(fā)器的Tsu和Th不滿足,或者復(fù)位過(guò)程中復(fù)位信號(hào)的釋放相對(duì)于有效時(shí)鐘沿的恢復(fù)時(shí)間(recovery time)不滿足

2023-04-27 17:31:36

讓我們從觸發(fā)器開始,所有觸發(fā)器都有一個(gè)圍繞活動(dòng)時(shí)鐘沿的建立(setup time)和保持窗口(hold time),在此期間數(shù)據(jù)不得更改。如果該窗口中的數(shù)據(jù)實(shí)際發(fā)生了變化,則觸發(fā)器的輸出將進(jìn)入不確定

2022-10-18 14:29:13

flip-flop) D觸發(fā)器可以說(shuō)是最常用的了。在寫Verilog時(shí),觸發(fā)器均為D觸發(fā)器。雙穩(wěn)態(tài)多諧振蕩器(Bistable Multivibrator),是一種應(yīng)用在數(shù)字電路上具有記憶功能的循序邏輯組件,可記錄

2016-05-21 06:50:08

問(wèn)題的,不過(guò)還是有一些方法可降低系統(tǒng)出現(xiàn)亞穩(wěn)態(tài)問(wèn)題的幾率。先來(lái)深入研究一下引起亞穩(wěn)態(tài)的原因,再談?wù)動(dòng)媚男┓椒右詰?yīng)對(duì)。什么是亞穩(wěn)態(tài) 在FPGA等同步邏輯數(shù)字器件中,所有器件的寄存器單元都需要預(yù)定義信號(hào)時(shí)序

2010-12-29 15:17:55

什么是單穩(wěn)態(tài)觸發(fā)器?單穩(wěn)態(tài)觸發(fā)器的工作特點(diǎn)是什么?

2021-04-22 06:09:01

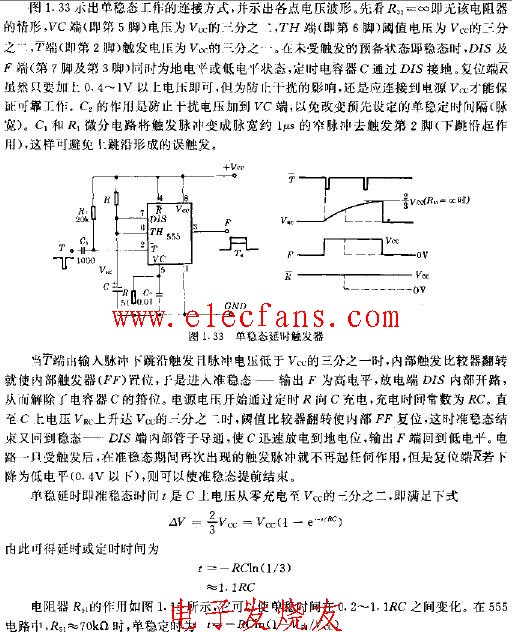

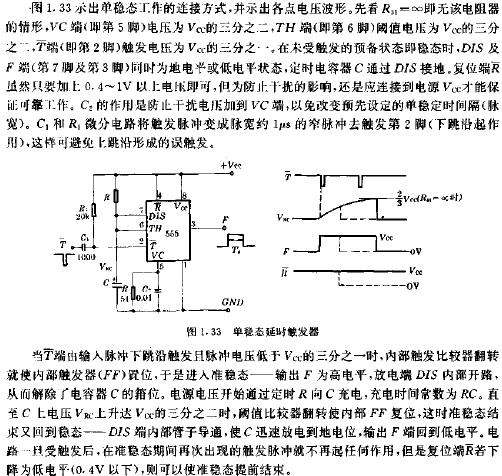

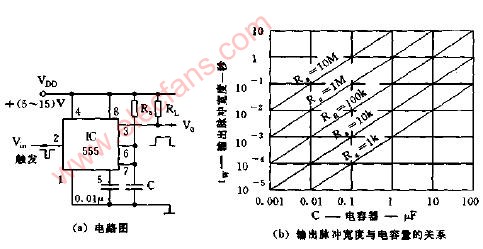

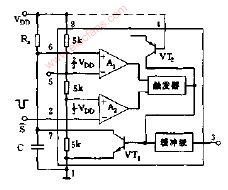

單穩(wěn)態(tài)延時(shí)觸發(fā)器

2019-11-08 09:01:59

部分。數(shù)字邏輯電路是由組合邏輯和時(shí)序邏輯器件構(gòu)成,在時(shí)序邏輯器件中,常用就是時(shí)鐘觸發(fā)的寄存器。 如果在設(shè)計(jì)中,所有的寄存器的時(shí)鐘端都是連接的同一個(gè)時(shí)鐘,那么稱之為同步電路設(shè)計(jì)。所謂同步也就是所有

2023-02-28 16:38:14

亞穩(wěn)態(tài)概述01 亞穩(wěn)態(tài)發(fā)生原因在 FPGA 系統(tǒng)中,如果數(shù)據(jù)傳輸中不滿足觸發(fā)器的 Tsu 和 Th 不滿足,或者復(fù)位過(guò)程中復(fù)位信號(hào)的釋放相對(duì)于有效時(shí)鐘沿的恢復(fù)時(shí)間(recovery time)不滿足

2020-10-19 10:03:17

微分型單穩(wěn)態(tài)觸發(fā)器的Multisim分析

2012-08-06 13:13:22

新建兩個(gè)D觸發(fā)器的目的是什么?何謂亞穩(wěn)態(tài)?解決亞穩(wěn)態(tài)的方法是什么?

2021-11-09 07:15:01

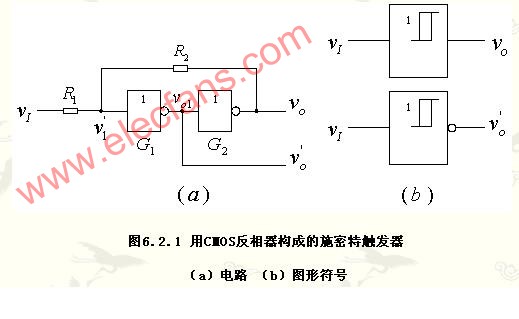

施密特觸發(fā)器的特性和符號(hào)

2019-09-17 01:31:17

觸發(fā)器(Flip-Flop,簡(jiǎn)寫為 FF),也叫雙穩(wěn)態(tài)門,又稱雙穩(wěn)態(tài)觸發(fā)器。是一種可以在兩種狀態(tài)下運(yùn)行的數(shù)字邏輯電路。觸發(fā)器一直保持它們的狀態(tài),直到它們收到輸入脈沖,又稱為觸發(fā)。當(dāng)收到輸入脈沖

2019-06-20 04:20:50

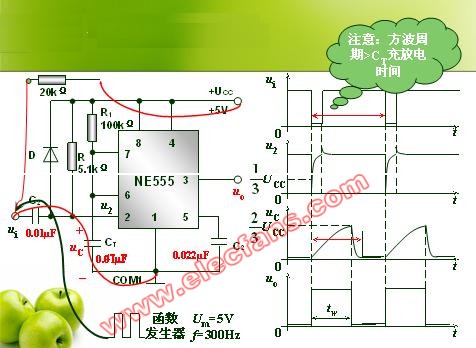

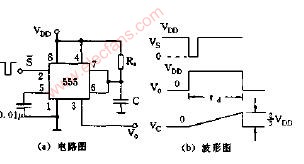

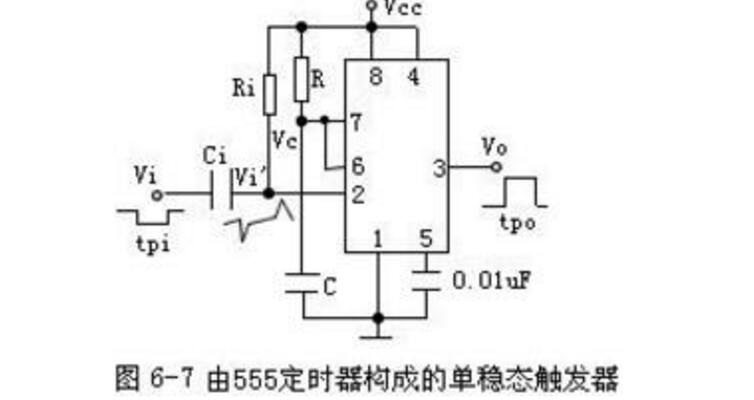

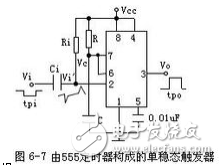

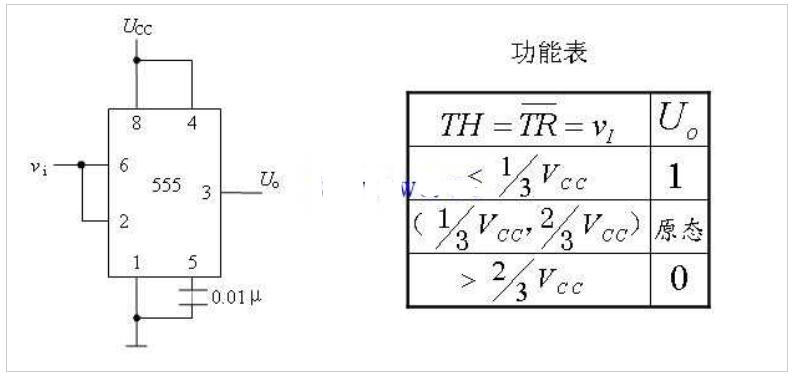

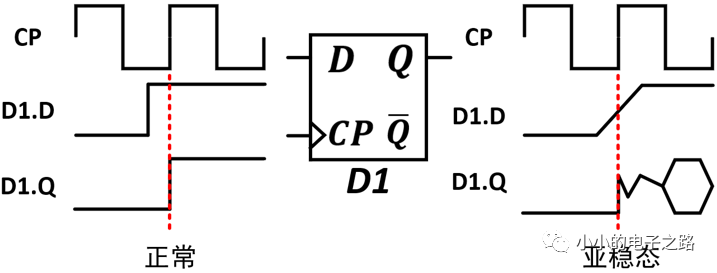

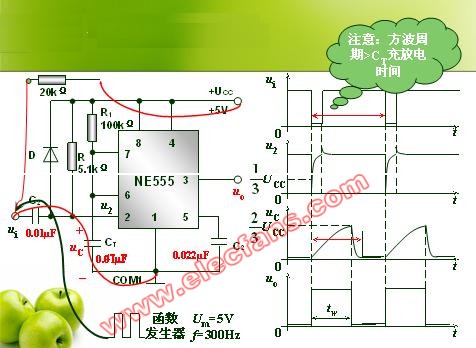

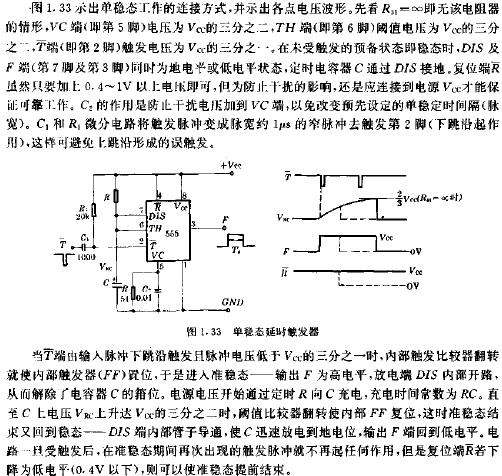

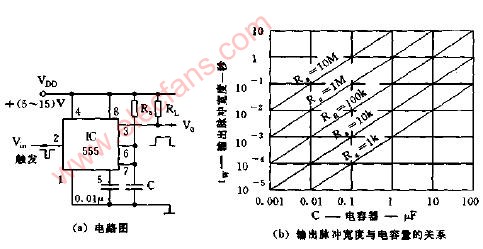

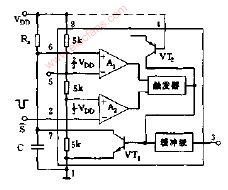

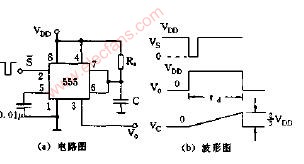

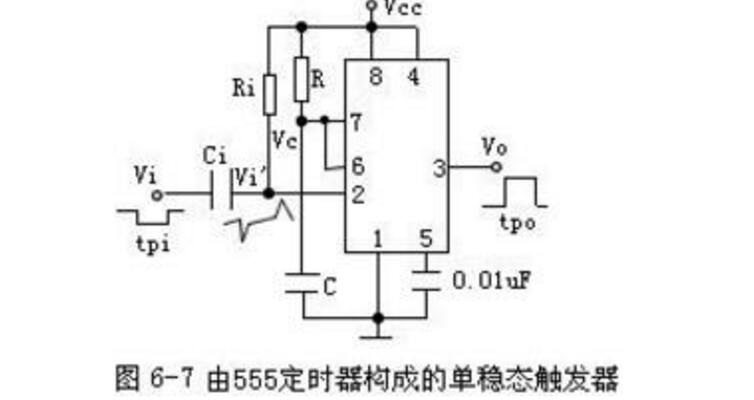

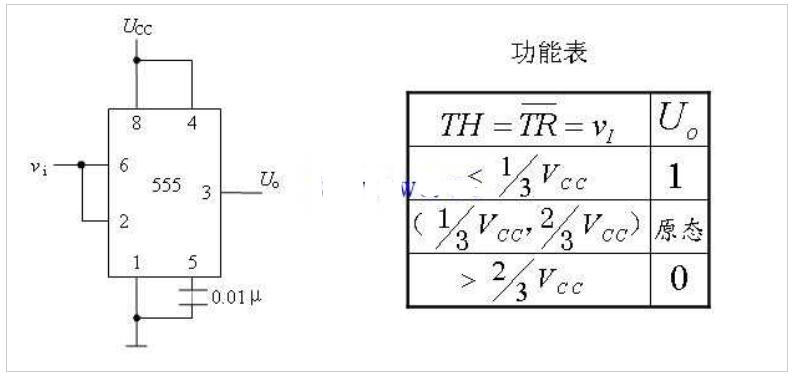

用555定時(shí)器組成單穩(wěn)態(tài)觸發(fā)器 接通VCC后瞬間,VCC通過(guò)R對(duì)C充電,當(dāng)uc上升到2VCC/3時(shí),比較器C1輸出為0,將觸發(fā)器置0,uo=0。這時(shí)Q=1,放電管T導(dǎo)通,C通過(guò)T放電,電路進(jìn)入穩(wěn)態(tài)

2009-09-24 09:51:13

說(shuō)起亞穩(wěn)態(tài),首先我們先來(lái)了解一下什么叫做亞穩(wěn)態(tài)。亞穩(wěn)態(tài)現(xiàn)象:信號(hào)在無(wú)關(guān)信號(hào)或者異步時(shí)鐘域之間傳輸時(shí)導(dǎo)致數(shù)字器件失效的一種現(xiàn)象。接下來(lái)主要討論在異步時(shí)鐘域之間數(shù)據(jù)傳輸所產(chǎn)生的亞穩(wěn)態(tài)現(xiàn)象,以及如何降低

2018-08-01 09:50:52

實(shí)驗(yàn)八 波形產(chǎn)生及單穩(wěn)態(tài)觸發(fā)器一、實(shí)驗(yàn)?zāi)康?、 熟悉多諧振蕩器的電路特點(diǎn)及振蕩頻率估算方法。2、 掌握單穩(wěn)態(tài)觸發(fā)器的使用。二、實(shí)驗(yàn)儀器及材料1

2009-03-20 17:55:07 42

42 CC4098--雙可重觸發(fā)單穩(wěn)態(tài)觸發(fā)器:CC4098 由兩個(gè)可重觸發(fā)的單穩(wěn)態(tài)觸發(fā)器組成,Q 和Q輸出有緩沖,輸出特性對(duì)稱,該器件在工作時(shí)應(yīng)在CEXT 和REXT /CEXT 端間外接電容 C,在REXT /CEXT 和VDD 端

2009-11-01 15:09:31 161

161 可重觸發(fā)單穩(wěn)態(tài)觸發(fā)器(有清除端)簡(jiǎn)要說(shuō)明:122為可以重觸發(fā)的單穩(wěn)態(tài)觸發(fā)器,共有54/74122 和54/74LS122 兩種線路結(jié)構(gòu)型式,其主要電特性的典型值如下:122 的輸出脈沖寬

2010-09-19 10:07:04 117

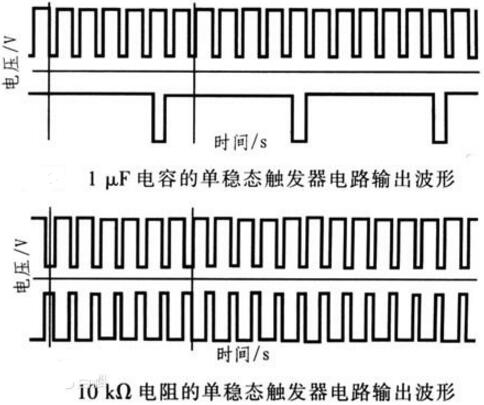

117 針對(duì)目前高校教學(xué)中555單穩(wěn)態(tài)觸發(fā)器設(shè)計(jì)和調(diào)試實(shí)驗(yàn)電路中存在的問(wèn)題,提出運(yùn)用先進(jìn)EDA技術(shù)完成單穩(wěn)態(tài)觸發(fā)器設(shè)計(jì)和仿真研究的方法,使電路設(shè)計(jì)過(guò)程具有快捷性、高效性和準(zhǔn)確

2010-12-28 10:37:22 0

0

單穩(wěn)態(tài)觸發(fā)器

作者:上海

2006-07-03 14:25:13 17083

17083

單穩(wěn)態(tài)延時(shí)觸發(fā)器

2008-05-19 23:05:30 2617

2617

單穩(wěn)態(tài)延時(shí)觸發(fā)器

2008-05-19 23:05:35 941

941

什么是雙穩(wěn)態(tài)觸發(fā)器?

雙穩(wěn)態(tài)觸發(fā)電路實(shí)際上也是RS觸發(fā)器,其ui1端相當(dāng)于R端,ui2端相當(dāng)于S端。因此,用門電路組成的

2008-05-26 13:31:40 9437

9437

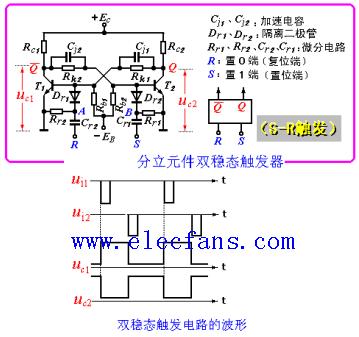

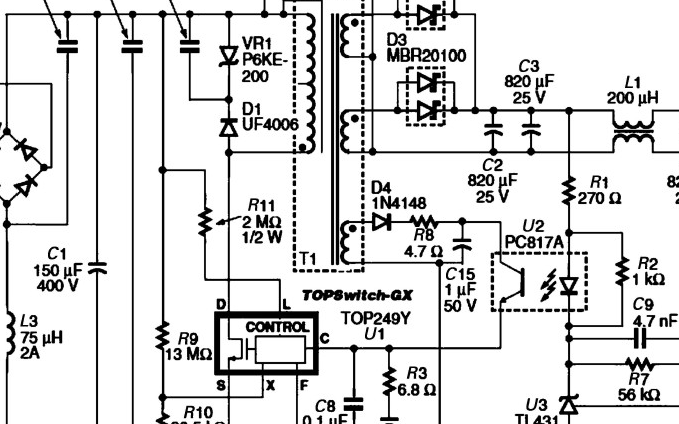

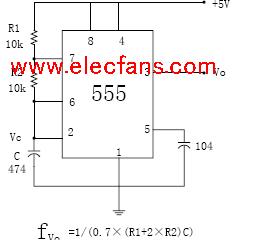

1. 555單穩(wěn)態(tài)觸發(fā)器

圖3.10 單穩(wěn)態(tài)觸發(fā)器電路圖

2008-09-22 11:31:17 3079

3079

555組成的單穩(wěn)態(tài)觸發(fā)器

2008-12-17 14:21:08 903

903

單穩(wěn)態(tài)延時(shí)觸發(fā)器

2009-04-08 08:49:26 610

610

555單穩(wěn)態(tài)觸發(fā)器電路圖

2009-05-16 16:46:26 1043

1043

555接成單穩(wěn)態(tài)觸發(fā)器電路圖

2009-05-16 16:46:51 1019

1019

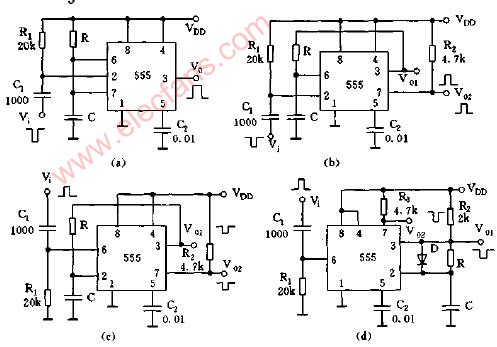

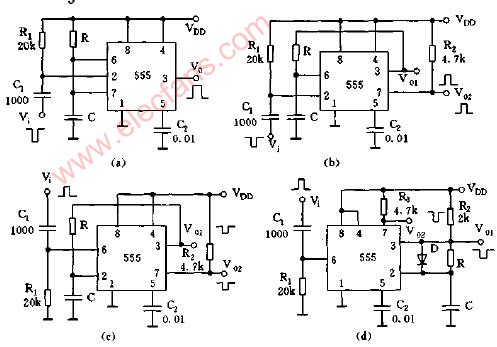

單穩(wěn)態(tài)觸發(fā)器的四種基本電路圖

2009-05-16 16:47:19 1637

1637

單穩(wěn)態(tài)觸發(fā)器電路圖

2009-05-16 16:47:43 800

800

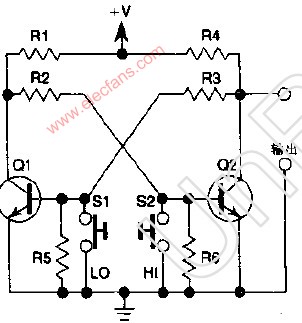

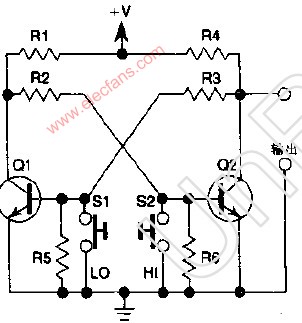

雙穩(wěn)態(tài)觸發(fā)器(按鍵觸發(fā)多諧振蕩器)

2009-09-28 11:35:44 1512

1512

觸發(fā)器的分類, 觸發(fā)器的電路

雙穩(wěn)態(tài)器件有兩類:一類是觸發(fā)器,一類是鎖存器。鎖存器是觸發(fā)器的原始形式。基本

2010-03-09 09:59:59 1554

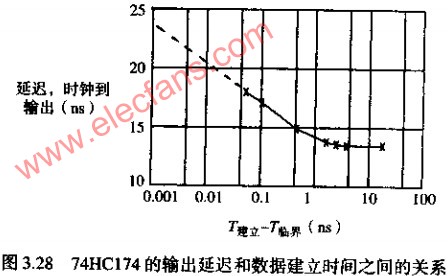

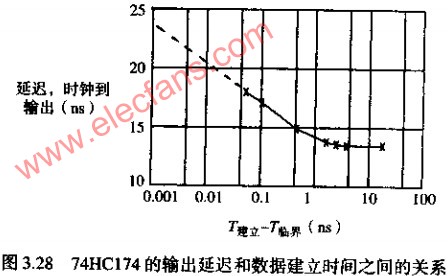

1554 圖3.27所示的是一個(gè)觀察D觸發(fā)器亞穩(wěn)態(tài)的電路圖。使用這個(gè)電路至少需要一個(gè)雙通道示波器。

2010-06-08 14:31:27 1088

1088

該文對(duì)單穩(wěn)態(tài)觸發(fā)器的工作特性作了簡(jiǎn)要的說(shuō)明,主要介紹了兩個(gè)具有代表性的工程應(yīng)用實(shí)例,結(jié)構(gòu)簡(jiǎn)單、易于實(shí)現(xiàn),可用于理論分析或投入實(shí)際操作

2011-09-23 17:54:01 80

80 555定時(shí)器構(gòu)成的單穩(wěn)態(tài)觸發(fā)器為基礎(chǔ)的測(cè)試電路根據(jù)雙向?qū)щ娫膶?dǎo)電原理,利用555 定時(shí)器構(gòu)成的單穩(wěn)態(tài)觸發(fā)器的觸發(fā)反應(yīng),驅(qū)動(dòng)蜂鳴器發(fā)聲,顯示測(cè)試結(jié)果。

2012-06-09 16:43:28 16518

16518

單穩(wěn)態(tài)觸發(fā)器仿真電路.ms8

2012-07-16 23:07:20 92

92 數(shù)字電路--觸發(fā)器雙穩(wěn)態(tài)觸發(fā)器

2016-12-20 17:32:40 0

0 單穩(wěn)態(tài)觸發(fā)器74123資料分享

2022-07-10 10:35:30 20

20 在進(jìn)行FPGA設(shè)計(jì)時(shí),往往只關(guān)心“0”和“1”兩種狀態(tài)。然而在工程實(shí)踐中,除了“0”、“1”外還有其他狀態(tài),亞穩(wěn)態(tài)就是其中之一。亞穩(wěn)態(tài)是指觸發(fā)器或鎖存器無(wú)法在某個(gè)規(guī)定時(shí)間段內(nèi)達(dá)到一個(gè)可確認(rèn)的狀態(tài)[1]。當(dāng)一個(gè)觸發(fā)器進(jìn)入亞穩(wěn)態(tài)時(shí),既無(wú)法預(yù)測(cè)該單元的輸出電平,也無(wú)法預(yù)測(cè)何時(shí)輸出才能穩(wěn)定在某個(gè)正確的電平上。

2019-10-06 09:42:00 908

908

亞穩(wěn)態(tài)是指觸發(fā)器無(wú)法在某個(gè)規(guī)定時(shí)間段內(nèi)達(dá)到一個(gè)可確認(rèn)的狀態(tài)。當(dāng)一個(gè)觸發(fā)器進(jìn)入亞穩(wěn)態(tài)時(shí),既無(wú)法預(yù)測(cè)該單元的輸出電平,也無(wú)法預(yù)測(cè)何時(shí)輸出才能穩(wěn)定在某個(gè)正確的電平上。在這個(gè)穩(wěn)定期間,觸發(fā)器輸出一些中間級(jí)電平.

2017-12-02 10:40:12 42902

42902

JK觸發(fā)器是數(shù)字電路觸發(fā)器中的一種基本電路單元。JK觸發(fā)器具有置0、置1、保持和翻轉(zhuǎn)功能,在各類集成觸發(fā)器中,JK觸發(fā)器的功能最為齊全。在實(shí)際應(yīng)用中,它不僅有很強(qiáng)的通用性,而且能靈活地轉(zhuǎn)換其他類型的觸發(fā)器。由JK觸發(fā)器可以構(gòu)成D觸發(fā)器和T觸發(fā)器。

2017-12-25 17:30:03 178011

178011

本文開始介紹了什么是單穩(wěn)態(tài)觸發(fā)器以及單穩(wěn)態(tài)觸發(fā)器的電路組成,其次闡述了單穩(wěn)態(tài)觸發(fā)器特點(diǎn)、門電路構(gòu)成的單穩(wěn)態(tài)觸發(fā)器、D觸發(fā)器構(gòu)成的單穩(wěn)態(tài)觸發(fā)器,最后詳細(xì)的闡述了時(shí)基電路構(gòu)成的單穩(wěn)態(tài)觸發(fā)器。

2018-03-27 09:24:23 71987

71987

本文開始介紹了單穩(wěn)態(tài)觸發(fā)器電路組成和單穩(wěn)態(tài)觸發(fā)器的四種基本電路圖,其次詳細(xì)闡述了單穩(wěn)態(tài)觸發(fā)器工作原理,最后介紹了單穩(wěn)態(tài)觸發(fā)器的作用。

2018-03-27 10:02:25 71864

71864

本文開始介紹了單穩(wěn)態(tài)觸發(fā)器的概念,其次闡述了單穩(wěn)態(tài)觸發(fā)器工作特點(diǎn)和單穩(wěn)態(tài)觸發(fā)器的用途,最后介紹了單穩(wěn)態(tài)觸發(fā)器的應(yīng)用。

2018-03-27 10:16:25 30508

30508

本文開始闡述了觸發(fā)器概念和觸發(fā)器作用,其次闡述了觸發(fā)器分類和觸發(fā)器優(yōu)點(diǎn),最后分析了觸發(fā)器有幾個(gè)穩(wěn)態(tài)。

2018-03-27 11:18:51 27564

27564 本文開始闡述了單穩(wěn)態(tài)觸發(fā)器工作特點(diǎn)和單穩(wěn)態(tài)觸發(fā)器的分類,其次闡述了單穩(wěn)態(tài)觸發(fā)器工作原理,最后介紹了常用的CD4098單穩(wěn)態(tài)觸發(fā)器。

2018-03-28 15:41:35 38999

38999

本文主要介紹了單穩(wěn)態(tài)觸發(fā)器芯片有哪些_單穩(wěn)態(tài)觸發(fā)器工作原理。單穩(wěn)態(tài)觸發(fā)器只有一個(gè)穩(wěn)定狀態(tài),一個(gè)暫穩(wěn)態(tài)。在外加脈沖的作用下,單穩(wěn)態(tài)觸發(fā)器可以從一個(gè)穩(wěn)定狀態(tài)翻轉(zhuǎn)到一個(gè)暫穩(wěn)態(tài)。由于電路中RC延時(shí)環(huán)節(jié)的作用

2018-03-28 18:22:32 27878

27878

本文主要介紹了雙穩(wěn)態(tài)觸發(fā)器的工作原理詳解。雙穩(wěn)態(tài)觸發(fā)器是脈沖和數(shù)字電路中常用的基本觸發(fā)器之一。雙穩(wěn)態(tài)觸發(fā)器的特點(diǎn)是具有兩個(gè)穩(wěn)定的狀態(tài),并且在外加觸發(fā)信號(hào)的作用下,可以由一種穩(wěn)定狀態(tài)轉(zhuǎn)換為另一種穩(wěn)定

2018-04-04 10:58:47 95398

95398

大家好,又到了每日學(xué)習(xí)的時(shí)間了,今天我們來(lái)聊一聊FPGA學(xué)習(xí)中,亞穩(wěn)態(tài)現(xiàn)象。 說(shuō)起亞穩(wěn)態(tài),首先我們先來(lái)了解一下什么叫做亞穩(wěn)態(tài)。亞穩(wěn)態(tài)現(xiàn)象:信號(hào)在無(wú)關(guān)信號(hào)或者異步時(shí)鐘域之間傳輸時(shí)導(dǎo)致數(shù)字器件失效的一種

2018-06-22 14:49:49 3222

3222

亞穩(wěn)態(tài)是指觸發(fā)器無(wú)法在某個(gè)規(guī)定時(shí)間段內(nèi)達(dá)到一個(gè)可確認(rèn)的狀態(tài)。

2018-09-22 08:25:00 8718

8718

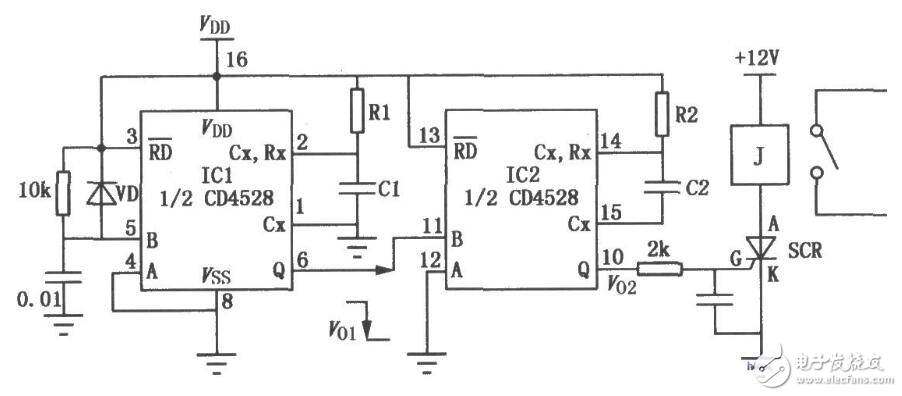

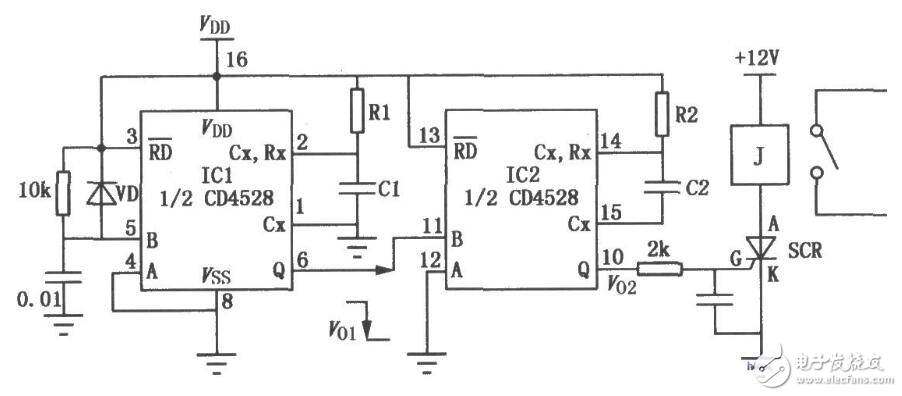

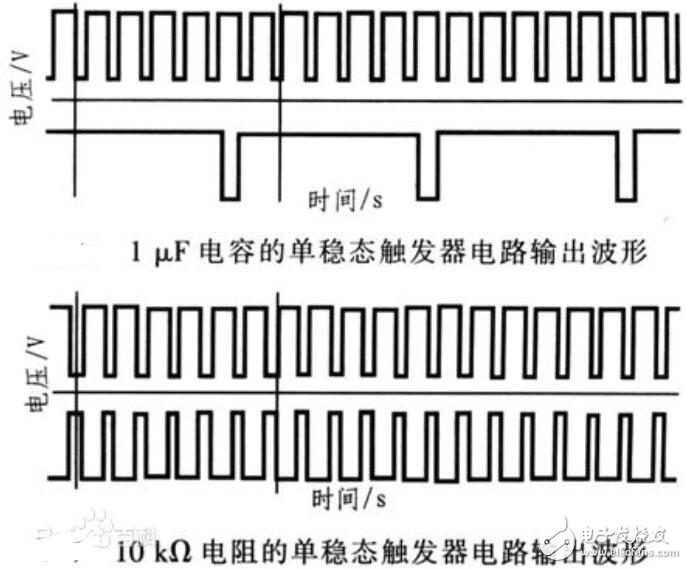

單穩(wěn)態(tài)觸發(fā)器CD4528組成的延時(shí)電路圖如下:?jiǎn)?b class="flag-6" style="color: red">穩(wěn)態(tài)觸發(fā)器電路處于穩(wěn)態(tài)時(shí),由于反相器D2輸入端經(jīng)R接+VDD,其輸出端為0,耦合至D1輸入端使D1輸出端為1,電容C兩端電位相等,無(wú)壓降。

2019-08-05 15:19:31 18291

18291

單穩(wěn)態(tài)觸發(fā)器只有一個(gè)穩(wěn)定狀態(tài),一個(gè)暫穩(wěn)態(tài)。在外加脈沖的作用下,單穩(wěn)態(tài)觸發(fā)器可以從一個(gè)穩(wěn)定狀態(tài)翻轉(zhuǎn)到一個(gè)暫穩(wěn)態(tài)。由于電路中RC延時(shí)環(huán)節(jié)的作用,該暫態(tài)維持一段時(shí)間又回到原來(lái)的穩(wěn)態(tài),暫穩(wěn)態(tài)維持的時(shí)間取決于RC的參數(shù)值。

2019-08-05 15:30:37 16109

16109

555守時(shí)器構(gòu)成的單穩(wěn)態(tài)觸發(fā)器原理圖如下:電路構(gòu)造與作業(yè)原理:

2020-09-25 11:23:51 8246

8246

亞穩(wěn)態(tài)概述 01亞穩(wěn)態(tài)發(fā)生原因 在 FPGA 系統(tǒng)中,如果數(shù)據(jù)傳輸中不滿足觸發(fā)器的 Tsu 和 Th 不滿足,或者復(fù)位過(guò)程中復(fù)位信號(hào)的釋放相對(duì)于有效時(shí)鐘沿的恢復(fù)時(shí)間(recovery time

2020-10-25 09:50:53 2196

2196

在同步系統(tǒng)中,如果觸發(fā)器的setup time / hold time不滿足,就可能產(chǎn)生亞穩(wěn)態(tài),此時(shí)觸發(fā)器輸出端Q在有效時(shí)鐘沿之后比較長(zhǎng)的一段時(shí)間處于不確定的狀態(tài),在這段時(shí)間里Q端毛刺、振蕩、固定的某一電壓值,而不是等于數(shù)據(jù)輸入端D的值。

2021-03-09 10:49:23 1321

1321

今天寫一下時(shí)序問(wèn)題常見(jiàn)的跨時(shí)鐘域的亞穩(wěn)態(tài)問(wèn)題。 先說(shuō)明一下亞穩(wěn)態(tài)問(wèn)題: D觸發(fā)器有個(gè)明顯的特征就是建立時(shí)間(setup time)和保持時(shí)間(hold time) 如果輸入信號(hào)在建立時(shí)間和保持時(shí)間

2021-06-18 15:28:22 2683

2683 亞穩(wěn)態(tài)的概念 亞穩(wěn)態(tài)是指觸發(fā)器無(wú)法在某個(gè)規(guī)定時(shí)間段內(nèi)達(dá)到一個(gè)可確認(rèn)的狀態(tài)。當(dāng)一個(gè)觸發(fā)器進(jìn)入亞穩(wěn)態(tài)引時(shí),既無(wú)法預(yù)測(cè)該單元的輸出電平,也無(wú)法預(yù)測(cè)何時(shí)輸出才能穩(wěn)定在某個(gè)正確的電平上。在這個(gè)穩(wěn)定期間,觸發(fā)器

2021-07-23 11:03:11 3928

3928

單穩(wěn)態(tài)觸發(fā)器只有一個(gè)穩(wěn)定狀態(tài),一個(gè)暫穩(wěn)態(tài)。在外加脈沖的作用下,單穩(wěn)態(tài)觸發(fā)器可以從一個(gè)穩(wěn)定狀態(tài)翻轉(zhuǎn)到一個(gè)暫穩(wěn)態(tài)。 ? 單穩(wěn)態(tài)觸發(fā)器工作原理 微分型單穩(wěn)態(tài)觸發(fā)器包含阻容元件構(gòu)成的微分電路。觸發(fā)器電路

2021-08-12 16:27:26 12953

12953 亞穩(wěn)態(tài)問(wèn)題是數(shù)字電路中很重要的問(wèn)題,因?yàn)楝F(xiàn)實(shí)世界是一個(gè)異步的世界,所以亞穩(wěn)態(tài)是無(wú)法避免的,并且亞穩(wěn)態(tài)應(yīng)該也是面試常考的考點(diǎn)。

2022-09-07 14:28:37 367

367 亞穩(wěn)態(tài)問(wèn)題是數(shù)字電路中很重要的問(wèn)題,因?yàn)楝F(xiàn)實(shí)世界是一個(gè)異步的世界,所以亞穩(wěn)態(tài)是無(wú)法避免的,并且亞穩(wěn)態(tài)應(yīng)該也是面試常考的考點(diǎn)。

2022-09-07 14:28:00 7116

7116 本系列整理數(shù)字系統(tǒng)設(shè)計(jì)的相關(guān)知識(shí)體系架構(gòu),為了方便后續(xù)自己查閱與求職準(zhǔn)備。對(duì)于FPGA和ASIC設(shè)計(jì)中,D觸發(fā)器是最常用的器件,也可以說(shuō)是時(shí)序邏輯的核心,本文根據(jù)個(gè)人的思考?xì)v程結(jié)合相關(guān)書籍內(nèi)容和網(wǎng)上文章,聊一聊D觸發(fā)器與亞穩(wěn)態(tài)的那些事。

2023-05-12 16:37:31 1345

1345

亞穩(wěn)態(tài)在電路設(shè)計(jì)中是常見(jiàn)的屬性現(xiàn)象,是指系統(tǒng)處于一種不穩(wěn)定的狀態(tài),雖然不是平衡狀態(tài),但可在短時(shí)間內(nèi)保持相對(duì)穩(wěn)定的狀態(tài)。對(duì)工程師來(lái)說(shuō),亞穩(wěn)態(tài)的存在可以帶來(lái)獨(dú)特的性質(zhì)和應(yīng)用,如非晶態(tài)材料、晶體缺陷

2023-05-18 11:03:22 2583

2583 本文主要介紹了亞穩(wěn)態(tài)的分析與處理。

2023-06-21 14:38:43 2073

2073

本系列整理數(shù)字系統(tǒng)設(shè)計(jì)的相關(guān)知識(shí)體系架構(gòu),為了方便后續(xù)自己查閱與求職準(zhǔn)備。對(duì)于FPGA和ASIC設(shè)計(jì)中,D觸發(fā)器是最常用的器件,也可以說(shuō)是時(shí)序邏輯的核心,本文根據(jù)個(gè)人的思考?xì)v程結(jié)合相關(guān)書籍內(nèi)容和網(wǎng)上文章,聊一聊D觸發(fā)器與亞穩(wěn)態(tài)的那些事。

2023-07-25 10:45:39 556

556

亞穩(wěn)態(tài)(Metastability)是由于輸入信號(hào)違反了觸發(fā)器的建立時(shí)間(Setup time)或保持時(shí)間(Hold time)而產(chǎn)生的。建立時(shí)間是指在時(shí)鐘上升沿到來(lái)前的一段時(shí)間,數(shù)據(jù)信號(hào)就要

2023-09-19 09:27:49 360

360

說(shuō)起亞穩(wěn)態(tài),首先我們先來(lái)了解一下什么叫做亞穩(wěn)態(tài)。亞穩(wěn)態(tài)現(xiàn)象:信號(hào)在無(wú)關(guān)信號(hào)或者異步時(shí)鐘域之間傳輸時(shí)導(dǎo)致數(shù)字器件失效的一種現(xiàn)象。

2023-09-19 15:18:05 1050

1050

RS觸發(fā)器是由兩個(gè)交叉連通的反相器(NOT門)和兩個(gè)邏輯門組成的,通常是由兩個(gè)與門(AND門)和一個(gè)非門(NOT門)構(gòu)成。而雙穩(wěn)態(tài)觸發(fā)器(也稱為D觸發(fā)器)是由一對(duì)互補(bǔ)輸出的鎖存器構(gòu)成,通常是由兩個(gè)與非門(NAND門)和一個(gè)非門(NOT門)構(gòu)成。

2023-09-26 16:11:50 893

893 兩級(jí)觸發(fā)器同步,就能消除亞穩(wěn)態(tài)嗎? 兩級(jí)觸發(fā)器同步可以幫助消除亞穩(wěn)態(tài)。本文將詳細(xì)解釋兩級(jí)觸發(fā)器同步原理、亞穩(wěn)態(tài)的定義和產(chǎn)生原因、以及兩級(jí)觸發(fā)器同步如何消除亞穩(wěn)態(tài)的機(jī)制。 1. 兩級(jí)觸發(fā)器同步

2024-01-16 16:29:38 252

252 施密特觸發(fā)器是一種常用的數(shù)字邏輯觸發(fā)器,具有兩個(gè)穩(wěn)態(tài)的特點(diǎn),即激勵(lì)信號(hào)超過(guò)一定閾值時(shí)觸發(fā),且在激勵(lì)信號(hào)低于另一閾值時(shí)復(fù)位。它由一個(gè)比較器和兩個(gè)正反饋網(wǎng)絡(luò)組成,具有較高的噪聲抑制能力和穩(wěn)態(tài)觸發(fā)特性

2024-02-04 09:53:12 657

657 單穩(wěn)態(tài)觸發(fā)器(也稱為單穩(wěn)態(tài)多譜儀或單穩(wěn)態(tài)穩(wěn)定器)是一種重要的數(shù)字電路元件,用于在輸入觸發(fā)信號(hào)的變化時(shí),產(chǎn)生一個(gè)確定時(shí)間寬度的穩(wěn)定的輸出脈沖。單穩(wěn)態(tài)觸發(fā)器在許多電子設(shè)備和系統(tǒng)中都有重要的應(yīng)用。本文

2024-02-05 10:54:51 367

367 單穩(wěn)態(tài)觸發(fā)器是一種基本的數(shù)字電路元件,具有兩個(gè)穩(wěn)態(tài)(穩(wěn)定狀態(tài)):穩(wěn)定低電位(低電平)和穩(wěn)定高電位(高電平)。當(dāng)輸入信號(hào)觸發(fā)器時(shí),觸發(fā)器會(huì)進(jìn)入暫態(tài)(暫態(tài))狀態(tài),即從一個(gè)穩(wěn)態(tài)過(guò)渡到另一個(gè)穩(wěn)態(tài)。單穩(wěn)態(tài)

2024-02-06 10:59:23 191

191 單穩(wěn)態(tài)觸發(fā)器是一種能夠在某個(gè)時(shí)間間隔內(nèi)將輸入信號(hào)的電平轉(zhuǎn)換為期望的輸出信號(hào)電平的數(shù)字電路。在單穩(wěn)態(tài)觸發(fā)器中,暫穩(wěn)態(tài)時(shí)間是指當(dāng)觸發(fā)器的輸入信號(hào)發(fā)生改變時(shí),觸發(fā)器在從暫穩(wěn)態(tài)過(guò)渡到穩(wěn)態(tài)所需的時(shí)間。 暫穩(wěn)態(tài)

2024-02-06 11:01:38 261

261 單穩(wěn)態(tài)觸發(fā)器的工作過(guò)程以及它可能的輸出狀態(tài)。 單穩(wěn)態(tài)觸發(fā)器是數(shù)字電路中最基本的多諧振蕩器之一,它在很多電路應(yīng)用中都有廣泛的應(yīng)用,例如數(shù)字脈沖發(fā)生器、脈沖寬度調(diào)制(PWM)電路等。 一、單穩(wěn)態(tài)觸發(fā)器的工作過(guò)程 單穩(wěn)態(tài)觸發(fā)器由兩個(gè)狀態(tài)組成:穩(wěn)定狀態(tài)和不

2024-02-06 11:16:11 259

259 D觸發(fā)器的穩(wěn)態(tài) D觸發(fā)器是數(shù)字電路中常用的一種存儲(chǔ)元件,它有兩種穩(wěn)態(tài),即低電平穩(wěn)態(tài)和高電平穩(wěn)態(tài)。當(dāng)輸入D為低電平時(shí),輸出Q保持為低電平;當(dāng)輸入D為高電平時(shí),輸出Q保持為高電平。 D觸發(fā)器和RS觸發(fā)器

2024-02-06 11:32:41 423

423 穩(wěn)態(tài)是指觸發(fā)器在某個(gè)特定的輸入狀態(tài)下穩(wěn)定保持輸出的狀態(tài)。根據(jù)觸發(fā)器的類型和觸發(fā)方式,觸發(fā)器分為很多種類,不同類型的觸發(fā)器有不同的穩(wěn)態(tài)。本文將詳細(xì)描述幾種常見(jiàn)的觸發(fā)器及其穩(wěn)態(tài),并介紹如何判斷觸發(fā)器

2024-02-06 13:36:55 367

367 觸發(fā)器是數(shù)字電路中常用的組合邏輯電路,在現(xiàn)代電子系統(tǒng)中有著廣泛的應(yīng)用。其中,最常用的兩種觸發(fā)器是T觸發(fā)器和JK觸發(fā)器。本文將詳細(xì)介紹T觸發(fā)器和JK觸發(fā)器的區(qū)別和聯(lián)系。 一、T觸發(fā)器 T觸發(fā)器是一種

2024-02-06 14:04:55 419

419 單穩(wěn)態(tài)觸發(fā)器是一種具有兩個(gè)穩(wěn)定狀態(tài)的觸發(fā)器,也稱為單穩(wěn)態(tài)多諧振蕩器(Monostable Multivibrator)或單穩(wěn)態(tài)脈沖發(fā)生器(Monostable Pulse Generator

2024-02-21 15:26:26 236

236

)中的VIN代入式(

)中的VIN代入式( )得到:

)得到:

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論