日前,德州儀器(TI)宣布推出全新系列的時鐘發生器,此次推出的產品可提供100飛秒(fs)的超低抖動以及靈活獨特的引腳控制選項。與傳統的參考時鐘解決方案相比,此次推出的新型時鐘發生器所具備的抖動性能可讓系統設計人員優化系統定時容限和誤碼率(BER),以減少數據傳輸錯誤。

2015-10-12 13:54:03 1258

1258 概述:MAX3625B是MAXIM公司生產的一款提供三路輸出的低抖動,高精度時鐘發生器。該MAX3625B是為網絡應用而優化的低抖動,高精度時鐘發生器。該器件集成一個晶體振蕩器和鎖相環(PLL)時鐘

2021-05-18 07:39:05

其它時鐘分配方法,其可降低整體抖動性能。您可使用如 LMK03806 等一款器件來克服這個問題,其在同一器件中整合了所有主時鐘發生器和時鐘分配功能(帶驅動器),如圖 1 所示。該器件可在 300MHz

2018-09-13 14:18:06

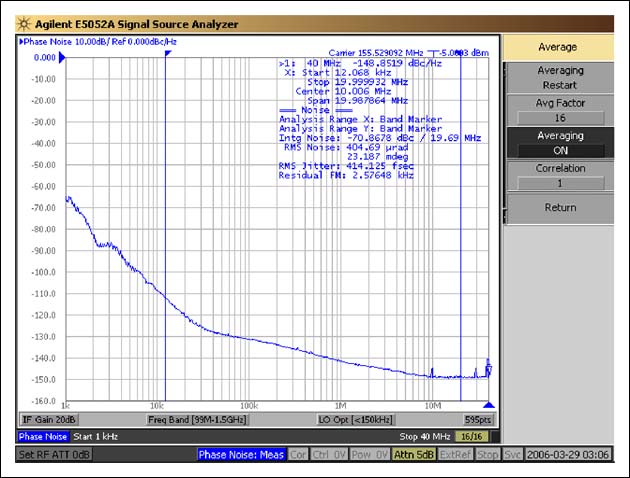

的時鐘發生器件的選擇上往往少有考慮。目前市場上有性能屬性大相徑庭的眾多時鐘發生器。然而,如果不慎重考慮時鐘發生器、相位噪聲和抖動性能,數據轉換器、動態范圍和線性度性能可能受到嚴重的影響。本文將詳細討論

2018-10-18 11:29:03

概述:AD9577是一款既提供一個多路輸出時鐘發生器功能,又帶有兩個片上鎖相環內核PLL1和PLL2,專門針對網絡時鐘應用而優化。PLL設計基于ADI公司成熟的高性能、低抖動頻率合成器產品系列,確保實現最高的網

2021-04-06 06:49:57

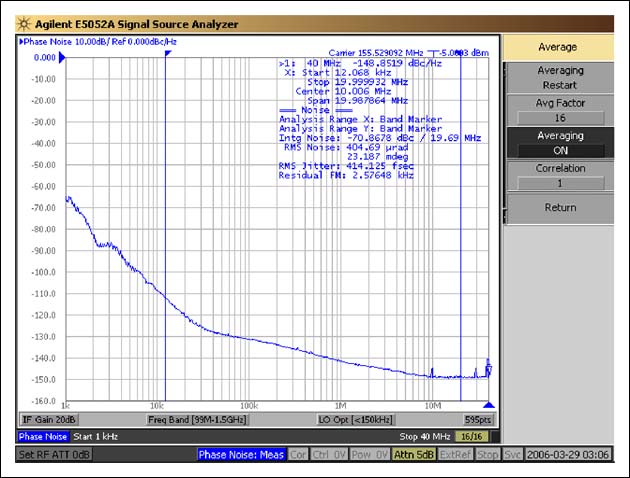

系統設計師通常側重于為應用選擇最合適的數據轉換器,在向數據轉換器提供輸入的時鐘發生器件的選擇上往往少有考慮。然而,如果不慎重考慮時鐘發生器的相位噪聲和抖動性能,數據轉換器動態范圍和線性度性能可能受到嚴重的影響。

2019-07-30 07:57:42

SNR 性能的影響以及怎樣降低一個噪聲時鐘源的抖動。作為基線,DC1826A-A 的時鐘輸入采用一個羅德與施瓦茨 SMB100A RF 發生器來驅動,并由 Stanford Research SR1 提供

2018-07-19 16:23:22

AD9520-1 / PCBZ,評估板是一款緊湊,易于使用的平臺,用于評估AD9520-1的所有功能。 AD9520-1是一款12 LVPECL / 24 CMOS輸出時鐘發生器,具有亞皮秒級抖動

2020-04-06 06:30:32

輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內集成鎖相環(PLL)和電壓控制振蕩器(VCO)。 產品名稱:時鐘發生器 AD9520-3BCPZ特征低相位噪聲、鎖相環(PLL)片內VCO的調諧頻率范圍為

2019-07-09 11:50:41

(LVDS工作模式) AD9571ACPZPEC產品詳情AD9571具有多路輸出時鐘發生器功能,內置專用PLL內核,針對以太網線路卡應用進行了優化。整數N PLL設計基于ADI公司成熟的高性能、低抖動

2019-07-09 10:19:09

AKD8140A Ver.2,AK8140??A可編程多時鐘發生器評估板。評估抖動性能和功能很容易

2020-07-27 15:01:46

本應用指南討論了CY2254 PLL時鐘發生器的內部結構,并提出一些使用建議。

2014-09-23 10:00:14

NB3N5573DTGEVB,用于SONET的NB3N5573 PLL時鐘發??生器評估板。 NB3N5573是一款高精度,低相位噪聲時鐘發生器,支持PCI Express和以太網要求

2019-08-30 08:41:47

NB4L339MNGEVB,GB以太網交換機時鐘發生器評估板。 NB4L339時鐘發生器評估板,方便有興趣進行自己的器件工程評估的客戶

2019-08-30 08:38:41

SI5324-EVB,SI5324評估板,0.002至710 MHz時鐘發生器。 SI5324-EVB為評估SI5316任意速率精度時鐘提供平臺。 SI5316直接使用器件上的配置引腳進行控制

2019-02-22 09:30:51

特征?單個3.3V電源?高性能時鐘發生器,包括集成頻率合成器的晶體振蕩器電路?低輸出抖動,低至380 fs(rms集成在10 kHz–20 MHz之間)?高頻下的低相位噪聲;在708 MHz時,在

2020-09-10 17:45:08

嗎?為什么PLL需要在不同的時鐘區域?時鐘發生器僅需要1個PLL和MMCM,不使用其他時鐘資源。我應該手動限制PLL嗎?這個怎么做?我在Kintex 7上有類似的設計,相同的時鐘發生器我沒有這個錯誤,我認為Kintex和Artix之間的時鐘資源相似

2020-07-20 12:51:25

專業銷售、維修、回收 高頻 二手儀器。 產品型號: CG635美國斯坦福時鐘發生器信息描述:時鐘可調頻由0.001Hz到2.05GHz少于1PS的RMS抖動可支持CMOS。PECL,ECL,LVDS

2020-08-18 09:08:58

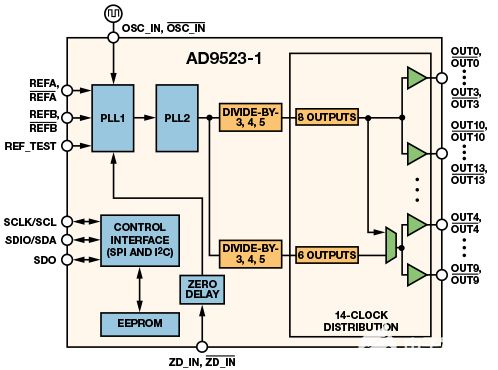

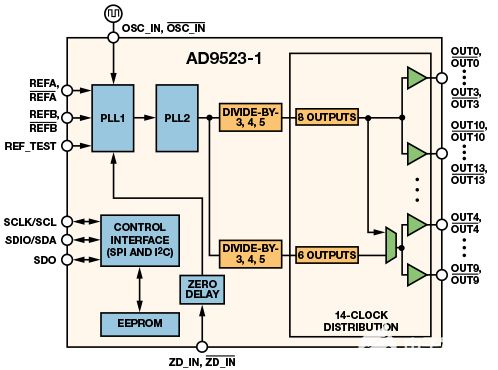

電路板面積,而且允許要求不同頻率的 多個器件以同一相位對齊源為時鐘源。AD9523, AD9523-1和 AD9524 時鐘發生器(如圖 1 所示)由 兩個串聯模擬PLL構成。第一個PLL (PLL

2019-10-31 08:00:00

SI5340-EVB,評估板用于評估Si5340低抖動任意頻率時鐘發生器。 Si5340采用獲得專利的Multisynth技術,可產生多達10個獨立時鐘頻率,每個頻率具有0 ppm的合成誤差

2019-02-26 09:28:56

SI5341-EVB,評估板用于評估Si5341低抖動任意頻率時鐘發生器。 Si5341采用獲得專利的Multisynth技術,可產生多達10個獨立時鐘頻率,每個頻率具有0 ppm的合成誤差

2019-02-25 07:03:01

我要做畢業設計 叫 基于lmk03806的高性能可編程時鐘發生器的設計與fpga實現,需要有protel 99se畫 lmk03806的原理圖和fpga的配置電路,用vhdl編程仿真,用fpga來配置lmk03806,求高手求助{:1:}

2013-05-03 23:06:27

找不到聯系方式,請在瀏覽器上搜索一下,旺貿通儀器儀 產品型號: CG635美國斯坦福時鐘發生器信息描述:時鐘可調頻由0.001Hz到2.05GHz少于1PS的RMS抖動可支持CMOS。PECL,ECL

2019-06-16 12:07:43

專業銷售、維修、回收 高頻 二手儀器。 產品型號: CG635美國斯坦福時鐘發生器信息描述:時鐘可調頻由0.001Hz到2.05GHz少于1PS的RMS抖動可支持CMOS。PECL,ECL,LVDS

2020-12-03 08:39:05

AD9523-1 / PCBZ,AD9523-1評估板旨在支持長期演進(LTE)和多載波GSM基站設計的時鐘要求。它依靠外部VCXO提供參考抖動清除,以實現可接受的數據轉換器SNR性能所需的限制性

2019-02-22 06:08:25

AD9525 / PCBZ-VCO,用于評估安裝了2950MHz VCO的AD9525的所有功能的評估板。 AD9525是一款低抖動時鐘發生器,具有正確的LVPECL輸出,旨在支持長期演進(LTE)和多載波GSM基站設計的轉換器時鐘要求

2019-02-26 09:38:38

AD9525 / PCBZ,用于AD9525時鐘發生器的評估板。 AD9525旨在支持長期演進(LTE)和多載波GSM基站設計的轉換器時鐘要求。 AD9525提供低功耗,多輸出,時鐘分配功能和低抖動

2019-02-25 08:38:34

AD9576 / PCBZ,AD9576評估板提供多輸出時鐘發生器功能,包括兩個專用鎖相環(PLL)內核,具有靈活的頻率轉換功能,經過優化,可作為整個系統的強大異步時鐘源,提供擴展功能通過監控和冗余

2019-02-25 09:40:01

SI52147-EVB,用于PoE無線接入點的時鐘發生器評估板。 Si52147是一款符合PCIe Gen1,Gen2和Gen3標準的9端口PCIe時鐘發生器

2020-08-27 14:27:11

?疑問3:是不是使用PLL類型的時鐘發生器芯片帶來的抖動誤差會比較大?針對14位的ADC輸入差分時鐘有此類型的參考嗎? 模擬輸入部分:疑問1:參考文檔中使用AD8138差分驅動芯片,計劃采用5v單電源模式

2018-11-07 09:35:54

噪聲抑制和出色的電源抑制比 (PSRR) 來幫助改進無錯數據傳輸。圖2顯示的是使用LMK03328時對PSRR和TX眼圖性能的改進,其原因就在于LMK03328集成了一個LDO。圖2:SAW示波器和TI LMK03328時鐘發生器的PSRR請在下方給我們留言,告訴我們你在正在研究的、最能從超低抖動中受益的應用。

2018-09-05 16:07:30

描述TIDA-00597 可為時鐘發生器提供噪聲非常低的輸出電源。主要特色低噪聲,適用于時鐘發生器輸出電流高達 800mA低相位噪聲輸出功率啟用和禁用

2018-08-22 07:43:40

~156.25MHz范圍的低抖動時鐘源。在理想的供電條件下,小數分頻PLL可在1 0kHz~20MHz頻段內提供低于lps RMS的抖動性能。相反,在有電源噪聲的環境中,振蕩器很難滿足其數據手冊中標明的相位抖動參數

2018-09-26 14:33:58

AC1571時鐘發生器一款基于PLL的、適用于5G基站應用的時鐘發生器。采用數字鎖相環技術,以實現最佳的高頻低相噪性能,具有低功耗和高PSRR能力。采用ADPLL技術,管腳兼容843N571,可以

2022-08-11 16:26:33

TIDA-00597 可為時鐘發生器提供噪聲非常低的輸出電源。

2009-05-07 15:12:41 0

0 HFAN-04.5.5評估電源噪聲抑制比對PLL時鐘合成器的影響

Characterizing Power-Supply Noise Rejection in PLL Clock

2009-06-19 07:35:38 50

50 具有單個 PLL 的超低抖動時鐘發生器系列 Function Ultra-low jitter clock generator Number of outputs 8

2022-12-02 13:47:16

具有兩個獨立 PLL 的超低抖動時鐘發生器系列 Function Ultra-low jitter clock generator Number of outputs 8

2022-12-02 13:47:17

汽車類 3.3V 雙路 PLL 多時鐘發生器 Function Clock generator Number of outputs 4 Output frequency

2022-12-02 13:47:21

8.192MHz 至 36.864MHz、并行控制、3.3V 雙路 PLL 多時鐘發生器 Function Clock generator Number of outputs 4

2022-12-02 13:47:44

4.096MHz 至 36.864MHz、串行控制、3.3V 雙路 PLL 多時鐘發生器 Function Clock generator Number of outputs 4

2022-12-02 13:47:45

3.3V 雙路 PLL 多時鐘發生器 Operating temperature range (C) -25 to 85 Rating Catalog 27-MHz

2022-12-02 13:47:45

8.192MHz 至 36.864MHz、串行控制、3.3V 雙路 PLL 多時鐘發生器 Function Clock generator Number of outputs 4

2022-12-02 13:47:45

AD9575是一款高度集成的雙路輸出時鐘發生器,包括一個針對網絡定時而優化的片內PLL內核。整數N分頻PLL設計基于ADI公司成熟的高性能、低抖動頻率合成器系列,可實現線路卡的較高性能。對相位噪聲

2023-02-13 10:25:49

AD9571具有多路輸出時鐘發生器功能,內置專用PLL內核,針對以太網線路卡應用進行了優化。整數N PLL設計基于ADI公司成熟的高性能、低抖動頻率合成器產品系列,確保實現較高的網絡性能。這款器件也

2023-02-13 10:29:31

AD9572是一款多輸出時鐘發生器,具有兩個片內PLL內核,針對包括以太網接口的光纖通道線路卡應用進行了優化。整數N分頻PLL設計基于ADI公司成熟的高性能、低抖動頻率合成器系列,可實現網絡的較高性能

2023-02-13 10:37:25

AD9573是一款高度集成的雙路輸出時鐘發生器 , 包括一個針對PCI-e應用而優化的片內PLL內核 。 整數N分頻PLL設計基于ADI公司成熟的高性能、低

2023-02-13 10:59:39

針對直接數字頻率合成(DDS)和集成鎖相環(PLL)技術的特性,提出了一種新的DDS 激勵PLL 系統頻率合成時鐘發生器方案。且DDS 避免正弦查找表,即避免使用ROM,采用濾波的方法

2009-12-14 10:22:00 36

36 MAX3625B是一款低抖動、精密時鐘發生器,優化用于網絡設備。器件內置晶體振蕩器和鎖相環(PLL)時鐘倍頻器,以產生高頻時鐘輸出,用于以太網、10G光纖通道及其它網絡設備。Ma

2010-03-01 08:54:52 126

126 AC1571 是用于 5G 基站應用的基于 PLL的時鐘發生器,該芯片采用全數字鎖相環技術,以實現最佳的高頻低相噪性能,并具有低功耗和高PSRR能力。典型應用場景:· 無線基站·

2023-12-12 14:25:17

時鐘發生器芯片廠家 時鐘芯片是一種基于PLL的時鐘發生器,采用ADPLL(全數字鎖相環)技術,以實現的高頻低相噪性能,并具備低功耗和高PSNR能力,可實現小于0.3ps RMS的相位抖動性能

2023-12-29 09:29:50

時鐘發生器芯片廠家 時鐘芯片是一種基于PLL的時鐘發生器,采用ADPLL(全數字鎖相環)技術,以實現的高頻低相噪性能,并具備低功耗和高PSNR能力,可實現小于0.3ps RMS的相位抖動性能

2024-02-04 11:41:14

MAX9489/MAX9471多輸出時鐘發生器構建集成時鐘源

摘要:與典型的“本地”時鐘方案相比,集成的多輸出時鐘發生器有許多優勢。本文探討了集中時鐘發生器(如

2008-10-04 20:43:25 922

922

精密時鐘發生器電路圖

2009-03-25 09:35:22 1054

1054

摘要:MAX9450/MAX9451/MAX9452是集成了VCXO,具有相同PLL內核和三種不同輸出(LVPECL, HSTL,LVDS)的高精度時鐘發生器。MAX945x時鐘發生器具有四個主要的特點:集成VCXO,工作頻率范圍寬,PLL

2009-04-22 09:42:01 966

966

摘要:與典型的“本地”時鐘方案相比,集成的多輸出時鐘發生器有許多優勢。本文探討了集中時鐘發生器(如MAX9489和MAX9471)的優點,如:降低系統成本、良好的信號完整性、抑制干

2009-04-22 10:11:53 407

407

摘要:與典型的“本地”時鐘方案相比,集成的多輸出時鐘發生器有許多優勢。本文探討了集中時鐘發生器(如MAX9489和MAX9471)的優點,如:降低系統成本、良好的信號完整性、抑制干

2009-05-03 11:07:05 652

652

MAX3625A 低抖動、精密時鐘發生器,提供三路輸出

2009-08-13 13:01:27 828

828

MAX3624 低抖動、精密時鐘發生器,提供四路輸出

概述

MAX3624是一款低抖動精密

2009-09-18 08:56:41 682

682

Maxim推出高性能、三路輸出時鐘發生器MAX3625B

Maxim近日推出高性能、三路輸出時鐘發生器MAX3625B,適用于以太網和光纖通道網絡設備。器件采用低噪聲VCO和PLL架構,能夠

2009-12-14 17:25:04 1040

1040 MAX3625B 抖動僅為0.36ps的PLL時鐘發生器

概述

MAX3625B是一款低抖動、精密時鐘發生器,優化用于網絡設備。器件內置晶體振蕩器和鎖相環(PLL)

2010-03-01 08:56:18 1345

1345

MAX3679A高性能四路輸出時鐘發生器(Maxim)

Maxim推出用于以太網設備的高性能、四路輸出時鐘發生器MAX3679A。器件采用低噪聲

2010-04-14 16:51:49 778

778 DS1091L是一款低成本的時鐘發生器,輸出頻率由工廠預置到130kHz至66.6MHz,標稱精度為±0.25%。器件可產生中心抖動或降頻抖動擴頻輸出,具有引腳可選的抖動幅度和抖動速率。

2011-03-16 10:57:41 1036

1036

AD9523提供低功耗、多路輸出時鐘分配功能,具有低抖動 性能,還配有片內集成鎖相環(PLL)和電壓控制振蕩器 (VCO)。片內VCO的調諧頻率范圍為3.6 GHz至4.0 GHz。 AD9523旨在滿足長期演進(LTE)和

2011-04-11 15:36:28 50

50 德州儀器(TI)(紐約證券交易所代碼:TXN)今天宣布推出一款具有業界最佳抖動性能的高度集成的時鐘發生器。LMK03806可以幫助設計人員運用一個低成本晶體合成所需的時鐘頻率,從而

2011-10-08 11:36:42 812

812 MAX3636是一個高度靈活,高精度鎖相環(PLL)時鐘發生器為下一代網絡設備的要求低抖動時鐘發生器和強大的高速數據傳輸的分布進行了優化。

2011-10-11 11:15:22 1329

1329

雙環路時鐘發生器可清除抖動并提供多個高頻輸出

2016-01-04 17:41:13 0

0 系統設計師通常側重于為應用選擇最合適的數據轉換器,在向數據轉換器提供輸入的時鐘發生器件的選擇上往往少有考慮。然而,如果不慎重考慮時鐘發生器、相位噪聲和抖動性能,數據轉換器、動態范圍和線性度性能可能受到嚴重的影響。

2017-11-17 02:00:58 752

752

Microchip基于MEMS的時鐘發生器

2018-06-07 13:46:00 4534

4534

Microchip基于MEMS的時鐘發生器

2018-07-08 01:23:00 3933

3933 AD9523:14路LVPECL/LVDS/HSTL輸出 或29路LVCMOS輸出 低抖動時鐘發生器

2019-07-04 06:18:00 3603

3603 TI推出超低抖動時鐘發生器,以實現更可靠的電信基礎設施設備,設計人員可以優化系統性能,簡化設備配置并減少設計周期時間。

2019-08-09 15:10:28 1652

1652 系統設計師通常側重于為應用選擇最合適的數據轉換器,在向數據轉換器提供輸入的時鐘發生器件的選擇上往往少有考慮。

2019-08-07 17:51:43 6011

6011

系統設計師通常側重于為應用選擇最合適的數據轉換器,在向數據轉換器提供輸入的時鐘發生器件的選擇上往往少有考慮。然而,如果不慎重考慮時鐘發生器的相位噪聲和抖動性能,數據轉換器動態范圍和線性度性能可能受到嚴重的影響。

2020-11-22 11:34:38 2666

2666

AD9523-1:低抖動時鐘發生器,14路LVPECL/LVDS/HSTL輸出或29路LVCMOS輸出 數據手冊

2021-03-21 14:28:08 1

1 AD9525: 8路LVPECL輸出低抖動時鐘發生器

2021-03-21 15:00:20 0

0 AD9540:655 MHz低抖動時鐘發生器數據表

2021-03-22 19:57:57 0

0 ADF4360-9:集成壓控振蕩器數據表的時鐘發生器PLL

2021-04-14 14:10:44 0

0 HMC1031:0.1 MHz至500 MHz時鐘發生器,帶整數N PLL數據表

2021-04-23 20:15:29 6

6 AD9530:4 CML輸出、低抖動時鐘發生器,集成5.4 GHz壓控振蕩器數據表

2021-04-24 12:02:38 0

0 AD9551:多業務時鐘發生器數據表

2021-04-28 10:30:52 0

0 AN-1576:采用AD9958 500 MSPS DDS或AD9858 1 GSPS DDS和AD9515時鐘分配IC的高性能ADC的低抖動采樣時鐘發生器

2021-04-30 09:48:42 13

13 AD9573:PCI-Express時鐘發生器IC,PLL內核,分頻器,雙輸出數據表

2021-05-08 20:05:05 5

5 AD9575:網絡時鐘發生器,雙輸出數據表

2021-05-09 11:06:44 1

1 超低抖動時鐘發生器和分配器最大限度地提高數據轉換器的信噪比

2021-05-18 20:57:30 0

0 Cypress時鐘發生器應用在車輛、工業生產、消費品和網絡服務的EMI降低和非EMI降低時鐘發生器。 Cypress具有廣泛的時鐘發生器組合,兼容700MHz的頻率和不超過0.7PS的RMS相位抖動

2022-04-22 09:02:09 806

806 超低抖動時鐘發生器如何優化串行鏈路系統性能

2022-11-04 09:50:15 0

0 AD9523、AD9523-1和AD9524時鐘發生器(如圖1所示)由兩個串聯的模擬PLL組成。第一個PLL(PLL1)清除參考抖動,而第二個PLL(PLL2)產生高頻相位對齊輸出。PLL2 還可以產生高基頻,從中可以導出各種較低頻率。

2023-02-02 17:29:35 829

829

采用PLL的時鐘發生器廣泛用于網絡設備中,用于生成高精度和低抖動參考時鐘或保持同步網絡操作。大多數時鐘振蕩器使用理想、干凈的電源給出其抖動或相位噪聲規格。然而,在實際的系統環境中,電源可能會因板載開關電源或嘈雜的數字ASIC而受到干擾。為了在系統設計中實現最佳性能,了解這種干擾的影響非常重要。

2023-03-08 15:33:00 895

895

9ZXL1951D PCIe 時鐘發生器評估板用戶指南

2023-03-21 19:21:13 0

0 本文討論電源噪聲干擾對基于PLL的時鐘發生器的影響,并介紹幾種用于評估由此產生的確定性抖動(DJ)的測量技術。派生關系顯示了如何使用頻域雜散測量來評估時序抖動行為。實驗室臺架測試結果用于比較測量技術,并演示如何可靠地評估參考時鐘發生器的電源噪聲抑制(PSNR)性能。

2023-04-11 11:06:39 811

811

) 頻帶內和頻帶外 (VCO) 噪聲的影響。基準時鐘發生器的相位噪聲性能需要在PLL環路帶寬內和帶寬外都表現得很出色,以符合更加嚴格的抖動技術規格要求。

2023-04-17 10:37:30 357

357

9ZXL1951D PCIe 時鐘發生器評估板用戶指南

2023-07-07 19:19:11 0

0 時鐘發生器由哪些部分組成?鎖相環pll的特點是什么?如何用硬件配置pll? 時鐘發生器是指通過特定的電路設計產生適合各種電子設備使用的時鐘信號的器件。時鐘發生器由多個部分組成,其中最核心的是鎖相環

2023-10-13 17:39:50 443

443 時鐘發生器/PLL頻率合成器SOP-82~15V2MHz封裝:SOP-8

2022-08-19 15:57:46 3

3 的時鐘發生器件的選擇上往往少有考慮。目前市場上有性能屬性大相徑庭的眾多時鐘發生器。然而,如果不慎重考慮時鐘發生器、相位噪聲和抖動性能,數據轉換器、動態范圍和線性度性能可能受到嚴重的影響。...

2023-11-28 14:33:57 0

0 電子發燒友網站提供《FemtoClock2抖動衰減器和時鐘發生器RC325008A數據手冊.pdf》資料免費下載

2024-01-14 10:55:06 0

0 電子發燒友網站提供《毫微微時鐘網絡同步器、抖動衰減器和時鐘發生器RC32112A 數據表.pdf》資料免費下載

2024-01-31 10:09:17 0

0

電子發燒友App

電子發燒友App

評論