我們所知道的計算機(jī)系統(tǒng)是建立在網(wǎng)絡(luò)和存儲速度較慢,而CPU內(nèi)存的反應(yīng)速度較快基礎(chǔ)上的。多年來,設(shè)計人員為這些組件開發(fā)了相應(yīng)的語言和接口,需要多層軟件將內(nèi)存命令轉(zhuǎn)換為網(wǎng)絡(luò)和存儲命令,反之亦然。

到目前為止,CPU內(nèi)存對相對于網(wǎng)絡(luò)和存儲I / O的速度使得這些軟件層對系統(tǒng)性能的影響很小。

然而,隨著摩爾定律的發(fā)展,網(wǎng)絡(luò)和存儲技術(shù)正迅速趕上CPU內(nèi)存速度,現(xiàn)在幾代軟件層發(fā)揮的作用變得越來越重要。

在本文中,我們將Gen-Z結(jié)構(gòu)視為消除現(xiàn)有系統(tǒng)瓶頸的解決方案,并通過統(tǒng)一通信路徑并使用CPU內(nèi)存加載/存儲語言簡化軟件來顯著提高系統(tǒng)效率和性能。

邁向新的計算架構(gòu)

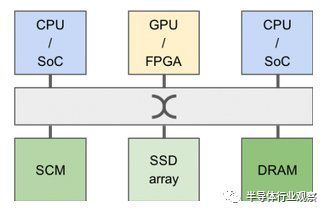

如圖1所示,計算架構(gòu)正在迅速發(fā)展為異構(gòu)系統(tǒng),包括多種計算單元(CPU / SoC,GPU,FPGA)和不同類型的內(nèi)存/存儲元件(DRAM,存儲器),在本地互連在一起或遠(yuǎn)程通信。

此類體系結(jié)構(gòu)應(yīng)通過允許添加或刪除資源,或在更新版本/技術(shù)可用時替換此類資源來提供更好的靈活性和可伸縮性。

圖1 - 新的計算架構(gòu)

以CPU為中心的方法

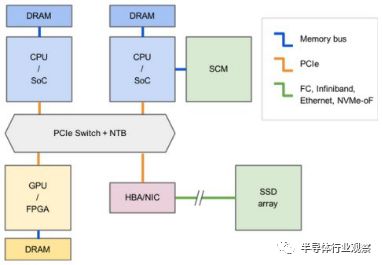

利用當(dāng)今以CPU內(nèi)存為中心的方法,圖1中的系統(tǒng)使用各種硅組件、接口和軟件層實現(xiàn),如圖2所示。

圖2 - 以CPU內(nèi)存為中心的系統(tǒng)架構(gòu)

在計算系統(tǒng)的這種特定實現(xiàn)中,PCI Express被用來連接CPU內(nèi)存、GPU / FPGA內(nèi)存和高性能/低延遲存儲器。SSD陣列通過主機(jī)總線適配器或NIC連接,使用光纖通道、Infiniband、NVMe-oF或以太網(wǎng)作為傳輸接口。

其中一個CPU的DRAM中的數(shù)據(jù)必須在到達(dá)SSD陣列之前遍歷4個接口域,隨后會產(chǎn)生相關(guān)的軟件開銷和緩沖區(qū)復(fù)制操作。

這里,可擴(kuò)展性是一個問題:升級到下一代SCM可能需要升級/更換相關(guān)的CPU / SoC。同樣,擴(kuò)展SSD陣列可能需要HBA / NIC下游的結(jié)構(gòu)交換機(jī)。

內(nèi)存語義方法

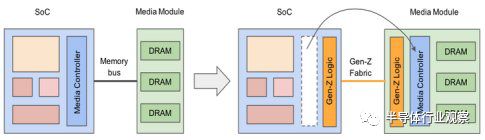

Gen-Z是一種內(nèi)存語義結(jié)構(gòu),它將CPU內(nèi)存字節(jié)可尋址的加載/存儲模型擴(kuò)展到整個系統(tǒng)。事實證明,加載/存儲模型是CPU與內(nèi)存子系統(tǒng)通信的最快、最有效的方法。為了啟用此模型,Gen-Z將計算與介質(zhì)分離,將介質(zhì)特定功能與其正確所屬的介質(zhì)放在一起。圖3說明了這個原理。

圖3 - 從CPU內(nèi)存接口到與介質(zhì)無關(guān)的結(jié)構(gòu)

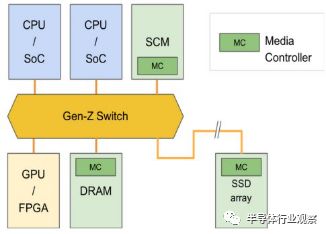

這一重要變化允許系統(tǒng)中的每個計算實體都是介質(zhì)不可知和分解的。使用Gen-Z內(nèi)存語義結(jié)構(gòu),可以使用交換拓?fù)鋵崿F(xiàn)圖1中的系統(tǒng),如圖4所示。

圖4 - 使用Gen-Z的系統(tǒng)架構(gòu)

通過這種方法,所有設(shè)備彼此對等并通過簡化的、高性能、低延遲的通信路徑說出相同的加載/存儲語言,而不會導(dǎo)致當(dāng)前總線體系結(jié)構(gòu)的轉(zhuǎn)換懲罰和軟件開銷。

Gen-Z協(xié)議定義了大量的內(nèi)存語義操作(通過OpCodes / OpClasses),可以實現(xiàn)高效的數(shù)據(jù)傳輸,以卸載計算資源,優(yōu)化互連使用并降低軟件開銷。在所示的示例中,可以使用適當(dāng)?shù)腛pCode / OpClass在一次加載和一次存儲操作中將來自DRAM的數(shù)據(jù)復(fù)制到SSD陣列。

在可擴(kuò)展性方面,系統(tǒng)可以通過獨(dú)立升級,添加或刪除計算,內(nèi)存或存儲元素而不影響功能,為每個工作負(fù)載和環(huán)境精確定制。

關(guān)于Gen-Z

Gen-Z架構(gòu)專注于提供高效率、高帶寬和低延遲。

通過利用經(jīng)過驗證的裝載/存儲模型實現(xiàn)高效率。簡化了Gen-Z硬件接口層,從而最大限度地減少了對軟件層的需求。消除這種復(fù)雜性、開銷和誘導(dǎo)系統(tǒng)延遲可以顯著提高系統(tǒng)性能。

高帶寬以兩種方式實現(xiàn)。Gen-Z支持非對稱通信路徑,這意味著可以將更多通道專用于讀取路徑而不是寫入路徑,反之亦然。此外,Gen-Z支持多種信令速率,包括16,25,32,56和112 GT / s。總而言之,這些功能將使Gen-Z能夠跟上行業(yè)不斷增長的速度需求,同時還允許將Gen-Z通信路徑調(diào)整為特定的工作負(fù)載流量模式。

通過減少軟件堆棧來實現(xiàn)低延遲。與傳統(tǒng)的服務(wù)器存儲和大量分層的網(wǎng)絡(luò)堆棧不同,Gen-Z采用輕量級軟件接口,直接對硬件進(jìn)行內(nèi)存讀寫操作。

芯片設(shè)計師需要的Gen-Z資源

希望成功開發(fā)Gen-Z產(chǎn)品的芯片設(shè)計師需要一些關(guān)鍵資源,具體如下:

Gen-Z控制器IP:SoC、交換機(jī)、存儲介質(zhì)控制器和其他類型的Gen-Z設(shè)備都需要可配置的高質(zhì)量控制器IP才能連接到Gen-Z結(jié)構(gòu)。在撰寫本文時,兩家IP供應(yīng)商,Gen-Z聯(lián)盟的成員已經(jīng)宣布了Gen-Z控制器IP的當(dāng)前和未來可用性。

Gen-Z PHY IP:初始Gen-Z實施將專注于經(jīng)過驗證的、部署的NRZ PHY信令技術(shù)和速度,利用16和32 GT / s的PCIe PHY和25 GT / s的IEEE802.3 PHY的可用性。后期部署可能會利用先進(jìn)的PAM4 PHY信令速率,如56和112 GT / s。

Gen-Z驗證IP:全面驗證IP(VIP)工具的可用性對于保證集成在SoC之前和之后Gen-Z IP的質(zhì)量至關(guān)重要。在撰寫本文時,兩家供應(yīng)商已宣布為Gen-Z提供驗證IP。

FPGA原型開發(fā)板:FPGA原型開發(fā)是確保系統(tǒng)級功能和互操作性的必要步驟。目前的FPGA技術(shù)允許Gen-Z原型設(shè)計高達(dá)56 GT / s(PAM4)和32 GT / s(NRZ)。還開發(fā)了連接器,以通過銅和光學(xué)連接以這些速率實現(xiàn)多通道Gen-Z信令。FPGA原型開發(fā)板可從多家供應(yīng)商處獲得,預(yù)計基于FPGA技術(shù)的Gen-Z特定原型開發(fā)平臺即將推出。

Gen-Z聯(lián)盟包括來自各個技術(shù)領(lǐng)域的成員,這對于構(gòu)建產(chǎn)品生態(tài)系統(tǒng)至關(guān)重要,其中所有必需的硬件和軟件組件彼此互操作。

結(jié)語

Gen-Z為計算機(jī)行業(yè)提供了一個獨(dú)特的機(jī)會,可以利用現(xiàn)有的CPU內(nèi)存重新定義現(xiàn)代計算并克服當(dāng)前的挑戰(zhàn)。隨著新公司繼續(xù)加入不斷發(fā)展的Gen-Z開放式生態(tài)系統(tǒng),構(gòu)建模塊、產(chǎn)品和服務(wù)的可用性自然會增加,并使新設(shè)計和產(chǎn)品能夠應(yīng)對新的工作負(fù)載和新出現(xiàn)的挑戰(zhàn)。

Gen-Z為創(chuàng)新的高性能、低延遲解決方案提供了機(jī)會,這些解決方案將是開放、簡單且經(jīng)濟(jì)、高效的。

-

數(shù)據(jù)傳輸

+關(guān)注

關(guān)注

9文章

2009瀏覽量

65814 -

網(wǎng)絡(luò)

+關(guān)注

關(guān)注

14文章

7783瀏覽量

90531 -

傳輸接口

+關(guān)注

關(guān)注

1文章

18瀏覽量

10485

發(fā)布評論請先 登錄

關(guān)于Gen-Z語義存儲(memory-semantic)體系架構(gòu)探討

如何創(chuàng)建最佳的網(wǎng)絡(luò)和架構(gòu) 一文解析Gen-Z架構(gòu)

EVAL-ADPD105Z-GEN信號是如何引入的,是否自帶發(fā)光管和接收管?

TE推出Sliver互連解決方案,具有高性能、靈活性、成本低等特點

關(guān)于Z軸TMR傳感器的性能介紹和應(yīng)用分析

關(guān)于MDT推Z軸TMR傳感器的性能分析和應(yīng)用介紹

關(guān)于USB 3.1 Gen 2 Type-C線纜配置和PVC護(hù)套的性能分析和介紹

處理器和加速器互聯(lián)的開發(fā)將得到進(jìn)一步發(fā)展

PCIe Gen 4協(xié)議分析儀的竟然那么強(qiáng)大!

最新PCIe Gen 5 switch芯片已內(nèi)置SerialTek PCIe抓包分析功能

iQOO Z6 Lite首發(fā)驍龍4 Gen 1處理器

高通驍龍8Gen3性能如何?

關(guān)于Gen-Z的性能和原理分析

關(guān)于Gen-Z的性能和原理分析

評論