本文主要分析一下在高速PCB設(shè)計(jì)中,高速信號(hào)與高速PCB設(shè)計(jì)存在一些理解誤區(qū)。

誤區(qū)一:GHz速率以上的信號(hào)才算高速信號(hào)?

提到“高速信號(hào)”,就需要先明確什么是“高速”,MHz速率級(jí)別的信號(hào)算高速、還是GHz速率級(jí)別的信號(hào)算高速?

傳統(tǒng)的SI理論對(duì)于“高速信號(hào)”有經(jīng)典的定義。

SI:Signal Integrity ,即信號(hào)完整性。

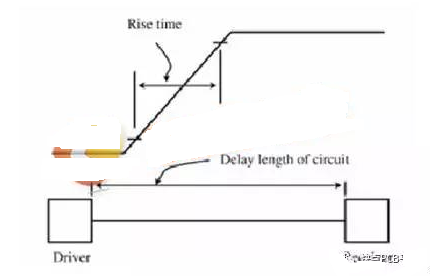

SI理論對(duì)于PCB互連線路的信號(hào)傳輸行為理解,信號(hào)邊沿速率幾乎完全決定了信號(hào)中的最大頻率成分,通常當(dāng)信號(hào)邊沿時(shí)間小于4~6倍的互連傳輸延時(shí)的情況下,信號(hào)互連路徑會(huì)被當(dāng)做分布參數(shù)模型處理,需要考慮SI行為。

所謂“高速”,是指“信號(hào)邊沿時(shí)間小于4~6倍的互連傳輸延時(shí)”,可以看出電路板傳輸?shù)男盘?hào)是否為“高速”,不只取決于信號(hào)的邊沿速率,還取決于電路板線路的路徑長(zhǎng)度大小,當(dāng)兩者存在一定的比例關(guān)系時(shí),該信號(hào)應(yīng)該按照“高速信號(hào)”進(jìn)行處理。

誤區(qū)二:有了仿真軟件平臺(tái)就可以做好高速PCB設(shè)計(jì)?

EDA設(shè)計(jì)軟件平臺(tái)集成了高速信號(hào)仿真功能,這對(duì)于高速PCB設(shè)計(jì)的規(guī)則制定與執(zhí)行,信號(hào)質(zhì)量仿真與評(píng)估都有很大的幫助。

但是,在PCB實(shí)際設(shè)計(jì)過程中,有時(shí)會(huì)出現(xiàn)仿真結(jié)果顯示信號(hào)質(zhì)量良好,但是實(shí)際測(cè)試時(shí)信號(hào)質(zhì)量很差,不滿足信號(hào)測(cè)試標(biāo)準(zhǔn),

實(shí)際上,仿真與測(cè)試是不可分的,拿IBIS模型為例,通常我們稱之為“行為級(jí)模型”,此類仿真模型也是通過芯片不同工作條件下的V、I測(cè)試曲線建立的,這就存在一個(gè)問題,仿真時(shí)如果不關(guān)注選取哪種工作條件下的芯片模型,就會(huì)仿真不準(zhǔn),例如:Slow、Typical、Fast。

從上面的例子可以看出,“仿真模型庫”對(duì)于仿真結(jié)果至關(guān)重要,必須通過實(shí)際產(chǎn)品項(xiàng)目的仿真測(cè)試實(shí)際對(duì)比、修正后的仿真模型才能算作“準(zhǔn)確的仿真模型”。

有了好的仿真設(shè)計(jì)平臺(tái)不能解決所有問題,還需要“準(zhǔn)確的仿真模型”,另外也要考慮到實(shí)際產(chǎn)品項(xiàng)目的應(yīng)用場(chǎng)景,仿真的某個(gè)信號(hào)網(wǎng)絡(luò),會(huì)受到電源噪聲、其他信號(hào)串?dāng)_等因素影響,這同樣會(huì)造成測(cè)試結(jié)果與仿真結(jié)果的差異。

誤區(qū)三:仿真軟件中的PCB走線“傳輸線模型”是非常準(zhǔn)確的?

仿真軟件中的PCB走線不管是微帶線還是帶狀線,都可以通過仿真工具建立模型,這個(gè)模型基于層疊和實(shí)際走線的尺寸,通常情況下可以滿足精度要求,但是如果說“非常準(zhǔn)確”,那還有一些差距,這需要從以下幾個(gè)方面分析:

(1)PCB銅皮的粗化/棕化處理加工工藝對(duì)信號(hào)質(zhì)量有影響

PCB加工過程中,為了提高PCB銅皮層與介質(zhì)層的結(jié)合強(qiáng)度,降低PCB分層風(fēng)險(xiǎn),都會(huì)有粗化/棕化處理工藝,就是通過打磨或者腐蝕的方式使銅皮表面變得粗糙。

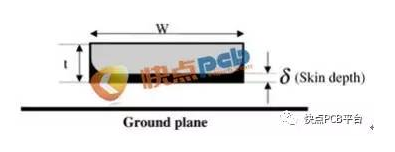

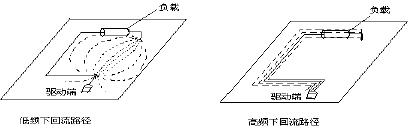

在高速信號(hào)在導(dǎo)體中的傳輸,存在“趨膚效應(yīng)”,是指高頻信號(hào)傳輸時(shí),在導(dǎo)體中流動(dòng)的電流將朝外圍或者導(dǎo)體的“表皮”遷移。

PCB銅皮表面粗糙,一方面影響損耗、另一方面也會(huì)影響信號(hào)傳輸延時(shí),這一點(diǎn)很好理解,就像汽車在崎嶇不堪的山路行駛時(shí)一定會(huì)比在柏油馬路上行駛更耗時(shí)。

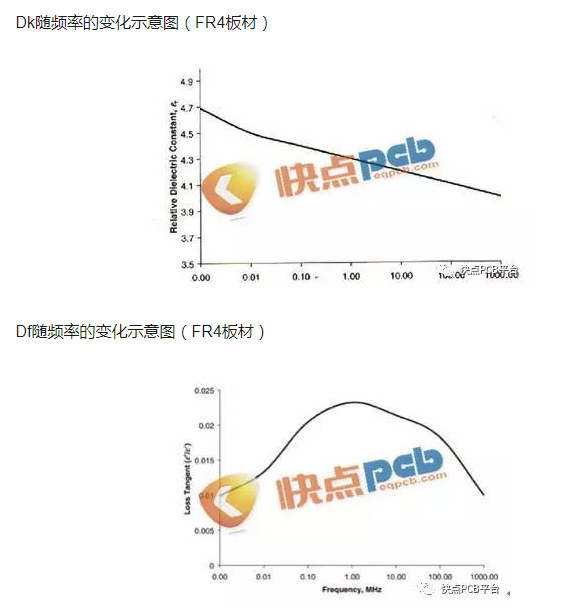

(2)PCB介質(zhì)的介電常數(shù)Dk、正切損耗角Df是隨著頻率變化的

仿真工具中的PCB介質(zhì)的Dk、Df通常為常數(shù),但是從信號(hào)實(shí)際傳輸?shù)慕嵌龋珼k/Df是隨著頻率變化的。

Dk/Df會(huì)隨著傳輸信號(hào)的速率變化,那么如果仿真工具中把這兩個(gè)參數(shù)作為常量處理,就會(huì)對(duì)傳輸線模型的仿真精度造成影響,信號(hào)傳輸速率越高這種影響就會(huì)越大。

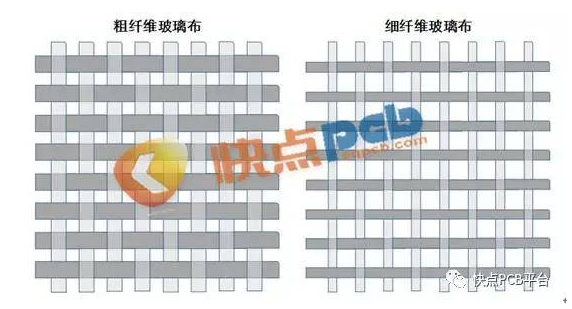

(3)PCB板材的“各向異性”影響

PCB板材通常是“環(huán)氧樹脂+玻璃布”的編織結(jié)構(gòu),玻璃布的排列方向分為“經(jīng)向”、“緯向”,同時(shí)根據(jù)玻璃纖維的粗細(xì)及間距,分成不同型號(hào)的PCB板材,如:1080、2116等。當(dāng)PCB板材采用不同類型玻璃布時(shí),玻璃布與樹脂在板材中的成分比例是不同的。

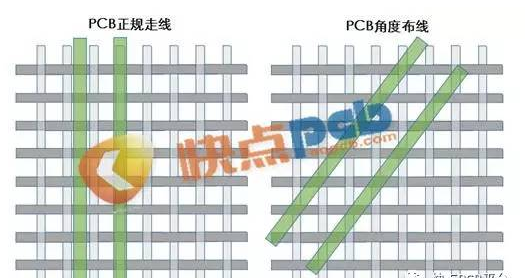

玻璃布與樹脂材料的Dk/Df值相差比較大,當(dāng)PCB正常走線與玻璃布的相對(duì)位置出現(xiàn)差異時(shí),就會(huì)導(dǎo)致參考介質(zhì)的Dk/Df值不同、信號(hào)的阻抗及損耗情況也會(huì)不同,如下圖所示,這也是為什么有些項(xiàng)目要求整板PCB走線方向要采用10°的原因。

誤區(qū)四:一種仿真軟件平臺(tái)可以搞定所有信號(hào)仿真問題

目前還沒有一個(gè)統(tǒng)一的仿真軟件平臺(tái)可以適用于所有信號(hào)仿真場(chǎng)景。行為級(jí)信號(hào)質(zhì)量仿真用Cadence SPB SigXplorer,晶體管級(jí)仿真用Synopsys HSPIe,三維電磁場(chǎng)建模用Ansoft HFSS,時(shí)域頻域混合仿真用Ansoft ADS。目前還沒有哪一款軟件可以一統(tǒng)江湖.

-

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

396文章

4794瀏覽量

90130 -

高速PCB

+關(guān)注

關(guān)注

4文章

102瀏覽量

25360 -

華強(qiáng)PCB

+關(guān)注

關(guān)注

8文章

1831瀏覽量

28561

發(fā)布評(píng)論請(qǐng)先 登錄

PCB設(shè)計(jì)高速模擬輸入信號(hào)走線方法及規(guī)則

高速pcb設(shè)計(jì)指南。

高速PCB設(shè)計(jì)之一 何為高速PCB設(shè)計(jì)

基于Cadence的高速PCB設(shè)計(jì)

高速PCB設(shè)計(jì)經(jīng)驗(yàn)與體會(huì)

高速PCB設(shè)計(jì)誤區(qū)與對(duì)策

高速PCB設(shè)計(jì)技巧有哪些

PCB設(shè)計(jì)中的高速信號(hào)傳輸優(yōu)化技巧

高速信號(hào)pcb設(shè)計(jì)中的布局

高速PCB設(shè)計(jì)中高速信號(hào)與高速PCB設(shè)計(jì)須知

高速PCB設(shè)計(jì)中高速信號(hào)與高速PCB設(shè)計(jì)須知

評(píng)論