1553B 總線控制器是國防電子系統的“中樞神經”,在過去的 50 年中,1553B 總線以其高可靠性、確定性等優點實現了傳感器等電子設備的信息共享和傳輸,并已被廣泛應用于國防及工業控制領域,成為聯合式國防電子系統的典型代表[1]。

目前,使用最為廣泛的是 DDC 公司生產的 BU-65170 系列電路[2-6]。該電路每次上電都需要微處理器對其配置寄存器和存儲器進行初始化,對于只需數據采集的簡單遠程終端系統(RT)來說,增加了系統的設計復雜度、體積、功耗。隨著國防電子系統傳感器日趨復雜,如何在不改變系統功能的前提下,最大程度地對系統簡化便成為首要任務。DDC 據此需求研制出了 1553B SSRT(Simple System Remote Terminal)系列控制電路 BU64703。

1 BU64703 功能特點

BU64703[7]是由美國 DDC 公司開發的一款全 3.3 V 供電,具備完全遠程終端(RT)功能,不需要處理器初始化配置,就可以進行遠程終端(RT)數據采集的一款 1553B 遠程終端控制電路。

BU64703 電路特點如下:(1)全 3.3 V 供電,完整的RT協議邏輯。(2)支持 1553A/B Notice2 協議。(3)內部集成 FIFO 支持消息突發。(4)16 位 DMA 接口。(5)上電自動配置功能。(6)內建自測試功能。可簡化 1553B 遠程終端 RT(不需要處理器初始化)。(8)時鐘 10 MHz、12 MHz、16 MHz 及 20 MHz 可選。(9)封裝形式 CQFP80。 BU 64703 電路內部功能框圖。

2 硬件設計

目前,1553B 協議電路使用最廣泛的是 DDC 公司 BU65170 系列(該電路為 5 V 供電),該電路的初始化工作需要由微處理器完成(主流的微處理器多為 3.3 V 供電),因此主流的 1553B 總線系統架構是:微處理器+譯碼邏輯電路+電平轉換電路+BU65170,系統較復雜。而有些 1553B 遠程終端(RT)節點因其體積結構或功能要求,其當前采集的數據不需要在本節點處理,而是轉發由總線控制節點(BC)處理。對于這種應用場景,本文提供了一種簡化系統的設計。

BU64703 是一款 3.3 V 供電,支持完整 RT 協議,專為簡化遠程終端(RT)系統設計的一款 1553B 控制電路,其可為 A/D、D/A 等器件直接提供 1553B 總線接口,從而降低終端系統復雜度、重量以及成本。本系統硬件設計方案,BU64703 工作于 16 位 DMA 接口工作模式。

選取了一路 A/D 電路作為本系統的數字信號輸入,即經 RT 采集的數據轉發給 BC;選取了一路 D/A 作為本系統的數字信號輸出,即將 BC 的控制信息傳遞給 RT。系統硬件主要由 CPLD 復雜可編程邏輯器件 EPM3128ATI100、1553B 總線控制器 BU64703、時鐘輸入 16 MHz(10/12/16/20MHz 可選),邏輯配置電路、復位控制電路 MAX706 等電路組成。

BU64703 電路 RT 地址總線 RTAD0~RTAD4、RTADP、數據總線 D0~D15、復位控制信號 MSTCLR、自動配置信號 AUTO_CFG、DMA 傳輸使能信號 DTGRT、非法化信號 ILLEGAL、存儲器寫信號 MEMWR、存儲器輸出使能信號 MEMOE、廣播模式信號 L_BRO、發送接收信號 T/R、子地址信號 SA4~SA0、數據個數信號 WC/CWC4-0、RT 節點正常信號 RTACVTIVE 和 DMA 握手信號 DTACK 等主要信號以及邏輯配置電路放入 CPLD 器件,TX/RXA 和 TX/RXB 通道與 1553B 總線隔離變壓器相連。BU64703 電路其他引腳主要信號配置如表 1 所示。

3 硬件實現

由于 BU64703 不需要處理器配置的特點,其電路的上電初始化、消息“非法化”、消息“忙”以及 BC 端發過來的消息都是通過 CPLD 中的 verilog 邏輯[8-11]實現的,本設計中這些功能的實現如下所述。

3.1 電路上電初始化

上電自動配置模塊的配置位,由 DMA 握手模塊從 D5~D0 端輸入完成設置,選擇配置工作狀態。上電初始化模塊硬件,通過使能自動配置信號 AUTO_CFG、使能DMA數據傳輸允許信號 DTGRT,將自動化配置位 6‘ b111111 與數據信號 D5~D0 連通。具體實現是將輸出 RTACTIVE 和 DTACK 信號做或邏輯,并將該邏輯信號作為自動化配置位 6’ b111111 輸入給數據線 D5 ~D0的使能信號,這樣就將配置數據6‘ b111111通過 DMA 的方式打入電路內部的配置位,從而實現初始化。

3.2 接收消息“非法化”

判斷接受消息是否非法方法如圖 3 所示:是通過 BU64703 輸出信號 L_BRO、T/R、SA4-SA0、WC/CWC4-0 在 CPLD 地址譯碼中進行組合邏輯運算完成的。并將運算結果交給 BU64703 的 ILLEGAL 信號從而實現“非法化”設置。

本設計使能兩種消息“合法”:(1)BC 到 RT 消息,子地址 1,數據個數為 1 的非廣播消息。(2)RT 到 BC 消息,子地址 1,數據字個數為 1 的非廣播消息“合法”,其余消息均“非法”。其 CPLD 中的對應的“非法化”邏輯為:ILLEGAL=((~L_BRO)&(~SA4)&(~SA3)&(~SA2)&(~SA1)&(SA0)&(~WC4)&(~WC3)&(~WC2)&(~WC1)&(WC0))。

3.3 接收消息“忙”

與接受消息“非法方法類似”,也是通過 BU64703 輸出信號 L_BRO、T/R、SA4-SA0、WC/CWC4-0 在 CPLD 地址譯碼中進行組合邏輯運算完成的。并將運算結果交給 BU64703 的 BUSY 信號從而實現“忙”設置。本設計使能兩種“不忙”消息:(1)BC 到 RT 消息,子地址 1,數據個數為 1 的非廣播消息。(2)RT 到 BC 消息,子地址 1,數據字個數為 1 的非廣播消息“不忙”;剩余消息均“忙”。其對應的邏輯為:BUSY=((~L_BRO)&(~SA4)&(~SA3)&(~SA2)&(~SA1)&(SA0)&(~WC4)&(~WC3)&(~WC2)&(~WC1)&(WC0))。

3.4 BC 命令的接收

本設計主要接收兩種消息:(1)BC 到 RT,子地址 1,數據字個數 1,其對應的外設是 D/A。(2)RT 到 BC,子地址 1,數據字個數 1,其對應得外設是 A/D。其 D/A 對應 LATCH 的使能信號 D/A_EN 也是由 BU64703 輸出信號 L_BRO、T/R、SA4-SA0、WC/CWC4-0 在 CPLD 地址譯碼中進行組合邏輯運算完成的。

其對應的邏輯為:D/A_EN=((~L_BRO)&(~T/R)&(~SA4)&(~SA3)&(~SA2)&(~SA1)&(SA0)&(~WC4)&(~WC3)&(~WC2)&(~WC1)&(WC0))。其 A/D 對應 LATCH 的使能信號 A/D_EN 也類似,對應邏輯為 A/D_EN=((~L_BRO)&(T/R)&(~SA4)&(~SA3)&(~SA2)&(~SA1)&(SA0)&(~WC4)&(~WC3)&(~WC2)&(~WC1)&(WC0)) 。

最后,BU64703 的國產化版本 B64703 已由國內科研院所研制成功[12]。B64703 芯片可以與 BU64703 實現 pin-to-pin 替換,經大量測試驗證,該芯片完全滿足國軍標 GJB289A-97[13] 和國軍標 GJB5186 的要求。目前,該電路已經大量應用于我國重點國防型號,實現了對國外同型號器件的替換,從而保證了升級后的簡化 1553B 遠程終端(RT)系統完全自主可控。

4 結語

本文主要闡述了 BU64703 電路的功能特點,并基于 CPLD 控制器完成遠程終端(RT)電路硬件設計實現。該系統外圍電路簡單,整個系統的集成性高,設計成本低且體積小,滿足體積要求較高的應用場合,特別適合只需進行數據采集而不需要進行數據處理的 1553B 總線遠程終端(RT)系統。BU64703 的國產化版本電路已經研制成功,標志著升級后的簡化 1553B 遠程終端(RT)系統完全自主可控。

責任編輯:pj

-

電路

+關注

關注

173文章

6026瀏覽量

174910 -

總線控制器

+關注

關注

0文章

31瀏覽量

12830

發布評論請先 登錄

電壓跟隨器的主要特點

Aigtek:功率放大器的主要特點介紹

光伏模擬器主要特點和應用

直流無刷電機的主要特點是什么?直流無刷電機具體可以組成哪些結構?

組合電器GIS的主要特點

與門的主要特點有哪些

DDR4 SDRAM控制器的主要特點

集成運放電路的主要特點有哪些

盛顯科技:超高分媒體處理器的主要特點有哪些?

集成運算放大器中間級的主要特點是什么

3GPP R16的主要特點

韓國裸機云大寬帶服務器主要特點和優勢

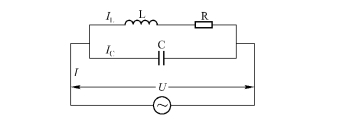

rlc串聯諧振電路的主要特點 RLC串聯諧振電路圖

電路交換的主要特點

電路交換的主要特點

評論