1,TTL電平:

輸出高電平》2.4V,輸出低電平《0.4V。在室溫下,一般輸出高電平是3.5V,輸出低電平是0.2V。最小輸入高電平和低電平:輸入高電平》=2.0V,輸入低電平《=0.8V,噪聲容限是0.4V。

2,CMOS電平:

1邏輯電平電壓接近于電源電壓,0邏輯電平接近于0V。而且具有很寬的噪聲容限。

3,電平轉(zhuǎn)換電路:

因?yàn)門TL和COMS的高低電平的值不一樣(ttl 5v《==》cmos 3.3v),所以互相連接時(shí)需要電平的轉(zhuǎn)換

4,OC門,即集電極開路門電路,OD門,即漏極開路門電路,必須外界上拉電阻和電源才能將開關(guān)電平作為高低電平用。否則它一般只作為開關(guān)大電壓和大電流負(fù)載,所以又叫做驅(qū)動(dòng)門電路。

5,TTL和COMS電路比較:

1)TTL電路是電流控制器件,而coms電路是電壓控制器件。

2)TTL電路的速度快,傳輸延遲時(shí)間短(5-10ns),但是功耗大。COMS電路的速度慢,傳輸延遲時(shí)間長(25-50ns),但功耗低。COMS電路本身的功耗與輸入信號(hào)的脈沖頻率有關(guān),頻率越高,芯片集越熱,這是正常現(xiàn)象。

3)COMS電路的鎖定效應(yīng):

COMS電路由于輸入太大的電流,內(nèi)部的電流急劇增大,除非切斷電源,電流一直在增大。這種效應(yīng)就是鎖定效應(yīng)。當(dāng)產(chǎn)生鎖定效應(yīng)時(shí),COMS的內(nèi)部電流能達(dá)到40mA以上,很容易燒毀芯片。

防御措施:

1)在輸入端和輸出端加鉗位電路,使輸入和輸出不超過規(guī)定電壓。

2)芯片的電源輸入端加去耦電路,防止VDD端出現(xiàn)瞬間的高壓。

3)在VDD和外電源之間加限流電阻,即使有大的電流也不讓它進(jìn)去。

4)當(dāng)系統(tǒng)由幾個(gè)電源分別供電時(shí),開關(guān)要按下列順序:開啟時(shí),先開啟COMS電路得電源,再開啟輸入信號(hào)和負(fù)載的電源;關(guān)閉時(shí),先關(guān)閉輸入信號(hào)和負(fù)載的電源,再關(guān)閉COMS電路的電源。

6,COMS電路的使用注意事項(xiàng)

1)COMS電路時(shí)電壓控制器件,它的輸入總抗很大,對干擾信號(hào)的捕捉能力很強(qiáng)。所以,不用的管腳不要懸空,要接上拉電阻或者下拉電阻,給它一個(gè)恒定的電平。

2)輸入端接低內(nèi)阻的信號(hào)源時(shí),要在輸入端和信號(hào)源之間要串聯(lián)限流電阻,使輸入的電流限制在1mA之內(nèi)。

3)當(dāng)接長信號(hào)傳輸線時(shí),在COMS電路端接匹配電阻。

4)當(dāng)輸入端接大電容時(shí),應(yīng)該在輸入端和電容間接保護(hù)電阻。電阻值為R=V0/1mA.V0是外界電容上的電壓。

5)COMS的輸入電流超過1mA,就有可能燒壞COMS。

7,TTL門電路中輸入端負(fù)載特性(輸入端帶電阻特殊情況的處理):

1)懸空時(shí)相當(dāng)于輸入端接高電平。因?yàn)檫@時(shí)可以看作是輸入端接一個(gè)無窮大的電阻。

2)在門電路輸入端串聯(lián)10K電阻后再輸入低電平,輸入端出呈現(xiàn)的是高電平而不是低電平。因?yàn)橛蒚TL門電路的輸入端負(fù)載特性可知,只有在輸入端接的串聯(lián)電阻小于910歐時(shí),它輸入來的低電平信號(hào)才能被門電路識(shí)別出來,串聯(lián)電阻再大的話輸入端就一直呈現(xiàn)高電平。這個(gè)一定要注意。COMS門電路就不用考慮這些了。

8,TTL電路有集電極開路OC門,MOS管也有和集電極對應(yīng)的漏極開路的OD門,它的輸出就叫做開漏輸出。OC門在截止時(shí)有漏電流輸出,那就是漏電流,為什么有漏電流呢?那是因?yàn)楫?dāng)三極管截止的時(shí)候,它的基極電流約等于0,但是并不是真正的為0,經(jīng)過三極管的集電極的電流也就不是真正的 0,而是約0。而這個(gè)就是漏電流。開漏輸出:OC門的輸出就是開漏輸出;OD門的輸出也是開漏輸出。它可以吸收很大的電流,但是不能向外輸出的電流。所以,為了能輸入和輸出電流,它使用的時(shí)候要跟電源和上拉電阻一齊用。OD門一般作為輸出緩沖/驅(qū)動(dòng)器、電平轉(zhuǎn)換器以及滿足吸收大負(fù)載電流的需要。

9,什么叫做圖騰柱,它與開漏電路有什么區(qū)別?

TTL集成電路中,輸出有接上拉三極管的輸出叫做圖騰柱輸出,沒有的叫做OC門。因?yàn)門TL就是一個(gè)三級(jí)關(guān),圖騰柱也就是兩個(gè)三級(jí)管推挽相連。所以推挽就是圖騰。一般圖騰式輸出,高電平400UA,低電平8MA

要了解邏輯電平的內(nèi)容,首先要知道以下幾個(gè)概念的含義:

1:輸入高電平(Vih): 保證邏輯門的輸入為高電平時(shí)所允許的最小輸入高電平,當(dāng)輸入電平高于Vih時(shí),則認(rèn)為輸入電平為高電平。

2:輸入低電平(Vil):保證邏輯門的輸入為低電平時(shí)所允許的最大輸入低電平,當(dāng)輸入電平低于Vil時(shí),則認(rèn)為輸入電平為低電平。

3:輸出高電平(Voh):保證邏輯門的輸出為高電平時(shí)的輸出電平的最小值,邏輯門的輸出為高電平時(shí)的電平值都必須大于此Voh。

4:輸出低電平(Vol):保證邏輯門的輸出為低電平時(shí)的輸出電平的最大值,邏輯門的輸出為低電平時(shí)的電平值都必須小于此Vol。

5:閥值電平(Vt):數(shù)字電路芯片都存在一個(gè)閾值電平,就是電路剛剛勉強(qiáng)能翻轉(zhuǎn)動(dòng)作時(shí)的電平。它是一個(gè)界于Vil、Vih之間的電壓值,對于CMOS電路的閾值電平,基本上是二分之一的電源電壓值,但要保證穩(wěn)定的輸出,則必須要求輸入高電平》 Vih,輸入低電平

對于一般的邏輯電平,以上參數(shù)的關(guān)系如下:

Voh 》 Vih 》 Vt 》 Vil 》 Vol。

6:Ioh:邏輯門輸出為高電平時(shí)的負(fù)載電流(為拉電流)。

7:Iol:邏輯門輸出為低電平時(shí)的負(fù)載電流(為灌電流)。

8:Iih:邏輯門輸入為高電平時(shí)的電流(為灌電流)。

9:Iil:邏輯門輸入為低電平時(shí)的電流(為拉電流)。

門電路輸出極在集成單元內(nèi)不接負(fù)載電阻而直接引出作為輸出端,這種形式的門稱為開路門。開路的TTL、CMOS、ECL門分別稱為集電極開路(OC)、漏極開路(OD)、發(fā)射極開路(OE),使用時(shí)應(yīng)審查是否接上拉電阻(OC、OD門)或下拉電阻(OE門),以及電阻阻值是否合適。對于集電極開路(OC)門,其上拉電阻阻值RL應(yīng)滿足下面條件:

(1):RL 《 (VCC-Voh)/(n*Ioh+m*Iih)

(2):RL 》 (VCC-Vol)/(Iol+m*Iil)

其中n:線與的開路門數(shù);m:被驅(qū)動(dòng)的輸入端數(shù)。

常用的邏輯電平

邏輯電平:有TTL、CMOS、LVTTL、ECL、PECL、GTL;RS232、RS422、LVDS等。

其中TTL和CMOS的邏輯電平按典型電壓可分為四類:5V系列(5V TTL和5V CMOS)、3.3V系列,2.5V系列和1.8V系列。

5V TTL和5V CMOS邏輯電平是通用的邏輯電平。

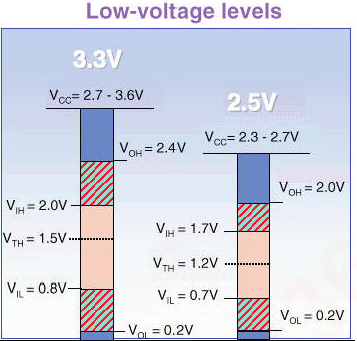

3.3V及以下的邏輯電平被稱為低電壓邏輯電平,常用的為LVTTL電平。

低電壓的邏輯電平還有2.5V和1.8V兩種。

ECL/PECL和LVDS是差分輸入輸出。

RS-422/485和RS-232是串口的接口標(biāo)準(zhǔn),RS-422/485是差分輸入輸出,RS-232是單端輸入輸出。

TTL和CMOS的邏輯電平關(guān)系

圖2-1:TTL和CMOS的邏輯電平圖

上圖為5V TTL邏輯電平、5V CMOS邏輯電平、LVTTL邏輯電平和LVCMOS邏輯電平的示意圖。

5V TTL邏輯電平和5V CMOS邏輯電平是很通用的邏輯電平,注意他們的輸入輸出電平差別較大,在互連時(shí)要特別注意。

另外5V CMOS器件的邏輯電平參數(shù)與供電電壓有一定關(guān)系,一般情況下,Voh≥Vcc-0.2V,Vih≥0.7Vcc;Vol≤0.1V,Vil≤0.3Vcc;噪聲容限較TTL電平高。

JEDEC組織在定義3.3V的邏輯電平標(biāo)準(zhǔn)時(shí),定義了LVTTL和LVCMOS邏輯電平標(biāo)準(zhǔn)。

LVTTL邏輯電平標(biāo)準(zhǔn)的輸入輸出電平與5V TTL邏輯電平標(biāo)準(zhǔn)的輸入輸出電平很接近,從而給它們之間的互連帶來了方便。LVTTL邏輯電平定義的工作電壓范圍是3.0-3.6V。

LVCMOS邏輯電平標(biāo)準(zhǔn)是從5V CMOS邏輯電平關(guān)注移植過來的,所以它的Vih、Vil和Voh、Vol與工作電壓有關(guān),其值如上圖所示。LVCMOS邏輯電平定義的工作電壓范圍是2.7-3.6V。

5V 的CMOS邏輯器件工作于3.3V時(shí),其輸入輸出邏輯電平即為LVCMOS邏輯電平,它的Vih大約為0.7×VCC=2.31V左右,由于此電平與 LVTTL的Voh(2.4V)之間的電壓差太小,使邏輯器件工作不穩(wěn)定性增加,所以一般不推薦使用5V CMOS器件工作于3.3V電壓的工作方式。由于相同的原因,使用LVCMOS輸入電平參數(shù)的3.3V邏輯器件也很少。

JEDEC組織為了加強(qiáng)在3.3V上各種邏輯器件的互連和3.3V與5V邏輯器件的互連,在參考LVCMOS和LVTTL邏輯電平標(biāo)準(zhǔn)的基礎(chǔ)上,又定義了一種標(biāo)準(zhǔn),其名稱即為3.3V邏輯電平標(biāo)準(zhǔn),其參數(shù)如下:

圖2-2:低電壓邏輯電平標(biāo)準(zhǔn)

從上圖可以看出,3.3V邏輯電平標(biāo)準(zhǔn)的參數(shù)其實(shí)和LVTTL邏輯電平標(biāo)準(zhǔn)的參數(shù)差別不大,只是它定義的Vol可以很低(0.2V),另外,它還定義了其 Voh最高可以到VCC-0.2V,所以3.3V邏輯電平標(biāo)準(zhǔn)可以包容LVCMOS的輸出電平。在實(shí)際使用當(dāng)中,對LVTTL標(biāo)準(zhǔn)和 3.3V邏輯電平標(biāo)準(zhǔn)并不太區(qū)分,某些地方用LVTTL電平標(biāo)準(zhǔn)來替代3.3V邏輯電平標(biāo)準(zhǔn),一般是可以的。

JEDEC組織還定義了2.5V邏輯電平標(biāo)準(zhǔn),如上圖所示。另外,還有一種2.5V CMOS邏輯電平標(biāo)準(zhǔn),它與上圖的2.5V邏輯電平標(biāo)準(zhǔn)差別不大,可兼容。

低電壓的邏輯電平還有1.8V、1.5V、1.2V的邏輯電平。

TTL和CMOS邏輯器件

邏輯器件的分類方法有很多,下面以邏輯器件的功能、工藝特點(diǎn)和邏輯電平等方法來進(jìn)行簡單描述。

TTL和CMOS器件的功能分類

按功能進(jìn)行劃分,邏輯器件可以大概分為以下幾類: 門電路和反相器、選擇器、譯碼器、計(jì)數(shù)器、寄存器、觸發(fā)器、鎖存器、緩沖驅(qū)動(dòng)器、收發(fā)器、總線開關(guān)、背板驅(qū)動(dòng)器等。

1:門電路和反相器

邏輯門主要有與門74X08、與非門74X00、或門74X32、或非門74X02、異或門74X86、反相器74X04等。

2:選擇器

選擇器主要有2-1、4-1、8-1選擇器74X157、74X153、74X151等。

3: 編/譯碼器

編/譯碼器主要有2/4、3/8和4/16譯碼器74X139、74X138、74X154等。

4:計(jì)數(shù)器

計(jì)數(shù)器主要有同步計(jì)數(shù)器74X161和異步計(jì)數(shù)器74X393等。

5:寄存器

寄存器主要有串-并移位寄存器74X164和并-串寄存器74X165等。

6:觸發(fā)器

觸發(fā)器主要有J-K觸發(fā)器、帶三態(tài)的D觸發(fā)器74X374、不帶三態(tài)的D觸發(fā)器74X74、施密特觸發(fā)器等。

7:鎖存器

鎖存器主要有D型鎖存器74X373、尋址鎖存器74X259等。

8:緩沖驅(qū)動(dòng)器

緩沖驅(qū)動(dòng)器主要有帶反向的緩沖驅(qū)動(dòng)器74X240和不帶反向的緩沖驅(qū)動(dòng)器74X244等。

9:收發(fā)器

收發(fā)器主要有寄存器收發(fā)器74X543、通用收發(fā)器74X245、總線收發(fā)器等。

10:總線開關(guān)

總線開關(guān)主要包括總線交換和通用總線器件等。

11:背板驅(qū)動(dòng)器

背板驅(qū)動(dòng)器主要包括TTL或LVTTL電平與GTL/GTL+(GTLP)或BTL之間的電平轉(zhuǎn)換器件。

TTL和CMOS邏輯器件的工藝分類特點(diǎn)

按工藝特點(diǎn)進(jìn)行劃分,邏輯器件可以分為Bipolar、CMOS、BiCMOS等工藝,其中包括器件系列有:

Bipolar(雙極)工藝的器件有:TTL、S、LS、AS、F、ALS。

CMOS工藝的器件有:HC、HCT、CD40000、ACL、FCT、LVC、LV、CBT、ALVC、AHC、AHCT、CBTLV、AVC、GTLP。

BiCMOS工藝的器件有:BCT、ABT、LVT、ALVT。

TTL和CMOS邏輯器件的電平分類特點(diǎn)

TTL和CMOS的電平主要有以下幾種:5VTTL、5VCMOS(Vih≥0.7*Vcc,Vil≤0.3*Vcc)、3.3V電平、2.5V電平等。

5V的邏輯器件

5V器件包含TTL、S、LS、ALS、AS、HCT、HC、BCT、74F、ACT、AC、AHCT、AHC、ABT等系列器件

3.3V及以下的邏輯器件

包含LV的和V 系列及AHC和AC系列,主要有LV、AHC、AC、ALB、LVC、ALVC、LVT等系列器件。

具體情況可以參考下圖:

圖3-1:TI公司的邏輯器件示例圖

包含特殊功能的邏輯器件

A.總線保持功能(Bus hold)

由內(nèi)部反饋電路保持輸入端最后的確定狀態(tài),防止因輸入端浮空的不確定而導(dǎo)致器件振蕩自激損壞;輸入端無需外接上拉或下拉電阻,節(jié)省PCB空間,降低了器件成本開銷和功耗,見圖6-3。ABT、LVT、ALVC、ALVCH、ALVTH、LVC、GTL系列器件有此功能。命名特征為附加了“H”如:74ABTH16244。

B.串聯(lián)阻尼電阻(series damping resistors)

輸出端加入串聯(lián)阻尼電阻可以限流,有助于降低信號(hào)上沖/下沖噪聲,消除線路振鈴,改善信號(hào)質(zhì)量。如圖6-4所示。具有此特征的ABT、LVC、LVT、 ALVC系列器件在命名中加入了“2”或“R”以示區(qū)別,如ABT162245,ALVCHR162245。對于單向驅(qū)動(dòng)器件,串聯(lián)電阻加在其輸出端,命名如SN74LVC2244;對于雙向的收發(fā)器件,串聯(lián)電阻加在兩邊的輸出端,命名如SN74LVCR2245。

C.上電/掉電三態(tài)(PU3S,Power up/power down 3-state)

即熱拔插性能。上電/掉電時(shí)器件輸出端為三態(tài),Vcc閥值為2.1V;應(yīng)用于熱拔插器件/板卡產(chǎn)品,確保拔插狀態(tài)時(shí)輸出數(shù)據(jù)的完整性。多數(shù)ABT、LVC、LVT、LVTH系列器件有此特征。

D.ABT 器件(Advanced BiCMOS Technology)

結(jié)合了CMOS器件(如HC/HCT、LV/LVC、ALVC、AHC/AHCT)的高輸入阻抗特性和雙極性器件(Bipolar,如TTL、LS、AS、ALS)輸出驅(qū)動(dòng)能力強(qiáng)的特點(diǎn)。包括ABT、LVT、ALVT等系列器件,應(yīng)用于低電壓,低靜態(tài)功耗環(huán)境。

E.Vcc/GND對稱分布

16位Widebus器件的重要特征,對稱配置引腳,有利于改善噪聲性能。AHC/AHCT、AVT、AC/ACT、CBT、LVT、ALVC、LVC、ALB系列16位Widebus器件有此特征。

F.分離軌器件(Split-rail)

即雙電源器件,具有兩種電源輸入引腳VccA和VccB,可分別接5V或3.3V電源電壓。如ALVC164245、LVC4245等,命名特征為附加了“4”。

邏輯器件的使用指南

1:多余不用輸入管腳的處理

在多數(shù)情況下,集成電路芯片的管腳不會(huì)全部被使用。例如74ABT16244系列器件最多可以使用16路I/O管腳,但實(shí)際上通常不會(huì)全部使用,這樣就會(huì)存在懸空端子。所有數(shù)字邏輯器件的無用端子必須連接到一個(gè)高電平或低電平,以防止電流漂移(具有總線保持功能的器件無需處理不用輸入管腳)。究竟上拉還是下拉由實(shí)際器件在何種方式下功耗最低確定。244、16244經(jīng)測試在接高電平時(shí)靜態(tài)功耗較小,而接地時(shí)靜態(tài)功耗較大,故建議其無用端子處理以通過電阻接電源為好,電阻值推薦為1~10K。

2:選擇板內(nèi)驅(qū)動(dòng)器件的驅(qū)動(dòng)能力,速度,不能盲目追求大驅(qū)動(dòng)能力和高速的器件,應(yīng)該選擇能夠滿足設(shè)計(jì)要求,同時(shí)有一定的余量的器件,這樣可以減少信號(hào)過沖,改善信號(hào)質(zhì)量。并且在設(shè)計(jì)時(shí)必須考慮信號(hào)匹配。

3:在對驅(qū)動(dòng)能力和速度要求較高的場合,如高速總線型信號(hào)線,可使用ABT、LVT系列。板間接口選擇ABT16244/245或LVTH16244 /245,并在母板兩端匹配,在不影響速度的條件下與母板接口盡量串阻,以抑制過沖、保護(hù)器件,典型電阻值為10- 200Ω左右,另外,也可以使用并接二級(jí)管來進(jìn)行處理,效果也不錯(cuò),如1N4148等(抗沖擊較好)。

4:在總線達(dá)到產(chǎn)生傳輸線效應(yīng)的長度后,應(yīng)考慮對傳輸線進(jìn)行匹配,一般采用的方式有始端匹配、終端匹配等。

始端匹配是在芯片的輸出端串接電阻,目的是防止信號(hào)畸變和地彈反射,特別當(dāng)總線要透過接插件時(shí),尤其須做始端匹配。內(nèi)部帶串聯(lián)阻尼電阻的器件相當(dāng)于始端匹配,由于其阻值固定,無法根據(jù)實(shí)際情況進(jìn)行調(diào)整,在多數(shù)場合對于改善信號(hào)質(zhì)量收效不大,故此不建議推薦使用。始端匹配推薦電阻值為10~51 Ω,在實(shí)際使用中可根據(jù)IBIS模型模擬仿真確定其具體值。

由于終端匹配網(wǎng)絡(luò)加重了總線負(fù)載,所以不應(yīng)該因?yàn)槠ヅ涠笲uffer的實(shí)際驅(qū)動(dòng)電流大于驅(qū)動(dòng)器件所能提供的最大Source、Sink電流值。

應(yīng)選擇正確的終端匹配網(wǎng)絡(luò),使總線即使在沒有任何驅(qū)動(dòng)源時(shí),其線電壓仍能保持在穩(wěn)定的高電平。

5:要注意高速驅(qū)動(dòng)器件的電源濾波。如ABT、LVT系列芯片在布線時(shí),建議在芯片的四組電源引腳附近分別接0.1 μ或0.01 μ電容。

6:可編程器件任何電源引腳、地線引腳均不能懸空;在每個(gè)可編程器件的電源和地間要并接0.1uF的去耦電容,去耦電容盡量靠近電源引腳,并與地形成盡可能小的環(huán)路。

7:收發(fā)總線需有上拉電阻或上下拉電阻,保證總線浮空時(shí)能處于一個(gè)有效電平,以減小功耗和干擾。

8:373/374/273等器件為工作可靠,鎖存時(shí)鐘輸入建議串入10-200歐電阻。

9:時(shí)鐘、復(fù)位等引腳輸入往往要求較高電平,必要時(shí)可上拉電阻。

10:注意不同系列器件是否有帶電插拔功能及應(yīng)用設(shè)計(jì)中的注意事項(xiàng),在設(shè)計(jì)帶電插拔電路時(shí)請參考公司的《單板帶電插拔設(shè)計(jì)規(guī)范》。

11:注意電平接口的兼容性。 選用器件時(shí)要注意電平信號(hào)類型,對于有不同邏輯電平互連的情況,請遵守本規(guī)范的相應(yīng)的章節(jié)的具體要求。

12: 在器件工作過程中,為保證器件安全運(yùn)行,器件引腳上的電壓及電流應(yīng)嚴(yán)格控制在器件手冊指定的范圍內(nèi)。邏輯器件的工作電壓不要超出它所允許的范圍。

13:邏輯器件的輸入信號(hào)不要超過它所能允許的電壓輸入范圍,不然可能會(huì)導(dǎo)致芯片性能下降甚至損壞邏輯器件。

14:對開關(guān)量輸入應(yīng)串電阻,以避免過壓損壞。

15:對于帶有緩沖器的器件不要用于線性電路,如放大器。

TTL、CMOS器件的互連

器件的互連總則

在公司產(chǎn)品的某些單板上,有時(shí)需要在某些邏輯電平的器件之間進(jìn)行互連。在不同邏輯電平器件之間進(jìn)行互連時(shí)主要考慮以下幾點(diǎn):

1:電平關(guān)系,必須保證在各自的電平范圍內(nèi)工作,否則,不能滿足正常邏輯功能,嚴(yán)重時(shí)會(huì)燒毀芯片。

2:驅(qū)動(dòng)能力,必須根據(jù)器件的特性參數(shù)仔細(xì)考慮,計(jì)算和試驗(yàn),否則很可能造成隱患,在電源波動(dòng),受到干擾時(shí)系統(tǒng)就會(huì)崩潰。

3:時(shí)延特性,在高速信號(hào)進(jìn)行邏輯電平轉(zhuǎn)換時(shí),會(huì)帶來較大的延時(shí),設(shè)計(jì)時(shí)一定要充分考慮其容限。

4:選用電平轉(zhuǎn)換邏輯芯片時(shí)應(yīng)慎重考慮,反復(fù)對比。通常邏輯電平轉(zhuǎn)換芯片為通用轉(zhuǎn)換芯片,可靠性高,設(shè)計(jì)方便,簡化了電路,但對于具體的設(shè)計(jì)電路一定要考慮以上三種情況,合理選用。

對于數(shù)字電路來說,各種器件所需的輸入電流、輸出驅(qū)動(dòng)電流不同,為了驅(qū)動(dòng)大電流器件、遠(yuǎn)距離傳輸、同時(shí)驅(qū)動(dòng)多個(gè)器件,都需要審查電流驅(qū)動(dòng)能力:輸出電流應(yīng)大于負(fù)載所需輸入電流;另一方面,TTL、CMOS、ECL等輸入、輸出電平標(biāo)準(zhǔn)不一致,同時(shí)采用上述多種器件時(shí)應(yīng)考慮電平之間的轉(zhuǎn)換問題。

我們在電路設(shè)計(jì)中經(jīng)常遇到不同的邏輯電平之間的互連,不同的互連方法對電路造成以下影響:

·對邏輯電平的影響。應(yīng)保證合格的噪聲容限(Vohmin-Vihmin≥0.4V,Vilmax-Volmax ≥0.4V),并且輸出電壓不超過輸入電壓允許范圍。

·對上升/下降時(shí)間的影響。應(yīng)保證Tplh和Tphl滿足電路時(shí)序關(guān)系的要求和EMC的要求。

·對電壓過沖的影響。過沖不應(yīng)超出器件允許電壓絕對最大值,否則有可能導(dǎo)致器件損壞。

TTL和CMOS的邏輯電平關(guān)系如上述圖所示: 圖2-1:TTL和CMOS的邏輯電平圖;圖2-2:低電壓邏輯電平標(biāo)準(zhǔn)

3.3V 的邏輯電平標(biāo)準(zhǔn)如前面所述有三種,實(shí)際的3.3V TTL/CMOS邏輯器件的輸入電平參數(shù)一般都使用LVTTL或3.3V邏輯電平標(biāo)準(zhǔn)(一般很少使用LVCMOS輸入電平),輸出電平參數(shù)在小電流負(fù)載時(shí)高低電平可分別接近電源電壓和地電平(類似LVCMOS輸出電平),在大電流負(fù)載時(shí)輸出電平參數(shù)則接近LVTTL電平參數(shù),所以輸出電平參數(shù)也可歸入 3.3V邏輯電平,另外,一些公司的手冊中將其歸納如LVTTL的輸出邏輯電平,也可以。

在下面討論邏輯電平的互連時(shí),對3.3V TTL/CMOS的邏輯電平,我們就指的是3.3V邏輯電平或LVTTL邏輯電平。

常用的TTL和CMOS邏輯電平分類有:5V TTL、5V CMOS、3.3V TTL/CMOS、3.3V/5V Tol.、和OC/OD門。

其中:

3.3V/5V Tol.是指輸入是3.3V邏輯電平,但可以忍受5V電壓的信號(hào)輸入。

3.3V TTL/CMOS邏輯電平表示不能輸入5V信號(hào)的邏輯電平,否則會(huì)出問題。

注意某些5V的CMOS邏輯器件,它也可以工作于3.3V的電壓,但它與真正的3.3V器件(是LVTTL邏輯電平)不同,比如其VIH是2.31V(=0.7×3.3V,工作于3.3V)(其實(shí)是LVCMOS邏輯輸入電平),而不是2.0V,因而與真正的3.3V器件互連時(shí)工作不太可靠,使用時(shí)要特別注意,在設(shè)計(jì)時(shí)最好不要采用這類工作方式。

值得注意的是有些器件有單獨(dú)的輸入或輸出電壓管腳,此管腳接3.3V的電壓時(shí),器件的輸入或輸出邏輯電平為3.3V的邏輯電平信號(hào),而當(dāng)它接5V電壓時(shí),輸入或輸出的邏輯電平為5V的邏輯電平信號(hào),此時(shí)應(yīng)該按該管腳上接的電壓的值來確定輸入和輸出的邏輯電平屬于哪種分類。

對于可編程器件(EPLD和FPGA)的互連也要根據(jù)器件本身的特點(diǎn)并參考上述內(nèi)容進(jìn)行處理。

以上5種邏輯電平類型之間的驅(qū)動(dòng)關(guān)系如下表:

上表中打鉤(√)的表示邏輯電平直接互連沒有問題,打星號(hào)(?/FONT》)的表示要做特別處理。

對于打星號(hào)(?/FONT》)的邏輯電平的互連情況,具體見后面說明。

一般對于高邏輯電平驅(qū)動(dòng)低邏輯電平的情況如簡單處理估計(jì)可以通過串接10-1K歐的電阻來實(shí)現(xiàn),具體阻值可以通過試驗(yàn)確定,如為可靠起見,可參考后面推薦的接法。

從上表可看出OC/OD輸出加上拉電阻可以驅(qū)動(dòng)所有邏輯電平,5V TTL和3.3V /5V Tol.可以被所有邏輯電平驅(qū)動(dòng)。所以如果您的可編程邏輯器件有富裕的管腳,優(yōu)先使用其OC/OD輸出加上拉電阻實(shí)現(xiàn)邏輯電平轉(zhuǎn)換;其次才用以下專門的邏輯器件轉(zhuǎn)換。

TI的AHCT系列器件為5V TTL輸入、5V CMOS輸出。

TI的LVC/LVT系列器件為TTL/CMOS邏輯電平輸入、3.3V TTL(LVTTL)輸出,也可以用雙軌器件替代。

注意:不是所有的LVC/LVT系列器件都能夠運(yùn)行5V TTL/CMOS輸入,一般只有帶后綴A的和LVCH/LVTH系列的可以,具體可以參考其器件手冊。

5V TTL門作驅(qū)動(dòng)源 :

·驅(qū)動(dòng)3.3V TTL/CMOS

通過LVC/LVT系列器件(為TTL/CMOS邏輯電平輸入,LVTTL邏輯電平輸出)進(jìn)行轉(zhuǎn)換。

·驅(qū)動(dòng)5V CMOS

可以使用上拉5V電阻的方式解決,或者使用AHCT系列器件(為5V TTL輸入、5V CMOS輸出)進(jìn)行轉(zhuǎn)換。

3.3V TTL/CMOS門作驅(qū)動(dòng)源 :

·驅(qū)動(dòng)5V CMOS

使用AHCT系列器件(為5V TTL輸入、5V CMOS輸出)進(jìn)行轉(zhuǎn)換(3.3V TTL電平(LVTTL)與5V TTL電平可以互連)。

5V CMOS門作驅(qū)動(dòng)源 :

·驅(qū)動(dòng)3.3V TTL/CMOS

通過LVC/LVT器件(輸入是TTL/CMOS邏輯電平,輸出是LVTTL邏輯電平)進(jìn)行轉(zhuǎn)換。

2.5V CMOS邏輯電平的互連

隨著芯片技術(shù)的發(fā)展,未來使用2.5V電壓的芯片和邏輯器件也會(huì)越來越多,這里簡單談一下2.5V邏輯電平與其他電平的互連,主要是談一下2.5V邏輯電平與3.3V邏輯電平的互連。(注意:對于某些芯片,由于采用了優(yōu)化設(shè)計(jì),它的2.5V管腳的邏輯電平可以和3.3V的邏輯電平互連,此時(shí)就不需要再進(jìn)行邏輯電平的轉(zhuǎn)換了。)

1:3.3V TTL/CMOS邏輯電平驅(qū)動(dòng)2.5V CMOS邏輯電平

2.5V 的邏輯器件有LV、LVC、AVC、ALVT、ALVC等系列,其中前面四種系列器件工作在2.5V時(shí)可以容忍3.3V的電平信號(hào)輸入,而ALVC不行,所以可以使用LV、LVC、AVC、ALVT系列器件來進(jìn)行3.3V TTL/CMOS邏輯電平到2.5V CMOS邏輯電平的轉(zhuǎn)換。

2:2.5V CMOS邏輯電平驅(qū)動(dòng)3.3V TTL/CMOS邏輯電平

2.5V CMOS邏輯電平的VOH為2.0V,而3.3V TTL/CMOS的邏輯電平的VIH也為2.0V,所以直接互連的話可能會(huì)出問題(除非3.3V的芯片本身的VIH參數(shù)明確降低了)。此時(shí)可以使用雙軌器件SN74LVCC3245A來進(jìn)行2.5V邏輯電平到3.3V邏輯電平的轉(zhuǎn)換,另外,使用OC/OD們加上拉電阻應(yīng)該也是可以的。

-

CMOS

+關(guān)注

關(guān)注

58文章

6005瀏覽量

238540 -

上拉電阻

+關(guān)注

關(guān)注

5文章

366瀏覽量

31114 -

電平

+關(guān)注

關(guān)注

5文章

367瀏覽量

40499

原文標(biāo)題:TTL電平和CMOS電平總結(jié)

文章出處:【微信號(hào):mcu168,微信公眾號(hào):硬件攻城獅】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評(píng)論請先 登錄

TTL電平和CMOS電平總結(jié)

TTL電平和CMOS電平總結(jié)

評(píng)論