毫無疑問,臺積電目前是晶圓代工市場的老大,其最新的5nm工藝已經量產,并且獨家拿下了蘋果A14處理器的訂單。不過,近兩年三星也在不斷的發力晶圓代工業務,不僅投入大筆資金建設先進的晶圓廠,同時也在工藝制程上加速的追趕。雖然,目前三星在市場份額上與臺積電有著很大的差距,但是技術上的差距正在縮小。去年,臺積電的創始人張忠謀在接受媒體采訪時也表示,“臺積電跟三星的戰爭絕對還沒結束,我們只是贏了一兩場battle(戰役),整個war(戰爭)還沒有贏。”

在2020世界人工智能大會期間的“萬物智聯·芯火燎原”人工智能芯片創新主題論壇上,三星電子高級副總裁Moonsoo Kang介紹了三星Foundry是如何通過提供最佳的Silicon(硅)解決方案來幫助AI芯片實現的。同時,他也介紹了三星Foundry在晶圓代工領域的概況及最新的進展。

▲Moonsoo Kang是Samsung Foundry市場戰略團隊負責人,負責與工藝技術、設計IP和封裝解決方案有關的Samsung Foundry的戰略規劃和路線圖

眾所周知,近年來人工智能技術發展迅猛,而對于人工智能來說,算力是極為重要的關鍵因素之一。而對于人工智能計算來說,最開始的載體是通用型CPU,因為其相對于AI計算來說,非常的靈活。但是隨著AI對于算力要求的越來越高,GPU開始成為了AI訓練的首選計算架構,因為其相比CPU來說,更加的高效。而現在,相比GPU更加高效的定制型AI芯片開始逐漸成為了AI計算架構的首選。

目前,CPU仍占據當今數據中心AI推理(Inference)應用市場的主導地位,同時在數據中心AI訓練應用市場,GPU則占據著主導地位。但是,根據研究機構的數據顯示,預計到到2025年,定制型AI芯片將占據數據中心AI推理應用市場40%的份額,在數據中心AI訓練應用市場,AI芯片的份額將達到50%。

在半導體芯片領域,我們可以看到的另一個趨勢則是,高端制程的邏輯工藝變得越來越昂貴,先進工藝的硅片制造成本越來越高,這也使得先進技術節點的芯片設計成本也隨之迅速增加。此外,并非采用先進的工藝,所有SoC內部的模塊都能以相同的方式體驗高級技術節點的好處。基于此,將傳統的SoC芯片分解成分為多個小芯片(Chiplet),每個小芯片可以根據不同的需求選擇不同的制程工藝,然后通過先進的封裝技術將其封裝在一起,這將使得芯片變得更加的高效和經濟。

基于這兩大趨勢,Samsung Foundry也針對性的提供了相應的工藝、IP和封裝技術來助力AI行業。

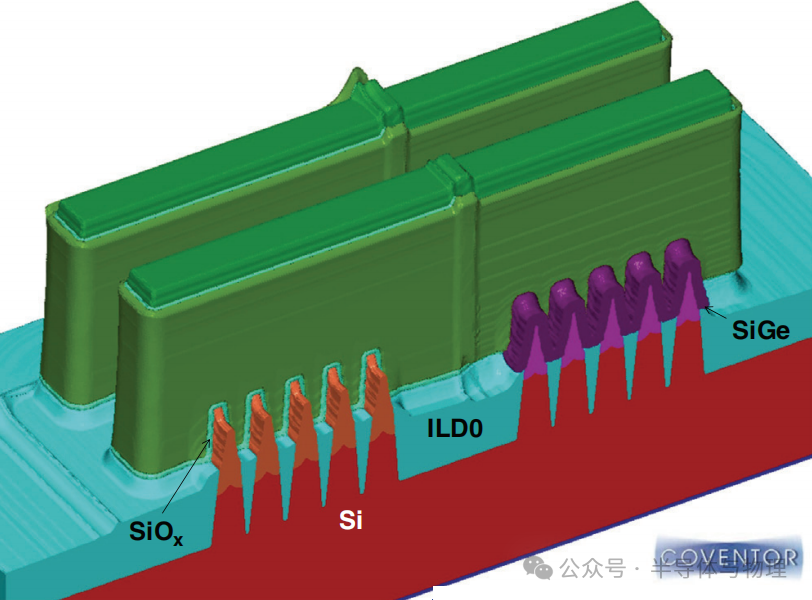

Moonsoo Kang首先介紹了Samsung Foundry在開發硅片先進制程技術方面的歷史。比如,在行業中率先在32/28nm工藝上引進了High-K金屬柵極技術;隨后又在Foundry行業中領先推出第一款采用FinFET晶體管結構的14nm工藝芯片;第一款基于EUV光罩技術的量產7nm芯片;三星還全球率先在3nm技術中引入全環柵極晶體管技術(Gate-all-around transistor,簡稱GAA)。

Moonsoo Kang表示,硅晶體管多年其就已從平面(Planar)演變到立體的FinFET,來實現更好的面積和電壓減縮,現在為了進一步改善并克服FinFET的短通道效應,Samsung Foundry引入了全環柵極的新型晶體管架構(GAA),借助這項新技術,可以進一步降低晶體管的工作電壓,從而實現更節能的計算,這對于AI應用至關重要。同樣,對于GAA器件,器件寬度會隨著納米片(Nano sheet)通道的垂直堆疊的增加而增加,因此可以實現性能提升的同時,而不會造成面積損失。這項技術可較小的硅片面積中實現更低的能耗和更多的計算能力,作為差別化的技術開發。

根據三星此前公布的數據顯示,三星電子已經成功攻克了3nm和1nm工藝所使用的GAA工藝技術,其將在2021年推出基于3nm GAA工藝,相比現有的7nm工藝來說,可實現芯片面積減少45%,功耗降低50%或性能提高35%,預計將于2022年開啟大規模量產。

此外,三星還擁有特殊工藝技術來提供差別化的解決方案。比如開發了28nm FD-SOI工藝,并提供了嵌入式非易失性存儲器解決方案,包括eFlash和eMRAM。并且三星還正在18nm節點上開發第二代FD-SOI技術。此外,三星還在FD-SOI工藝上提供eNVM解決方案,以實現最終的低功耗應用。

“我們的FD-SOI技術為節能解決方案提供了平臺,并且,借助嵌入式非易失性存儲器(如eFlash和eMRAM),有可能實現模擬類型的內存計算,與傳統的基于數字邏輯的計算架構相比,其功耗更低、面積更小、處理速度更快。”Moonsoo Kang介紹到。

但是,僅僅依靠先進的靠硅制程技術并不一定能提供出色的芯片,要制造出具有競爭力的芯片,還需要其他優秀的設計IP組合。

對此,Samsung Foundry提供了全套的設計IP來支持AI和HPC應用以及移動應用,比如,各種內存接口IP(例如HBM2/2e,GDDR6,DDR5/4和LPDDR5/4)、最高速度可達112G的Serdes IP、高速接口(例如PCIe,MIPI和USB)、Die-to-die接口串行和并行類型。

Moonsoo Kang表示,這些IP并非都是由我們的IP合作伙伴或Samsung Foundry內部開發,并經過所有測試和硅驗證的。

此外,封裝技術也是Samsung Foundry的技術解決方案的一部分。正如前面提到的,隨著異構整合、Chiplet的發展,先進封裝技術正成為推動芯片產業發展的關鍵技術。Samsung Foundry提供并繼續開發各種針對AI產品優化的封裝解決方案。

比如,可提供使用硅片和RDL中介層(interposer)連接邏輯和高帶寬存儲器,或邏輯和邏輯芯片的2.5D水平方向集成解決方案。該2.5D集成解決方案可從4個HBM集成進一步擴展到6和多于8個HBM集成。此外,Samsung Foundry還提供3D-TSV芯片堆疊集成解決方案,其中一個芯片位于另一個芯片的頂部,以實現極高的帶寬。隨著焊盤間距小至10um,3D集成解決方案將進一步擴展到晶圓對晶圓鍵合和芯片對晶圓技術。

對于AI芯片來說,性能尤為重要,但是功耗也是一個關鍵,尤其是對于耗電量巨大的數據中心類型的AI芯片而言。因此需要提供優秀的電源完整性(PI)解決方案。

隨著計算能力的提高,開關噪聲或功率紋波成為關鍵問題,作為一種解決方案,晶體管附近的高密度硅電容器可以減少電源噪聲并提高PI。Samsung Foundry提供了各種電容器解決方案來幫助增強PI,具有高電容密度的集成堆棧電容器(Integrated Stack Capacitor)可以集成在硅片中介層內部或作為分立芯片。集成的堆棧電容器可以顯著改善輸電網絡的峰值阻抗和電壓降(如下圖片所示)。還提Samsung Foundry供MIM(金屬絕緣體金屬)電容器和EPS(嵌入式無源基板),以進一步增強電源完整性。

以上,我們介紹了Samsung Foundry的硅工藝技術,設計IP和封裝技術,但是,這些技術組件不只是作為離散組件提供,它們是一個完整且客戶友好的生態系統,簡稱為SAFE(Samsung Advanced Foundry Ecosystem),可提供“一站式”解決方案。

Moonsoo Kang表示,百度的昆侖AI芯片就是采用了三星SAFE平臺,成功開發了出了同類最佳的AI芯片,該產品采用了Samsung Foundry的14nm邏輯工藝,SAFE可靠的IP解決方案和設計方法和HBM一起構建在2.5D硅片中介層PKG。

根據此前的資料顯示,百度昆侖AI芯片基于三星14nm工藝,支持PCIE 4.0*8,內建HBM內存、512GB/s內存帶寬,性能高達260TOPS,功耗僅150W。去年下半年百度昆侖AI芯片就已成功流片,目前已經成功量產,并應用于百度的智能云業務。

責任編輯:pj

-

芯片

+關注

關注

459文章

52416瀏覽量

439512 -

AI

+關注

關注

88文章

34918瀏覽量

278146 -

人工智能

+關注

關注

1806文章

48960瀏覽量

248593

發布評論請先 登錄

Cadence UCIe IP在Samsung Foundry的5nm汽車工藝上實現流片成功

多值電場型電壓選擇晶體管結構

nRF7002是我們獨特的Wi-Fi產品組合中的第一款設備

互補場效應晶體管的結構和作用

Samsung Foundry推出第一款采用FinFET晶體管結構的14nm工藝芯片

Samsung Foundry推出第一款采用FinFET晶體管結構的14nm工藝芯片

評論