一、簡介

RapidIO是由Motorola和Mercury等公司率先倡導的一種高性能、 低引腳數、 基于數據包交換的互連體系結構,是為滿足和未來高性能嵌入式系統需求而設計的一種開放式互連技術標準。RapidIO主要應用于嵌入式系統內部互連,支持芯片到芯片、板到板間的通訊,可作為嵌入式設備的背板(Backplane)連接。

RapidIO協議由邏輯層、傳輸層和物理層構成。邏輯層定義了所有協議和包格式。這是對終端進行初始化和完成傳送的很有必要的信息。傳輸層為數據包從一個終端到另一個終端通道的必要信息。物理層描述了設備之間接口協議,例如包傳裝置,流量控制,電特性及低級錯誤管理等。Rapid IO分為并行Rapid IO標準和串行Rapid IO標準,串行RapidIO是指物理層采用串行差分模擬信號傳輸的RapidIO標準。

RapidIO行業協會成立于2000年,其宗旨是為嵌入式系統開發可靠的、 高性能、 基于包交換的互連技術,2001 年正式發表其基本的規范。2003 年10 月,國際標準組織(ISO)和國際電工委員會(IEC)一致通過了RapidIO互連規范,即ISO/IEC DIS 18372,這使RapidIO(ISO)成為嵌入式互連技術方面得到授權的唯一標準。

RapidIO 的規范發布歷史如下:

2001年3月,發布RapidIO 1.1規范;

2002年6月,發布RapidIO 1.2規范;

2005年2月,發布RapidIO 1.3規范;

2007年6月,發布RapidIO 2.0規范;

2009年8月,發布RapidIO 2.1規范;

2011年5月,發布RapidIO 2.2規范。

RapidIO 1.x標準支持的信號速率為1.25GHz、2.5GHz和3.125GHz;RapidIO 2.x標準在兼容Rapid IO 1.x標準基礎上,增加了支持5GHz和6.25GHz的傳輸速率 。

RapidIO 已有超過10 年的歷史,仍然生機勃勃,它還在繼續為開發人員提供高速、先進的通訊技術:可對許多集成電路、板卡、背板及計算機系統供應商提供支持,支持RapidIO 標準的廠商有:Mercury Computer Systems、Freescale Semiconductor、Lucent-Alcatel、PMC-Sierra、Texas Instruments、Tundra Semiconductor、WindRiver、AMCC、Curtiss-Wright Controls、GE Fanuc 等,也就是說世界上幾乎所有的嵌入式主流廠商都已經支持RapidIO 技術,顯然,RapidIO 勢在必行。發展至今,開發人員有100 多種基于RapidIO 的產品可供選擇,這些產品涵蓋了各種開發工具、嵌入式系統、IP、軟件、測試與測量設備及半導體(ASIC、DSP、FPGA)等。

二、其他協議相比較

隨著高性能嵌入式系統的不斷發展,芯片間及板間互連對帶寬、成本、靈活性及可靠性的要求越來越高,傳統的互連方式,如處理器總線、PCI總線和以太網,都難以滿足新的需求 。

處理器總線主要用作外部存儲器接口,如德州儀器(TI) C6000系列DSP的外部存儲器接口,可支持外接同步SDRAM、SBSRAM及FIFO,也可支持異步SRAM、FLASH等。外部存儲器接口也可用作與板內FPGA或ASIC芯片互連,這種情況下,FPGA或ASIC模擬一個DSP支持的存儲器接口,DSP則把FPGA或ASIC當作存儲器來訪問。這類同步接口帶寬可達10Gbps,如德州儀器TMS320C6455 DSP的DDR2接口最大帶寬為17.066Gbps,SBSRAM接口最大帶寬為8.533Gbps。

然而,這種接口也存在一些局限性:

① 接口管腳多,硬件設計困難。常見的DDR2接口有70~80個管腳;

② 只能用于板內互連,無法用于板間互連;

③ 不是點對點的對等互連,DSP始終是主設備,其它器件只能做從設備。

PCI是廣泛用于計算機內器件互連的技術。傳統PCI技術也采樣類似于上述存儲器接口的并行總線方式,如TMS320C6455 DSP的PCI接口,有32bits數據總線,最高時鐘速度為66MHz,共有42個管腳。最新的串行PCI Express技術采用與串行RapidIO(SRIO, Serial RapidIO)類似的物理層傳輸技術,使得帶寬達到10Gbps左右。但由于其主要的應用仍是計算機,而且為了兼容傳統PCI技術,使得它在嵌入式設備方面的應用具有一定的局限性,如不支持點對點對等通信等。

眾所周知,以太網是使用最廣泛的局域網互連技術,它也被擴展應用到嵌入式設備互連,但它的局限性也是顯而易見的:

① 不支持硬件糾錯,軟件協議棧開銷較大;

② 打包效率低,有效傳輸帶寬因此而減小;

③ 只支持消息傳輸模式,不支持對對端設備的直接存儲器訪問(DMA, Direct Memory Access)。

針對嵌入式系統的需求以及傳統互連方式的局限性,RapidIO標準按如下目標被制定:

① 針對嵌入式系統機框內高速互連應用而設計。

② 簡化協議及流控機制,限制軟件復雜度,使得糾錯重傳機制乃至整個協議棧易于用硬件實現。

③ 提高打包效率,減小傳輸時延。

④ 減少管腳,降低成本。

⑤ 簡化交換芯片的實現,避免交換芯片中的包類型解析。

⑥ 分層協議結構,支持多種傳輸模式,支持多種物理層技術,靈活且易于擴展。

三、協議的三層結構

為了滿足靈活性和可擴展性的要求,RapidIO協議分為三層:邏輯層、傳輸層和物理層。

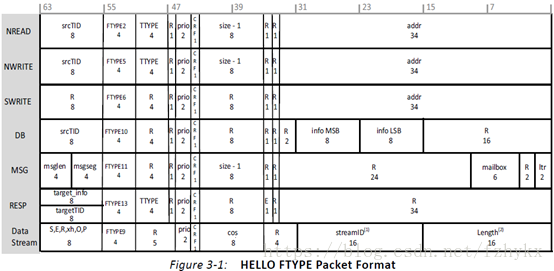

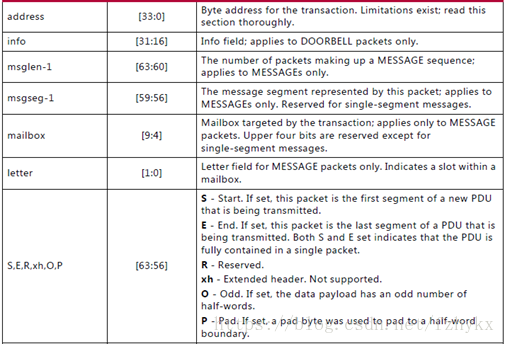

和以太網一樣,RapidIO也是基于包交換的互連技術。如圖3所示,RapidIO包由包頭、可選的載荷數據和16bits CRC校驗組成。包頭的長度因為包類型不同可能是十幾到二十幾個字節。每包的載荷數據長度不超過256字節,這有利于減少傳輸時延,簡化硬件實現。

上述包格式定義兼顧了包效率及組包/解包的簡單性。RapidIO交換器件僅需解析前后16bits,以及源/目地器件ID,這簡化了交換器件的實現。

邏輯層協議

邏輯層定義了操作協議和相應的包格式。RapidIO支持的邏輯層業務主要是:直接IO/DMA (Direct IO/Direct Memory Access)和消息傳遞(Message Passing)。

直接IO/DMA模式是最簡單實用的傳輸方式,其前提是主設備知道被訪問端的存儲器映射。在這種模式下,主設備可以直接讀寫從設備的存儲器。直接IO/DMA在被訪問端的功能往往完全由硬件實現,所以被訪問的器件不會有任何軟件負擔。從功能上講,這一特點和德州儀器DSP的傳統的主機接口(HPI, Host Port Interface)類似。但和HPI口相比,SRIO(Serial RapidIO)帶寬大,管腳少,傳輸方式更靈活。

對上層應用來說,發起直接IO/DMA傳輸主要需提供以下參數:目地器件ID、數據長度、數據在目地器件存儲器中的地址。

直接IO/DMA模式又可進一步分為以下幾種傳輸格式:

① NWRITE: 寫操作,不要求接收端響應。

② NWRITE_R: 帶響應的NWRITE(NWRITE with Response),要求接收端響應。

③ SWRITE:流寫(Stream Write),數據長度必須是8字節的整數倍,不要求接收端響應。

④ NREAD: 讀操作。

SWRITE是最高效的傳輸格式;帶響應的寫操作或讀操作效率則較低,一般只能達到不帶響應的傳輸的效率的一半。

消息傳遞(Message Passing)模式則類似于以太網的傳輸方式,它不要求主設備知道被訪問設備的存儲器狀況。數據在被訪問設備中的位置則由郵箱號(類似于以太網協議中的端口號)確定。從設備根據接收到的包的郵箱號把數據保存到對應的緩沖區,這一過程往往無法完全由硬件實現,而需要軟件協助,所以會帶來一些軟件負擔。

對上層應用來說,發起消息傳遞主要需提供以下參數:目地器件ID、數據長度、郵箱號。

傳輸層協議

RapidIO是基于包交換的互連技術,傳輸層定義了包交換的路由和尋址機制。

RapidIO網絡主要由兩種器件,終端器件(End Point)和交換器件(Switch)組成。終端器件是數據包的源或目的地,不同的終端器件以器件ID來區分。RapidIO支持8 bits 或 16 bits器件ID,因此一個RapidIO網絡最多可容納256或65536個終端器件。與以太網類似,RapidIO也支持廣播或組播,每個終端器件除了獨有的器件ID外,還可配置廣播或組播ID。交換器件根據包的目地器件ID進行包的轉發,交換器件本身沒有器件ID。

RapidIO的互連拓撲結構非常靈活,除了通過交換器件外,兩個終端器件也可直接互連。以德州儀器(TI)的TMS320C6455 DSP為例,它有4個3.125G的SRIO口,它可支持的拓撲結構

物理層協議

RapidIO 1.x 協議定義了以下兩種物理層接口標準:

① 8/16 并行LVDS協議

② 1x/4x 串行協議 (SRIO)

并行RapidIO由于信號線較多(40~76)難以得到廣泛的應用,而1x/4x串行RapidIO僅4或16個信號線,逐漸成為主流,所以本文僅介紹串行RapidIO。

串行RapidIO基于現在已廣泛用于背板互連的SerDes(Serialize Deserialize)技術,它采用差分交流耦合信號。差分交流耦合信號具有抗干擾強、速率高、傳輸距離較遠等優點。差分交流耦合信號的質量不是由傳統的時序參數來衡量,而是通過眼圖來衡量,眼圖中的“眼睛”張得越開則信號質量越好。

下圖是一個典型的串行RapidIO信號的眼圖。

差分信號的強弱由一對信號線的電壓差值表示,串行RapidIO協議規定信號峰-峰值的范圍是200mV-2000mV。信號幅度越大,則傳輸距離越遠,RapidIO協議按信號傳輸距離定義兩種傳輸指標:

① 短距離傳輸(Short Run),<=50厘米,主要用于板內互連,推薦的發送端信號峰-峰值為500mV-1000mV

② 長距離傳輸(Long Run),>50厘米,主要用于板間或背板互連,推薦的發送端信號峰-峰值為800mV-1600mV

為了支持全雙工傳輸,串行RapidIO收發信號是獨立的,所以每一個串行RapidIO口由4根信號線組成。標準的1x/4x 串行RapidIO接口,支持四個口,共16根信號線。這四個口可被用作獨立的接口傳輸不同的數據;也可合并在一起當作一個接口使用,以提高單一接口的吞吐量。

德州儀器TMS320C6455 DSP上集成了標準的1x/4x串行RapidIO接口,如圖

發送時,邏輯層和傳輸層將組好的包經過CRC編碼后被送到物理層的FIFO中,“8b/10b編碼”模塊將每8bit數據編碼成10bits數據,“并/串轉換”模塊將10bits并行數據轉換成串行bits,發送模塊把數字bit轉換成差分交流耦合信號在信號線上發送出去。

這里的8b/10編碼的主要作用是:

① 保證信號有足夠的跳變,以便于接收方恢復時鐘。串行RapidIO沒有專門的時鐘信號線,接收端靠數據信號的跳變恢復時鐘。所以需要把信號跳變少的8bits數據(如全0或全1)編碼成有一定跳變的10bits數據。另外,也使得總體數據中0和1的個數均衡,以消除直流分量,保證交流耦合特性;

② 8b/10編碼可擴大符號空間,以承載帶內控制符號。10bits能表示1024個符號,其中256個表示有效的8bits數據,剩下的符號中的幾十個被用作控制符號。控制符號可被用作包分隔符,響應標志,或用于鏈路初始化,鏈路控制等功能;

③ 8b/10編碼能實現一定的檢錯功能。1024個符號中,除了256個有效數據符號和幾十個控制符號外,其它符號都是非法的,接收方收到非法符號則表示鏈路傳輸出錯。

接收的過程則正好相反,首先接收方需要根據數據信號的跳變恢復出時鐘,用這個時鐘采樣串行信號,將串行信號轉換為10bits的并行信號,再按8b/10b編碼規則解碼得到8bits數據,最后做CRC校驗并送上層處理。

數據被正確的接收時,接收端會發送一個ACK響應包給發送端;如果數據不正確(CRC錯或非法的10bits符號),則會送NACK包,要求發送方重傳。這種重傳糾錯的功能由物理層完成,而物理層功能往往由硬件實現,所以不需要軟件干預。

串行RapidIO支持的信號速率有三種:1.25GHz,2.5GHz,3.125GHz。但由于8b/10b編碼,其有效數據速率分別為:1Gbps, 2Gbps, 2.5Gbps。 4個1x端口或一個4x端口支持的最高速率為10Gbps。

四、xlinx srio ip介紹

Endpoint IP由物理層、傳輸層及邏輯層組成,自帶可配置buffer design、reference clock module、reset module及configuration fabric referencedesign。支持1x、2x、4x lane widths,支持per-lane speeds of 1.25、2.5、3.125、5.0及6.25Gbaud。SRIO Gen2使用AXI4-Stream接口用于高速數據傳輸。

邏輯層定義了操作協議和包格式。

傳輸層提供端點器件間傳輸包所需的路由信息。

物理層定義器件級接口的細節,如包傳輸機制、流量控制、電氣特性和低級錯誤管理。

1. 1SRIO系統預覽

2. 邏輯層接口介紹

由圖一可以看到邏輯層有三種接口:ConfigurationFabric Interface,具體如下:

User Interface

主要包含一系列I/O ports和三類可選的ports,主要是用來發包和收包解析。對于使用哪些接口,在FPGA開發過程中,可以在IP core進行配置,實現時,每種事物根據事物的類型接入對應的port中。

其中,任何支持I/O事物傳輸的都將在I/O ports收發,如NWRITEs、NWRITE_Rs、SWRITEs、NREADs和RESPONSEs等事物;MESSAGE事物則可以在I/O ports傳輸,也可以在專用的messaging port傳輸;DOORBELL事物不管有沒有message port,都將使用IO port進行傳輸;如果定義了maintenance接口,那么maintenance事物將通過maintenance接口進行傳輸;如果使用了User-defined接口的話,那么用戶自定義的、系統不支持的或者未指明接口的事物將可以采用這種User-defined接口,如果未使能User-defined接口,那么上面提到這3種事物包將被丟棄。

必備的I/O Port

IO port支持2種格式:HELLO format 和SRIOstream。對于模式和包格式的選擇都需要在創建IPcore的時候選定好,并且IO ports里面所有的channels都必須使用相同的包格式。

IO ports配置成condensedIO模式主要是為了減少channels數,此時只有一個AXI4-stream 用來收發數據。在這種模式下,SRIO的IO port很接近于PCIE的AXI總線。(注意端口命名的參考是LOG層).

initiator/Target允許在遠端的initiator發起事物并把本地的endpoint作為事物傳送目標。從下面其接口圖可以看出,其實感覺有點類似IIC,規定什么時候誰為master,向slave發起操作,故具備了2套獨立的AXI4-stream用來收發數據。

s_axis_ireq* are associated with INITIATOR_IREQ.

m_axis_iresp* are associated with INITIATOR_IRESP.

m_axis_treq* are associated with TARGET_TREQ.

s_axis_tresp* are associated with TARGET_TRESP.

可選的Messaging Port

為什么是可選的呢,因為message也可以作為普通的wrtie事物通過I/O prot進行傳輸,IP core 產生時可以對這個進行選擇。默認是和I/O port復用的,但是如果作為獨立的port也是可以的,接口類型和initiator/Target一樣。

可選的Maintenance Port

雖然說這個是可選的,可是在xilinx的IP core配置上,這個好像是一定存在的,并且還被推薦配置成AXI4-Liteinterface,當然也可以配置成AXI4-Stream。這2種interface的區別主要在于AXI4-Lite interface不僅可以讓用戶app target本地的配置空間,還可以target遠端的配置空間,而AXI4-Stream interface只能配置遠端的配置空間。

可選的User-Defined Port

User-definedport采用的是SRIO stream format,并且擁有2個AXI4-Stream channels。

3. BUF接口垃圾桶

BUF層夾雜在LOG層和PHY層中間,為包的傳送和流控制提供了保證。當然收發的buffer大小是可配的,值得注意的是,這里說的大小不是說fifo size或深度之類的,而是max sized packets的個數,即按最大size包的個數進行管理的。

上面的和LOG和PHY層的interface是AXI4-Stream,而cfgb則是AXI4-Liteinterface接口,實現進入BUF層的配置空間。

該層主要包含以下一些接口:

(1)clock andresetinterface

(2)transport interface

(3)link interface

(4)BUF configurationfabric interface

4. 物理層接口

RapidIO串行物理層,通常稱為串行RapidIO,針對板上或通過背板的器件間的電氣連接。串行物理層定義器件間的全雙工串行鏈路,在每個方向上使用單向差分信號。RapidIO串行物理層支持RapidIO器件間的包傳送,包括包和控制符號的傳送、流量控制、錯誤管理和其他器件到器件的功能。

由于串行RapidIO規范僅在物理層定義(RapidIO技術定于物理層為電氣接口和器件到器件的鏈路協議),多數RapidIO控制器的邏輯是相同的。因此,串行RapidIO規范保留了許多已有的設計經驗和經過證實的基礎結構,簡化了并行與串行鏈路間的系統級交換操作。

RapidIO串行物理層有如下特征:

(1)采用8B/10B編碼方案將發送時鐘嵌入到數據中;

(2)在每個方向上支持一個串行差分對,稱為1通道;或支持四個并列的串行差分對,稱為4通道;

(3)使用專用的8B/10B碼來管理鏈路,管理內容包括流量控制、包定界和錯誤報告;

(4)允許在RapidIO1x/4xLP-Serial(串行RapidIO)端口和RapidIO物理層8/16 LP-LVDS(并行RapidIO)端口之間進行包傳輸而無需包處理;

(5)使用與并行RapidIO物理層相似的重傳和錯誤恢復協議;

(6)支持每通道1.25G、2.5G和3.125G波特率(數據流為1.0Gbps、2.0Gbps和2.5Gbps)的傳送速率。(現在支持的應該更多了,可以高達6.25G了)

該層主要包含以下一些接口:

(1)clock and reset interface

(2)link interface

(3)serial interface

(4)control and statusinterface

(5)configuration fabricinterface

(6)serial transceiversinterface

(7)configuration fabricreference design interface

五、xlinx srio ip

在利用Xilinx的IP進行開發時,為了簡化報文的解析和組包,SRIO Gen2 usesAXI4-Stream,Xilinx推出了一種簡化的報文格式,這樣一來,我們可以發現,這樣又很接近PCIE的TLP報文格式了。

lHELLO format

引腳示意:

編輯:hfy

-

嵌入式系統

+關注

關注

41文章

3672瀏覽量

131135 -

RapidIO

+關注

關注

1文章

40瀏覽量

21112 -

PCI

+關注

關注

5文章

679瀏覽量

131689 -

存儲器接口

+關注

關注

0文章

16瀏覽量

8039 -

嵌入式設備

+關注

關注

0文章

116瀏覽量

17385

發布評論請先 登錄

嵌入式系統 RapidIO協議結構詳解

嵌入式系統 RapidIO協議結構詳解

評論