最近本人一直在學(xué)習(xí)ZYNQ SOC的使用,目的是應(yīng)對(duì)科研需要,做出通用的算法驗(yàn)證平臺(tái)。大概思想是:ZYNQ PS端負(fù)責(zé)與MATLAB等上位機(jī)數(shù)據(jù)分析與可視化軟件交互:既可傳輸數(shù)據(jù),也能通過(guò)上位機(jī)配置更新硬件算法模塊配置寄存器內(nèi)容,同時(shí)可計(jì)算分析PL端算法實(shí)現(xiàn)性能指標(biāo)。PL端的FPGA邏輯則負(fù)責(zé)算法的硬件實(shí)現(xiàn),以探索高效并行硬件架構(gòu)。為此本人后續(xù)會(huì)持續(xù)編寫《利用ZYNQ SOC快速打開(kāi)算法驗(yàn)證通路》系列專題博文,在各個(gè)階段進(jìn)行些基礎(chǔ)性總結(jié)。

MATLAB中數(shù)據(jù)為雙精度浮點(diǎn)型,因此打開(kāi)算法驗(yàn)證通路的第一步即為MATLAB中浮點(diǎn)數(shù)與定點(diǎn)二進(jìn)制補(bǔ)碼之間的相互轉(zhuǎn)換。在之前的博文:《FPGA與MATLAB數(shù)據(jù)交互高效率驗(yàn)證算法——仿真階段》中提到過(guò)兩種數(shù)值表示方式之間的轉(zhuǎn)換,但為了便于testbench仿真,MATLAB寫和讀的文件均為txt文本文件。在算法板級(jí)驗(yàn)證中,數(shù)據(jù)應(yīng)以未經(jīng)過(guò)ASCII碼編碼的二進(jìn)制數(shù)據(jù)方式被處理。這里涉及到MATLAB函數(shù)fscanf和fprintf以及函數(shù)fread和fwrite的區(qū)別,前兩個(gè)分別為讀和寫文本文件,后兩個(gè)則是讀寫二進(jìn)制文件。

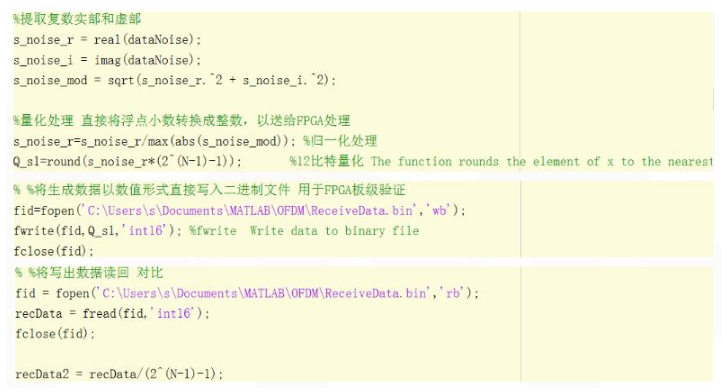

以下給出浮點(diǎn)定點(diǎn)轉(zhuǎn)換以及讀寫二進(jìn)制文件代碼:

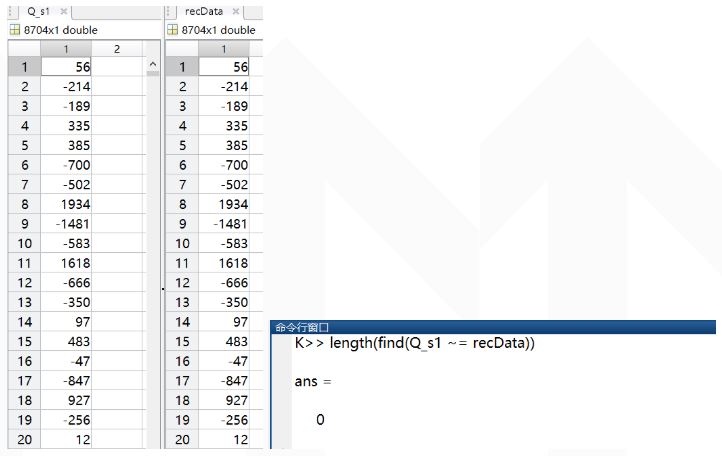

先看下寫出到文件的數(shù)據(jù)和從該該文件讀回的數(shù)據(jù)是否一致。

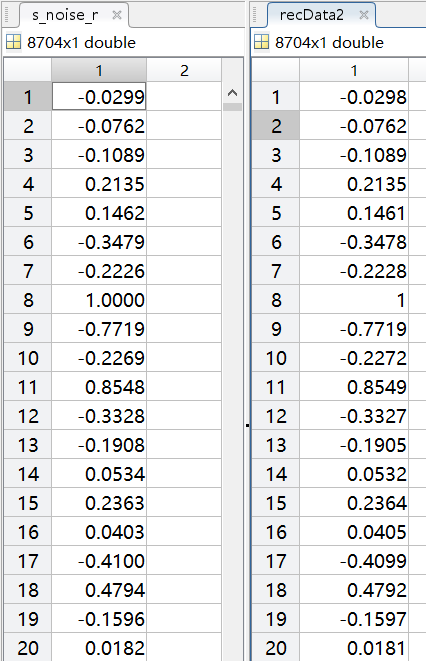

直接對(duì)比數(shù)據(jù)和命令檢測(cè)結(jié)果顯示兩者完全一致。再來(lái)對(duì)比下量化之前與讀回定點(diǎn)數(shù)經(jīng)過(guò)類型轉(zhuǎn)換后的浮點(diǎn)數(shù)。

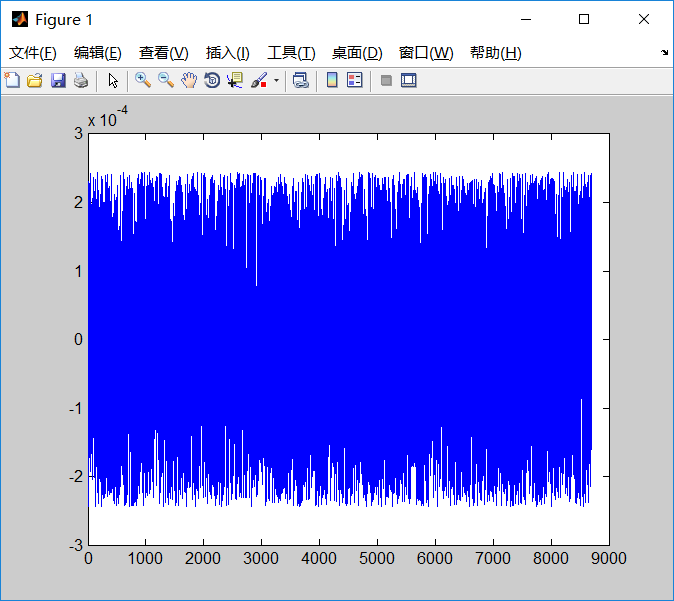

MATLAB顯示兩者的差值。可見(jiàn)在浮點(diǎn)轉(zhuǎn)定點(diǎn)數(shù)時(shí),會(huì)有一定的精度損失,但僅在10的負(fù)四次方數(shù)量級(jí),在很多精度要求不高的場(chǎng)合下可以忽略。

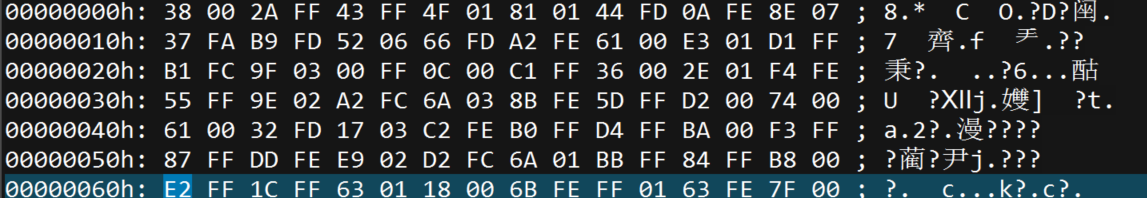

現(xiàn)在利用Uedit軟件打開(kāi)該文件,并以16進(jìn)制方式顯示:

我們用前兩個(gè)數(shù)據(jù)做驗(yàn)證,依次是00_38和FF_2A。由于是補(bǔ)碼形式,故先寫成二進(jìn)制形式:0000_0000_0011_1000和1111_1111_0010_1010,再轉(zhuǎn)換為原碼:0000_0000_0011_1000和1000_0000_1101_0110,十進(jìn)制結(jié)果就是56和-240,與MATLAB中數(shù)據(jù)吻合。

非常簡(jiǎn)單的東西困擾了我有一陣,希望對(duì)大家有幫助吧。因?yàn)樗惴?yàn)證平臺(tái)僅是載體,最重要的是PL端的算法硬件實(shí)現(xiàn)部分。為了簡(jiǎn)單快速形成算法驗(yàn)證通路,采用網(wǎng)絡(luò)調(diào)試助手和W5500協(xié)議棧芯片實(shí)現(xiàn)MATLAB與ZYNQ之間的數(shù)據(jù)傳輸,從而避免寫上位機(jī)軟件和網(wǎng)絡(luò)協(xié)議先關(guān)設(shè)計(jì)配置帶來(lái)的工作量。這部分內(nèi)容在下篇博文中敘述。

編輯:hfy

-

matlab

+關(guān)注

關(guān)注

189文章

3000瀏覽量

233836 -

二進(jìn)制

+關(guān)注

關(guān)注

2文章

807瀏覽量

42286 -

浮點(diǎn)數(shù)

+關(guān)注

關(guān)注

0文章

61瀏覽量

16114

發(fā)布評(píng)論請(qǐng)先 登錄

偏移二進(jìn)制和二進(jìn)制補(bǔ)碼如何和實(shí)際數(shù)據(jù)對(duì)應(yīng),如何轉(zhuǎn)換?

西門子TIA Portal如何比較兩個(gè)浮點(diǎn)數(shù)相等

ADS1282采集到的數(shù)據(jù)傳到PC上應(yīng)該怎么轉(zhuǎn)為浮點(diǎn)數(shù)?

hex格式和二進(jìn)制的區(qū)別

為什么Gain=1對(duì)應(yīng)的默認(rèn)值不是16位二進(jìn)制補(bǔ)碼的中間數(shù)而是最小數(shù)?

二進(jìn)制編碼器在自動(dòng)化領(lǐng)域的作用

二進(jìn)制編碼器的種類及特點(diǎn)

二進(jìn)制編碼器應(yīng)用場(chǎng)景 二進(jìn)制編碼器與模擬編碼器比較

二進(jìn)制編碼器工作原理 如何選擇二進(jìn)制編碼器

labview中浮點(diǎn)數(shù)與十六進(jìn)制字符串相互轉(zhuǎn)化

二進(jìn)制補(bǔ)碼及與原碼的互相轉(zhuǎn)換方法

TMS320C6743定點(diǎn)和浮點(diǎn)數(shù)字信號(hào)處理器數(shù)據(jù)表

TMS320C6654定點(diǎn)和浮點(diǎn)數(shù)字信號(hào)處理器數(shù)據(jù)表

TMS320C6655/57定點(diǎn)和浮點(diǎn)數(shù)字信號(hào)處理器數(shù)據(jù)表

TMS320C6671定點(diǎn)和浮點(diǎn)數(shù)字信號(hào)處理器數(shù)據(jù)表

MATLAB浮點(diǎn)數(shù)與定點(diǎn)二進(jìn)制補(bǔ)碼互轉(zhuǎn)算法驗(yàn)證方案

MATLAB浮點(diǎn)數(shù)與定點(diǎn)二進(jìn)制補(bǔ)碼互轉(zhuǎn)算法驗(yàn)證方案

評(píng)論