本應用筆記介紹了 TW2880P-BC2-GR 芯片。該文檔介紹了 Clockgen 和 PLL,包括 SCK、MCLK 和 VCLK 寄存器。該芯片的 PCB 布局如圖所示,包括 SDRAM、DAC 和 HDMI 布局。本文檔還討論了 PB 窗口和通道 ID 解碼、記錄和 SPOT 單元、基于 TW2880C 的顯示設置、OSG 和簡單 OSD、運動檢測和中斷、DMA 功能、音頻接口以及 C2 和B1.

第 1 部分:時鐘發(fā)生器和 PLL

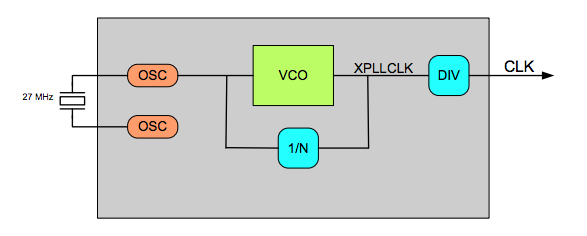

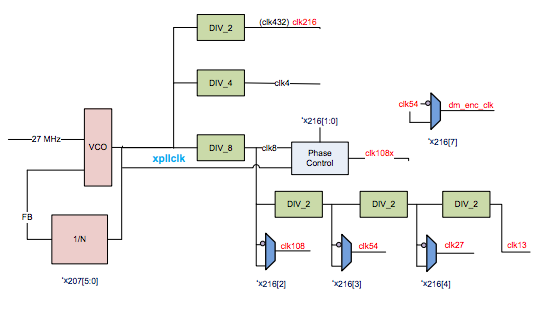

TW2880C 具有三個時鐘域,分別是系統(tǒng)時鐘域、存儲器時鐘域和視頻時鐘域。每個時鐘域支持不同種類的功能單元。時鐘由三個不同的自由運行 PLL 生成。VCO 級之后的高速時鐘在到達最終電路之前將經(jīng)過串聯(lián)分頻器和相位選擇。現(xiàn)在我們將詳細介紹每個時鐘域。

時鐘

整個 TW2880 都使用系統(tǒng)時鐘。這個想法是我們還將在這個時鐘組中使用 27 的倍數(shù)的時鐘。原因顯而易見;27 MHz 時鐘是 BT.656 標準的數(shù)據(jù)時鐘。由于這些特性,一些視頻解碼器或 CVBS 輸出部分將使用該時鐘組。

時鐘列表

- 該時鐘組產(chǎn)生 12 個時鐘。

- 108 MHz 系統(tǒng)時鐘

- 54、27、13.5 MHz 系統(tǒng)在輸入/輸出模塊中使用

- 帶相位控制的 108 MHz 系統(tǒng)時鐘,用于錄音輸出單元。

- 高速 216 MHz 定標時鐘(可以是 432 MHz)

- 雙顯示器電視編碼器時鐘

- 雙顯示器視頻時鐘

- 定標器的雙顯示器快速時鐘

- 雙監(jiān)視器 DAC 時鐘

- VGA 的雙顯示器外部視頻時鐘

- 網(wǎng)口輸出時鐘

SPLL 的寄存器設置

在正常情況下,[0x207] 位[5:0] 被設計為具有默認值 5'd31,因為這將使 xpllclk 為 864 MHz,經(jīng) 8 個電路分頻后將創(chuàng)建 108 MHz 系統(tǒng)時鐘。

[0x216] bit 2, 3, 4 用于選擇108 MHz、54 MHz和27 MHz時鐘的相位。

[0x216] bit 1, 0 用于選擇108 MHz時鐘的相位,用于調整記錄端口時鐘/數(shù)據(jù)的關系。

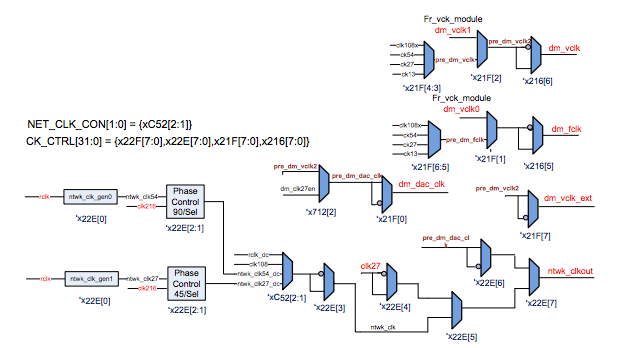

[0x21F] bit 2:1 用于選擇雙監(jiān)視器時鐘的來源,如果需要 CVBS,我們應該使用 SCLK 組產(chǎn)生的時鐘。如果與 27 MHz 以外的顯示模式相關,那么我們應該將這兩位設置為 1,并使用 VCLK 組生成的時鐘。

編輯:hfy

-

寄存器

+關注

關注

31文章

5432瀏覽量

123998 -

時鐘發(fā)生器

+關注

關注

1文章

223瀏覽量

69028

發(fā)布評論請先 登錄

熱TW2880P-BC2-GR 芯片應用筆記

熱TW2880P-BC2-GR 芯片應用筆記

評論