我們在介紹信號完整性的時候通常會說“當(dāng)傳輸延時大于六分之一的信號的上升時間時,需要考慮信號完整性問題”,于是乎教科書里面都會配上一副類似于這樣表現(xiàn)上升時間或者傳輸延時與反射的圖片:

最開始的時候小陳說這段話時總會覺得很別扭,“我堂堂信號完整性怎么能是區(qū)區(qū)反射就能說明的呢?”之后隨著理論與實踐的深入,越來越覺得“反射中有黃金屋,反射中有顏如玉”,be the signal,弄清楚反射與串?dāng)_就拿到了解開信號完整性謎題的兩把最關(guān)鍵的鑰匙,小陳也很希望能陪各位書友將反射弄得更清楚一些,趁著圍毆反射的機會,我們將反射系列修改補充后再復(fù)習(xí)一遍。

在先導(dǎo)集里,我們先來理一理信號這一路發(fā)展過來的心路歷程。

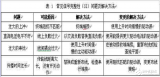

在最初的時候,我們還是幾百K幾兆的信號,幾十納秒的上升時間。十幾歐姆的驅(qū)動阻抗?沒問題!小半米的走線?沒問題!多負(fù)載亂七八糟的拓?fù)洌繘]問題!

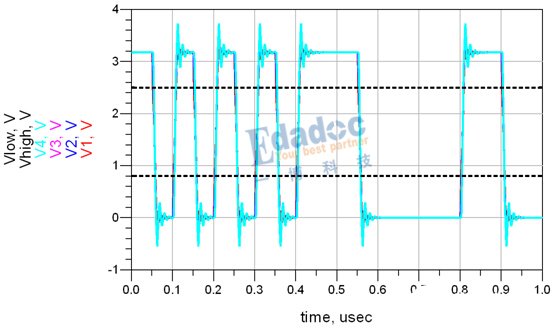

(10ns上升時間,4個負(fù)載,最長負(fù)載距離0.8m)

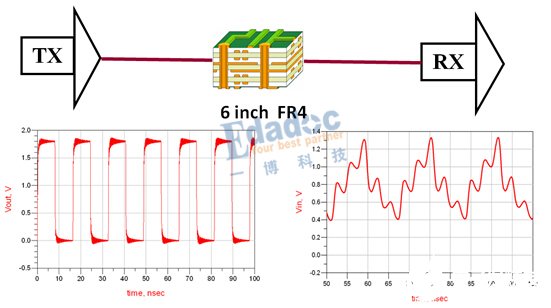

慢慢的芯片工藝越來越發(fā)達(dá),一些時鐘芯片,明明只有幾十兆,但是上升時間卻做到了納秒以下,這時候一旦走線過長,原本好好的信號就會由于反射,即使是點對點的傳輸,一旦傳輸線過長,還是會使得接收端無法接收到正確的信號了。

這時候人們要考慮的是縮短走線的距離,或者在鏈路中間加一個redriver。

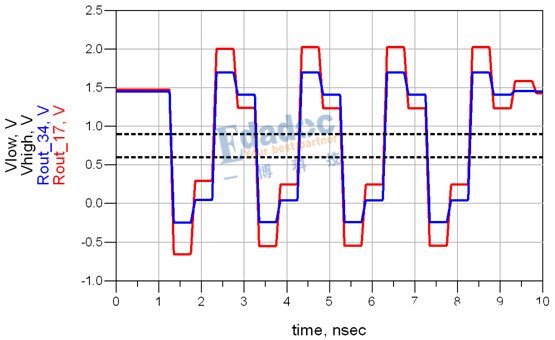

后來,出現(xiàn)了像DDRx這樣的幾百兆甚至上G的信號,驅(qū)動端的阻抗已經(jīng)不是你想低就能低了,從十七歐姆到三十四歐姆,再不行的話還需要加匹配電阻或者拉低傳輸線阻抗來減小源端反射,甚至加上了ODT等等。拓?fù)湟膊皇窍朐趺醋呔驮趺醋吡耍琓點到遠(yuǎn)端樹形,菊花鏈到fly-by,還要在末端疏通一下管道,加上上拉電阻。

(點對點信號,上升時間100ps,驅(qū)動端阻抗為17與34歐姆的比較)

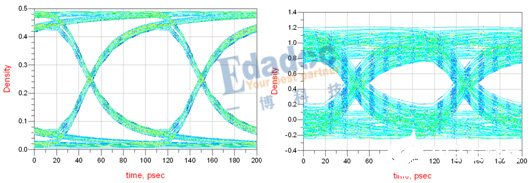

再后來,串行信號出現(xiàn)了,其目標(biāo)是為了實現(xiàn)超高速傳輸。功耗大咱們可以降低電平;損耗大咱們可以用預(yù)加重均衡;串?dāng)_大咱們可以拉開間距;源端和末端這樣的反射大的話???那我們還是把發(fā)送端與接收端的阻抗都做成跟傳輸線一樣吧:

(發(fā)送/接收端阻抗匹配與不匹配的對比)

現(xiàn)在的電子產(chǎn)品,從芯片的設(shè)計到系統(tǒng)的完成,都需要考慮反射的影響,好好的了解一下反射的原理對我們理解硬件設(shè)計有非常大的幫助。

Ps:特別提醒,在學(xué)習(xí)的過程中需要帶入時間與長度的概念。

Ps:重發(fā)好沒誠意,這里解釋一下為何反射會淹沒在上升時間內(nèi)。

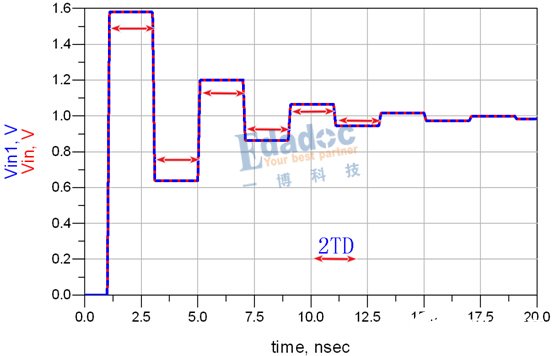

我們學(xué)習(xí)的時候公式是二維的,并沒有增加時間的概念,于是源端低阻抗,末端高阻抗時,當(dāng)發(fā)送端發(fā)送一個1V的階躍信號時,我們通常看到的接收端波形是一幅這樣的反彈圖:

在這幅圖中有兩個關(guān)鍵的時間,一個是上升時間TR,一個是傳輸延時TD。什么是TR?是信號從0到1的時間,這是一定會需要時間的。上圖中,信號的上升時間是100ps,傳輸延時是1ns。也就是說,第一個信號到達(dá)接收端的時候是1ns時,但是,信號達(dá)到最高幅值1.6V的時間是1.1ns。第二個反射波到達(dá)接收端的時候是3ns時。

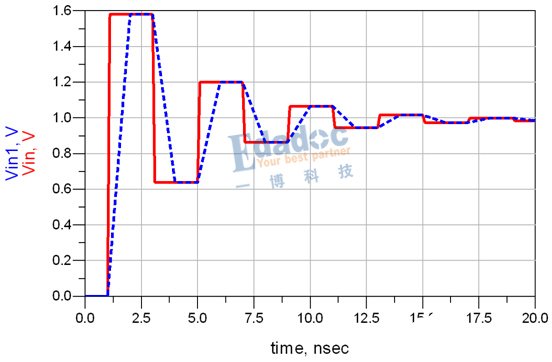

當(dāng)我們的上升時間變成了1ns時,我們經(jīng)過反射之后的幅值能不能達(dá)到最高值1.6V?顯然是可以的。我們的反彈圖變成了這樣,信號第一次到達(dá)最高幅值1.6V的時間是2ns。

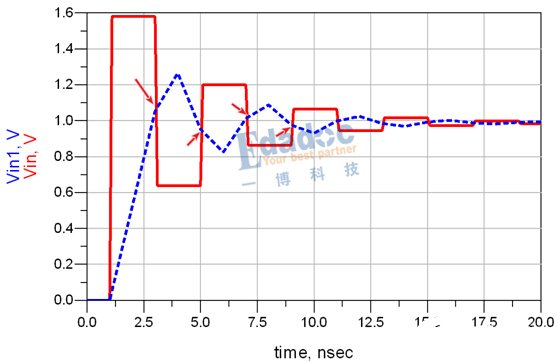

當(dāng)我們信號的上升時間為2ns的時候呢?也是可以的。但是如果當(dāng)信號的上升時間大于2ns時,接收端的信號還能達(dá)到1.6V嗎?永遠(yuǎn)不行了,因為在3ns處,第二次的反射波已經(jīng)過來了。于是,當(dāng)信號的上升時間為3ns時,反彈圖變成了這樣子:

注意箭頭位置,信號上升的斜率發(fā)生了明顯的變化,這是因為多次反射波的疊加。

當(dāng)信號的上升時間再長一點呢?他可能就不止會疊加第二次的反射波,還會疊加第三次第四次第五次第六次,多次的反射疊加之后,就幾乎看不出來反射的現(xiàn)象了。

在后文中,會將信號分解,從另外一個角度去分析解釋該現(xiàn)象。

編輯:hfy

-

信號完整性

+關(guān)注

關(guān)注

68文章

1440瀏覽量

96631 -

串?dāng)_

+關(guān)注

關(guān)注

4文章

189瀏覽量

27393 -

串行信號

+關(guān)注

關(guān)注

0文章

29瀏覽量

8630

發(fā)布評論請先 登錄

信號完整性(五):信號反射

信號完整性與電源完整性仿真分析

信號完整性簡介及protel信號完整性設(shè)計指南

信號完整性與電源完整性的仿真

信號完整性之反射(一)

信號完整性的“反射”的心路歷程

信號完整性的“反射”的心路歷程

評論