這幾天多篇文章爆出了“中芯國際涉軍”,已被美國列入黑名單,深知信息搬運(yùn)工的責(zé)任重大,秉著“不忘初心,牢記使命”的宗旨,外加周末有點(diǎn)自我安排的時(shí)間,所以也就有了本篇文章,另外作為模擬IC設(shè)計(jì)師,還是很有必要知道國內(nèi)有哪些集成電路代工廠+工藝節(jié)點(diǎn)+工藝特征,畢竟我也是填過坑的人,項(xiàng)目指標(biāo)來了首先需要確定的就是工藝,選擇不當(dāng)來回折騰也是難以避免,不廢話上內(nèi)容了。

責(zé)任編輯:xj

原文標(biāo)題:國內(nèi)主流集成電路代工廠的工藝特征

文章出處:【微信公眾號(hào):旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

集成電路

+關(guān)注

關(guān)注

5422文章

12025瀏覽量

368121 -

IC

+關(guān)注

關(guān)注

36文章

6111瀏覽量

179124 -

中芯國際

+關(guān)注

關(guān)注

27文章

1436瀏覽量

66240

原文標(biāo)題:國內(nèi)主流集成電路代工廠的工藝特征

文章出處:【微信號(hào):wc_ysj,微信公眾號(hào):旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

主流氧化工藝方法詳解

CMOS超大規(guī)模集成電路制造工藝流程的基礎(chǔ)知識(shí)

概倫電子集成電路工藝與設(shè)計(jì)驗(yàn)證評(píng)估平臺(tái)ME-Pro介紹

CMOS集成電路的基本制造工藝

等離子體蝕刻工藝對(duì)集成電路可靠性的影響

集成電路工藝中的金屬介紹

集成電路外延片詳解:構(gòu)成、工藝與應(yīng)用的全方位剖析

集成電路新突破:HKMG工藝引領(lǐng)性能革命

創(chuàng)飛芯90nm BCD工藝OTP IP模塊規(guī)模量產(chǎn)

集成電路工藝學(xué)習(xí)之路:從零基礎(chǔ)到專業(yè)水平的蛻變

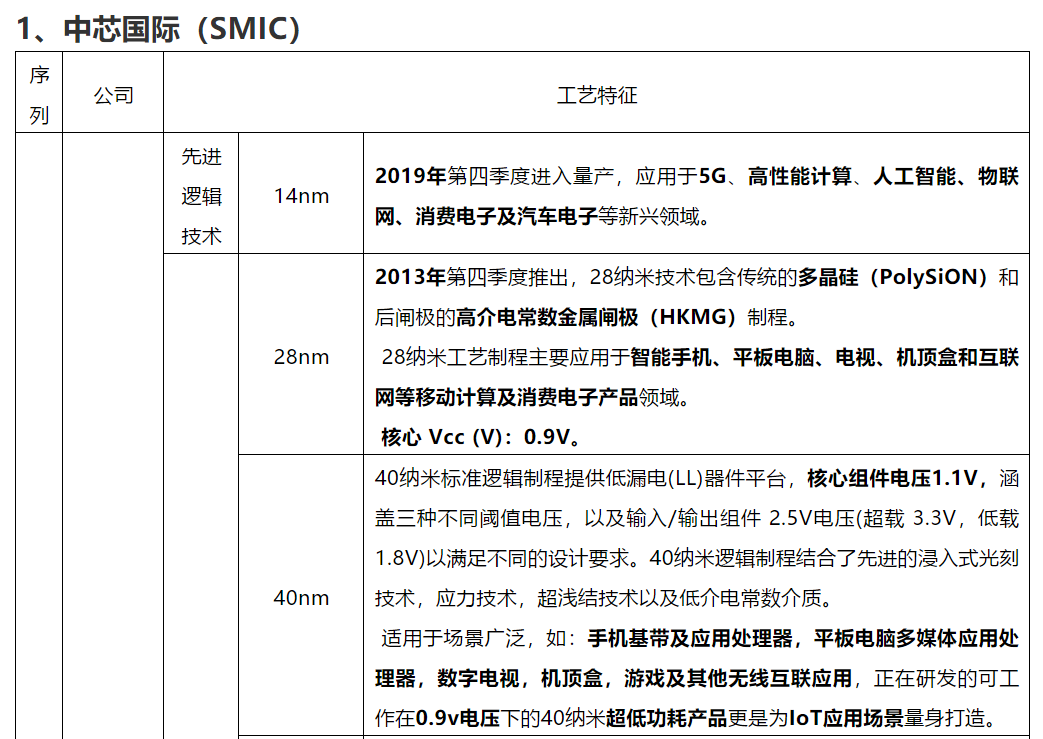

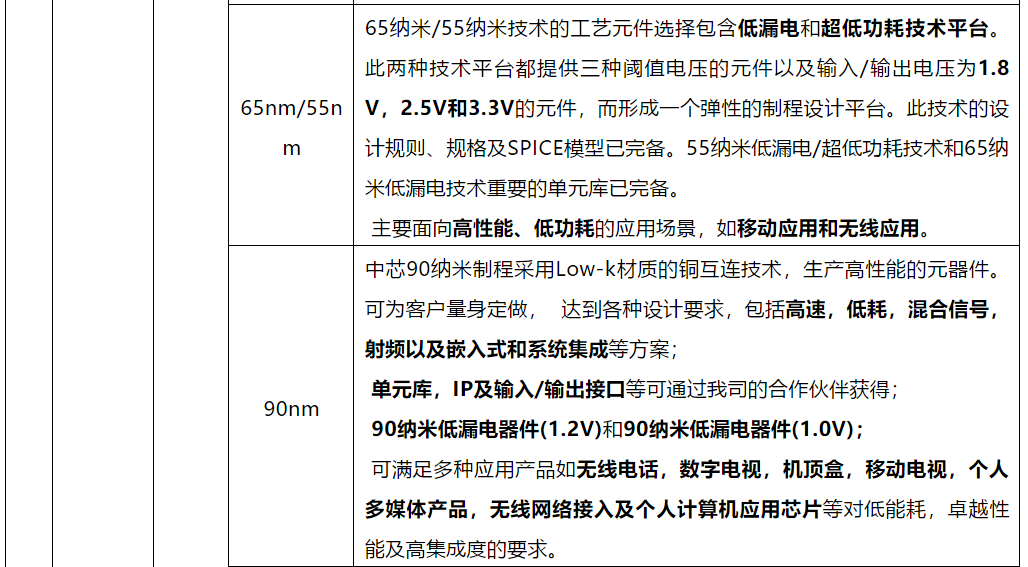

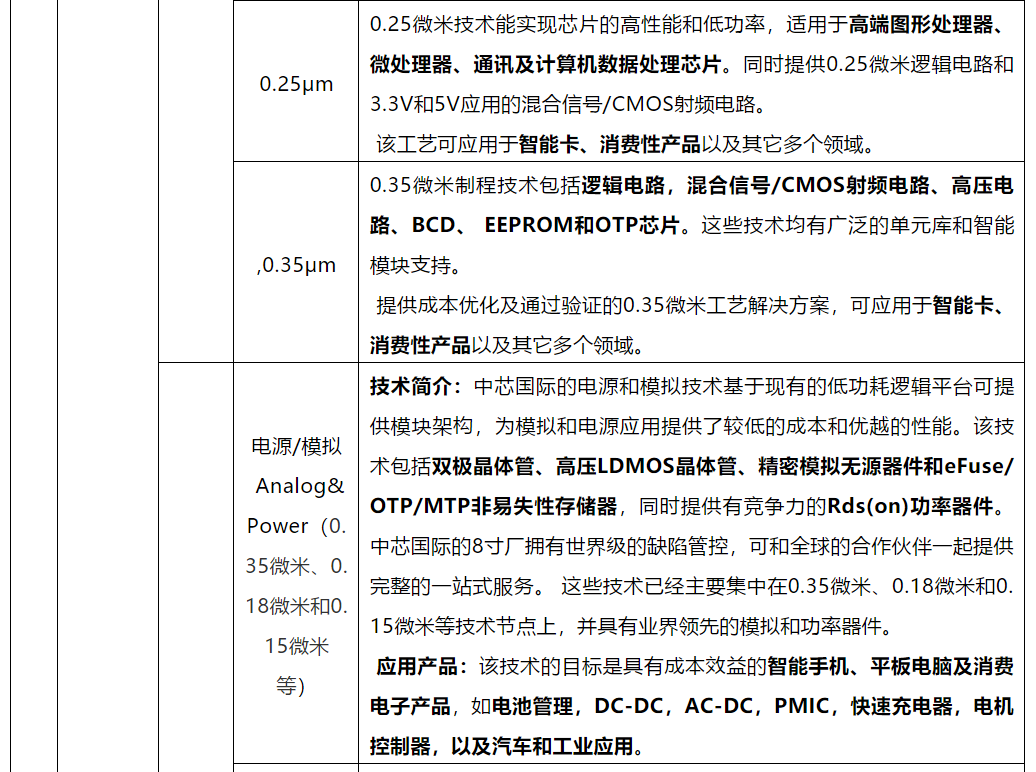

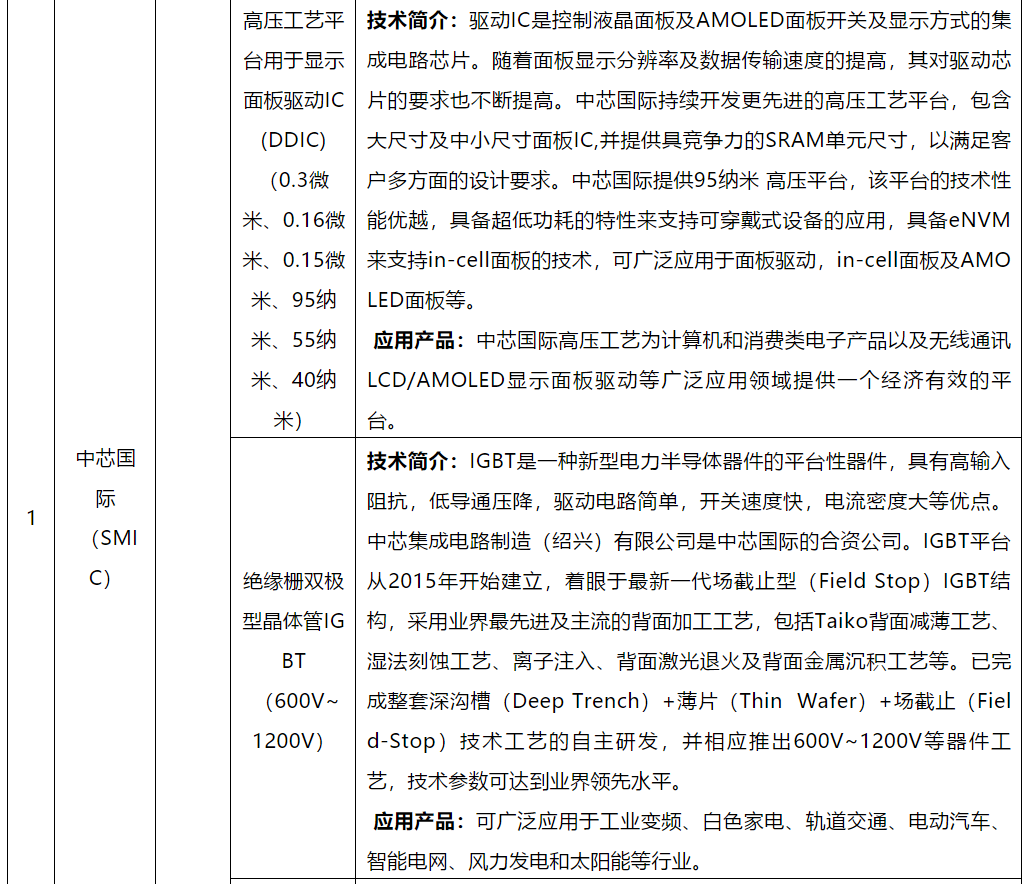

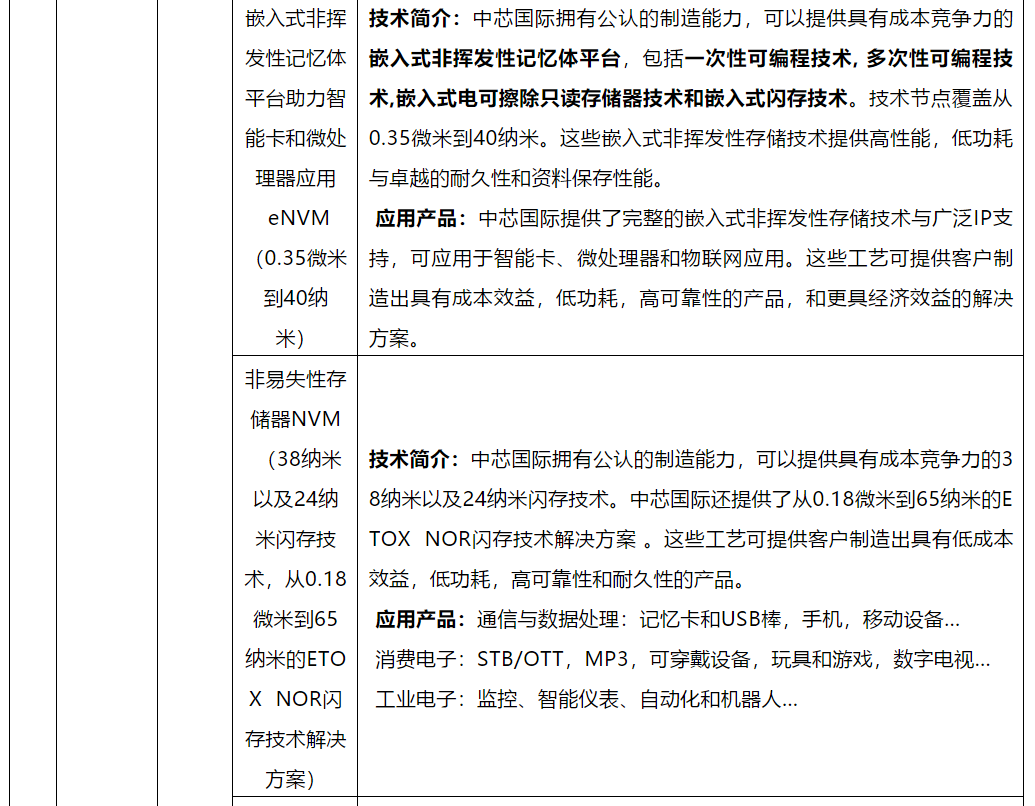

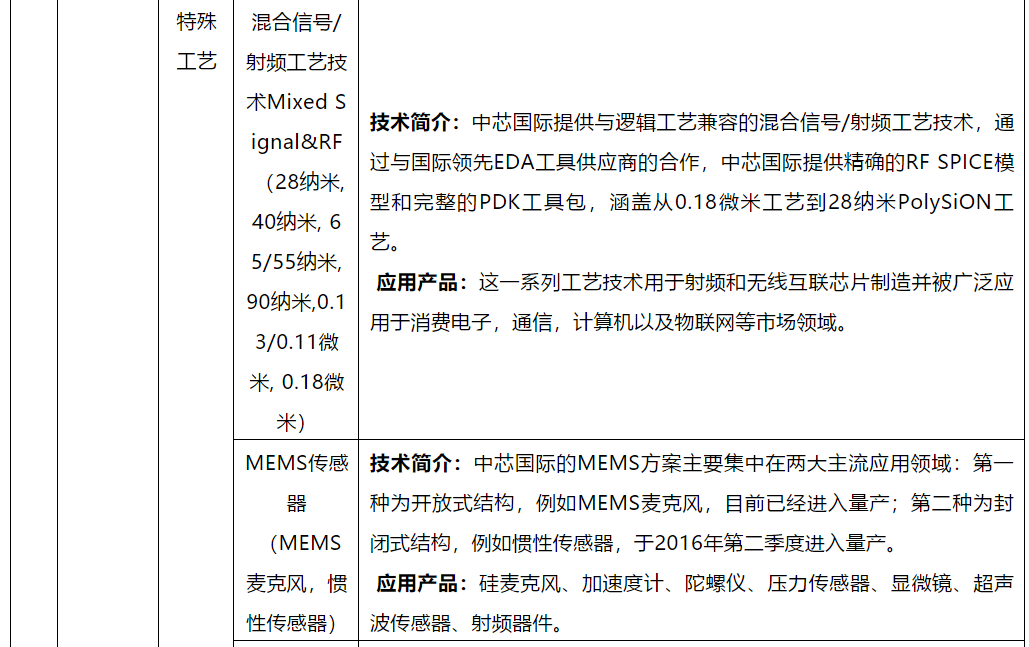

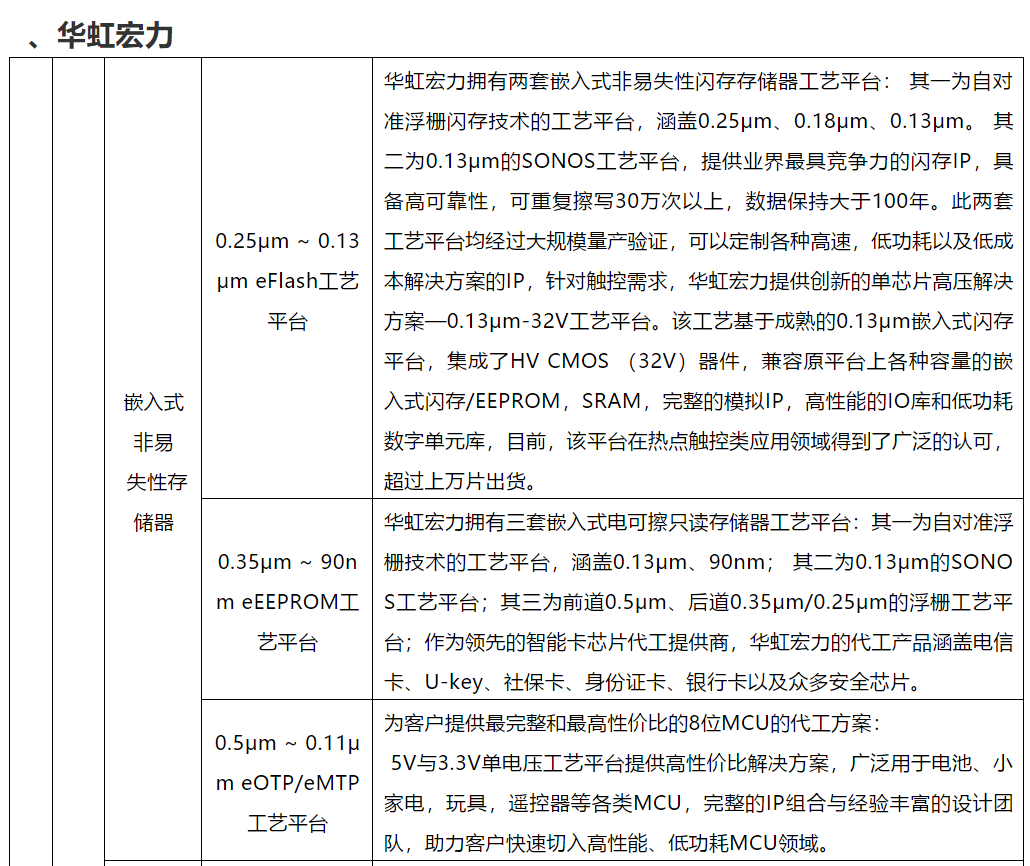

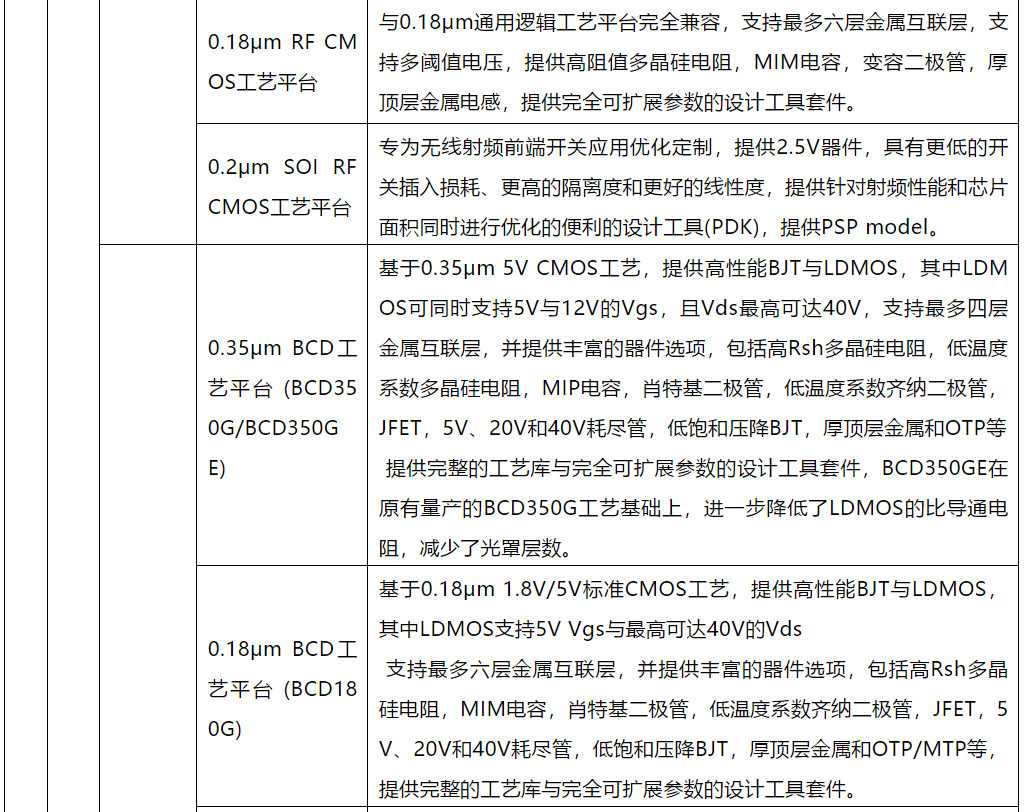

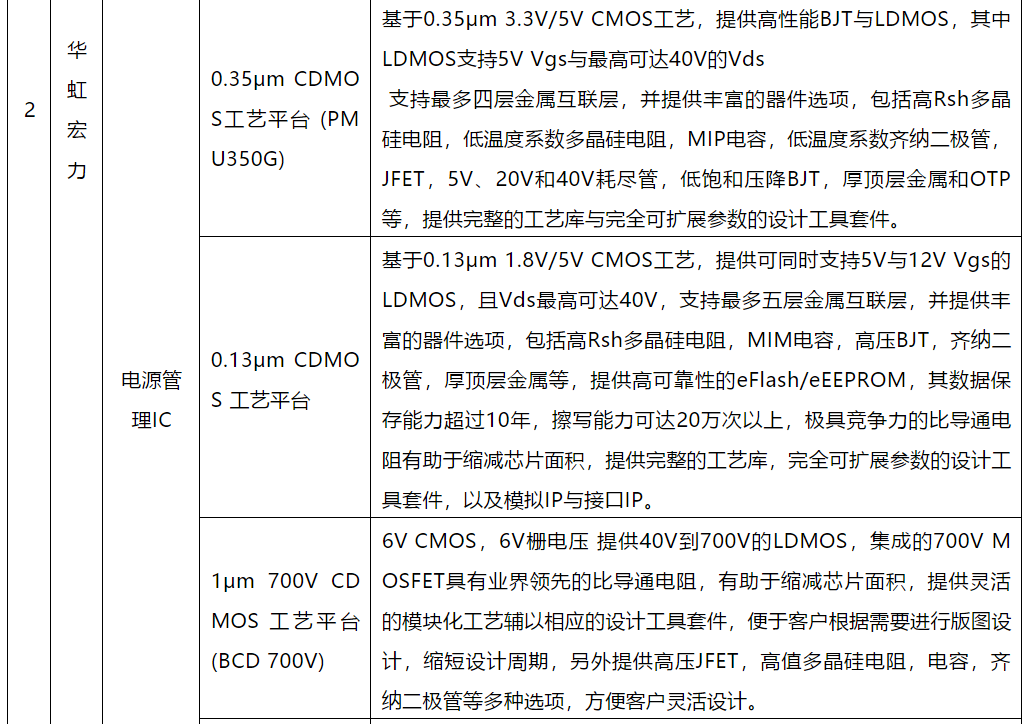

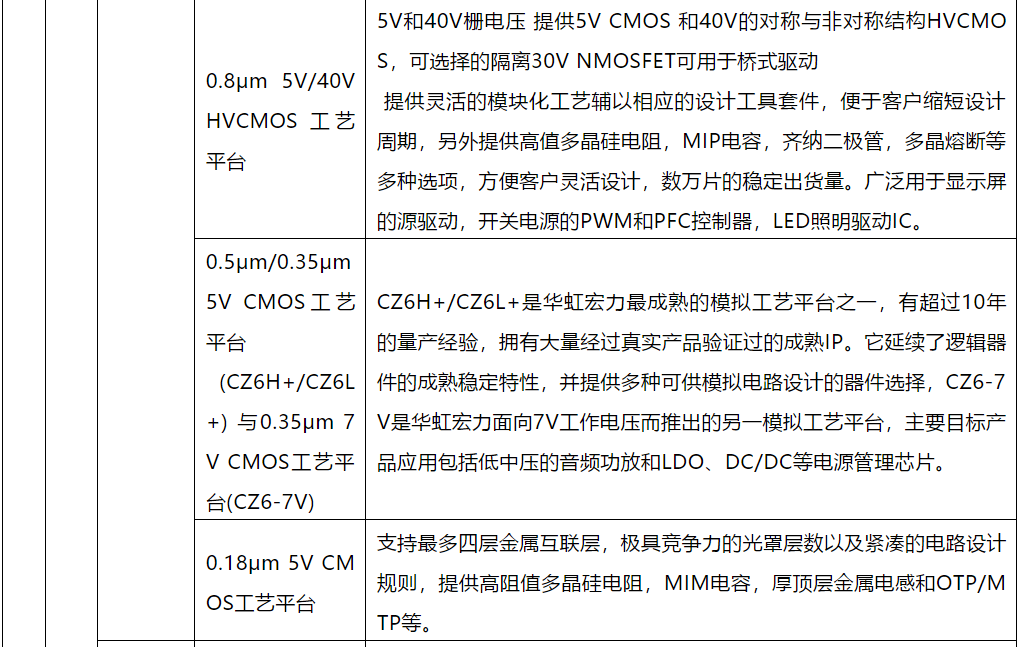

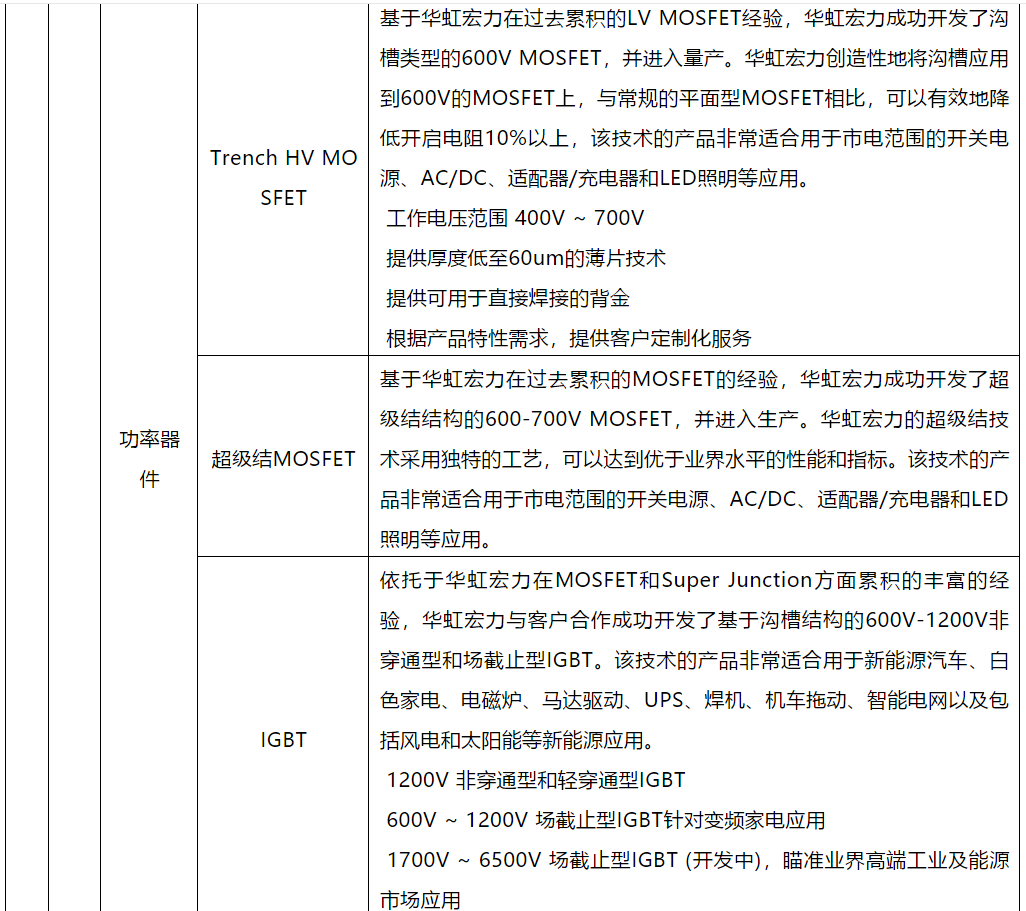

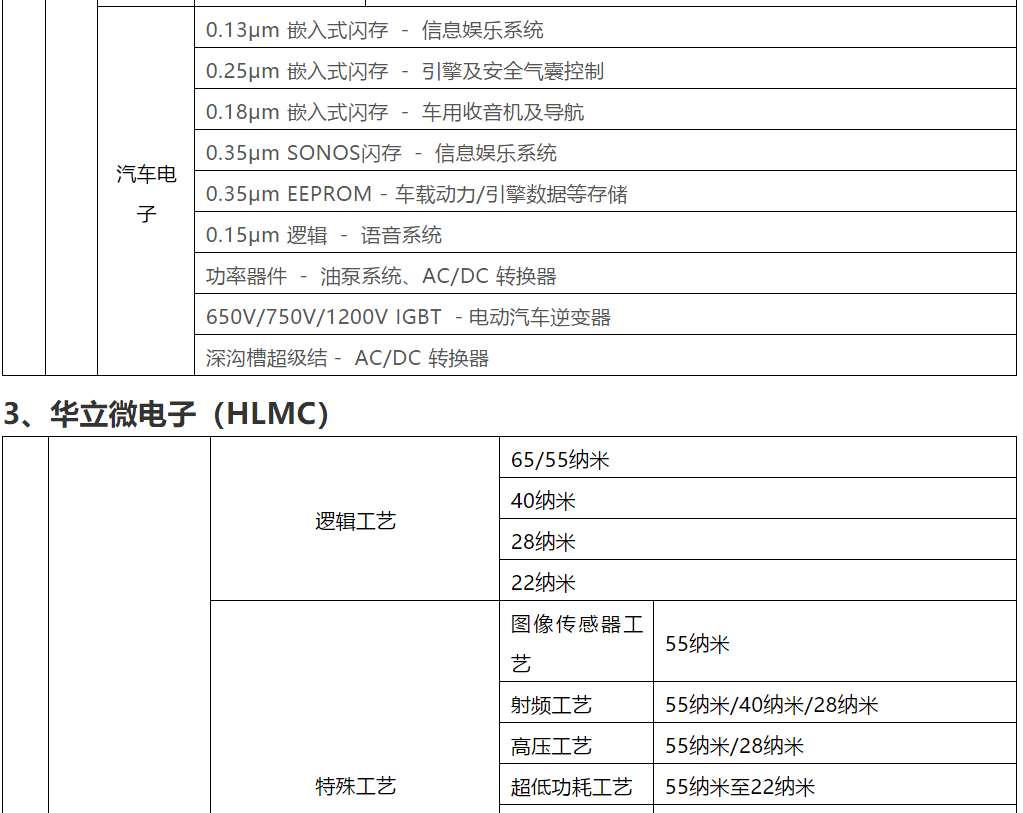

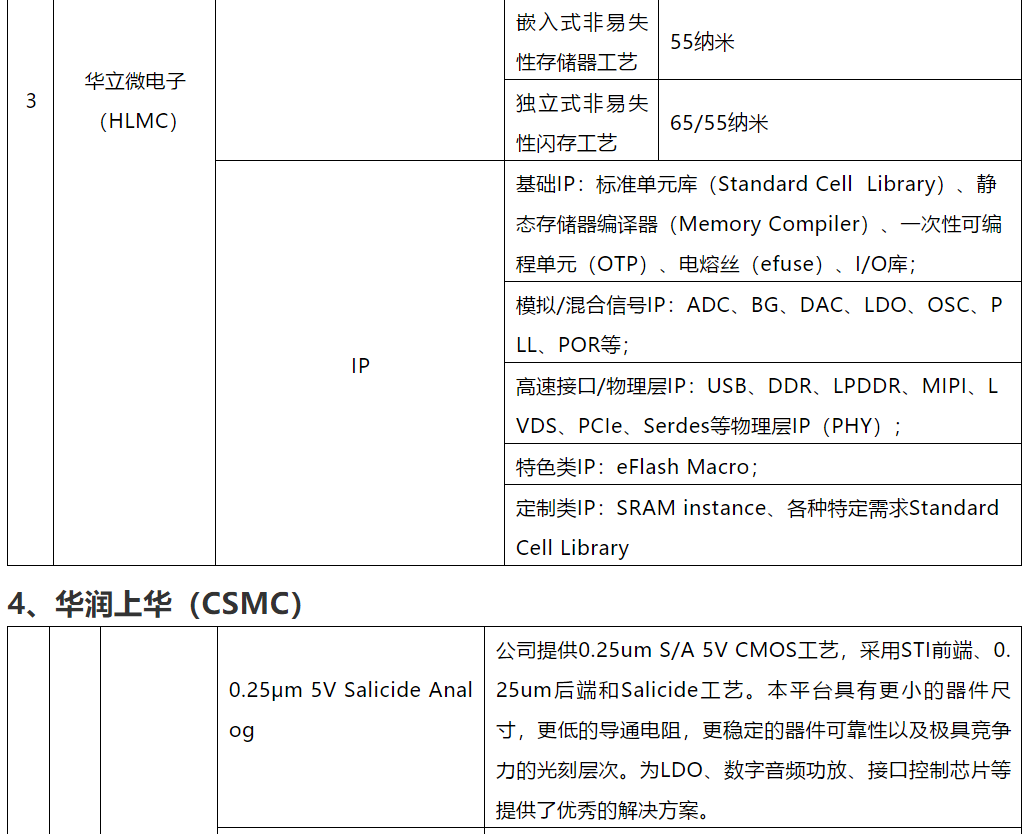

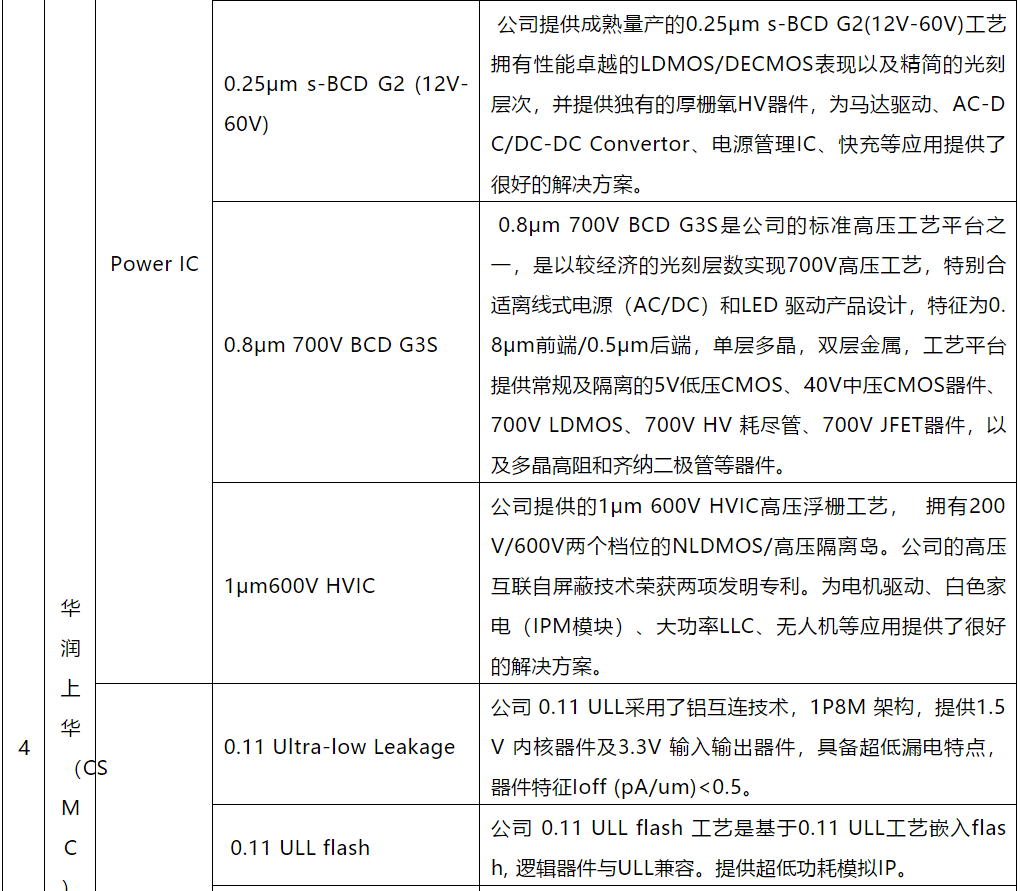

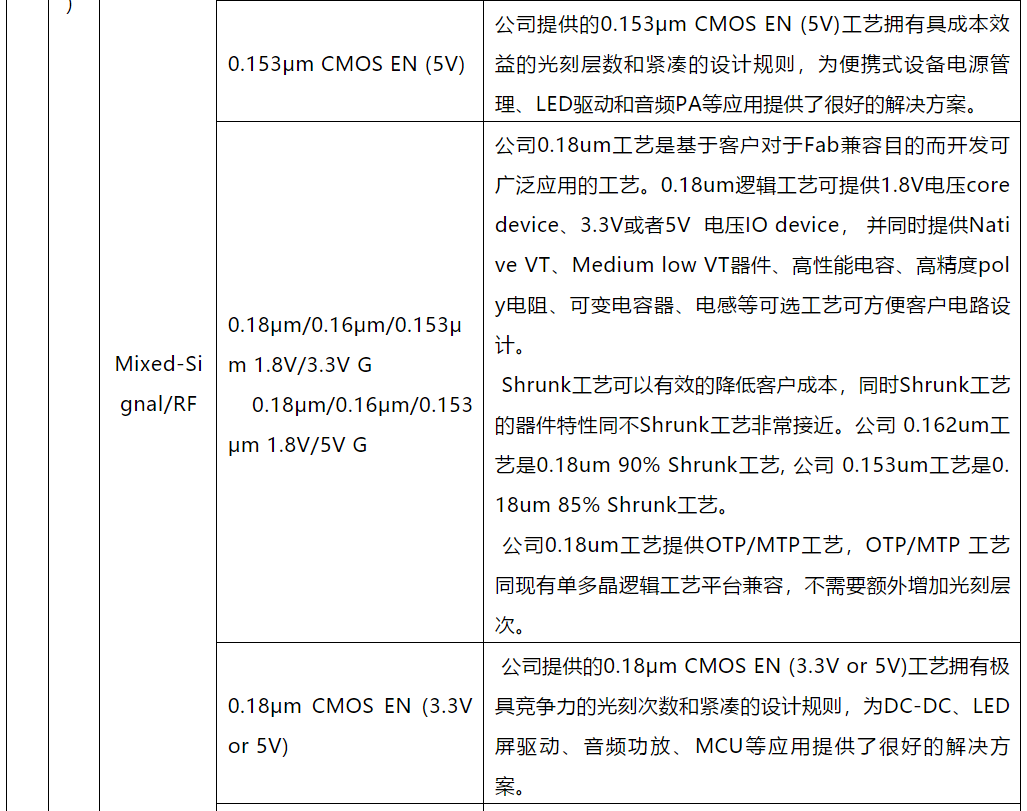

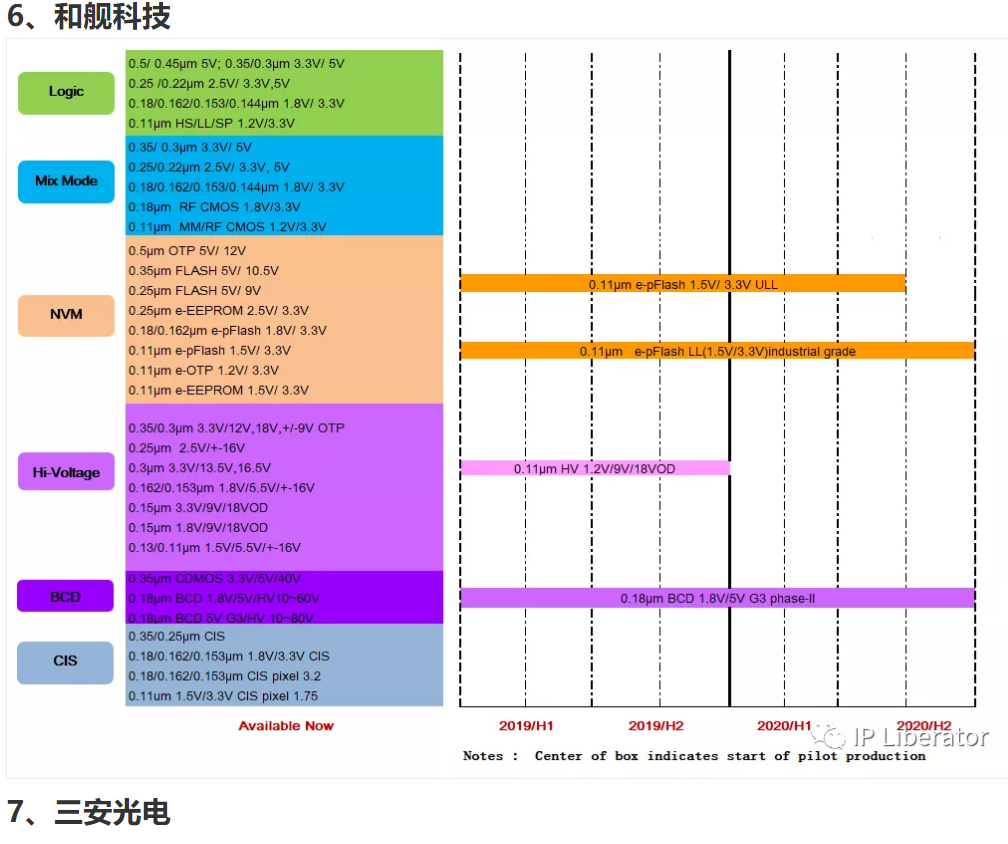

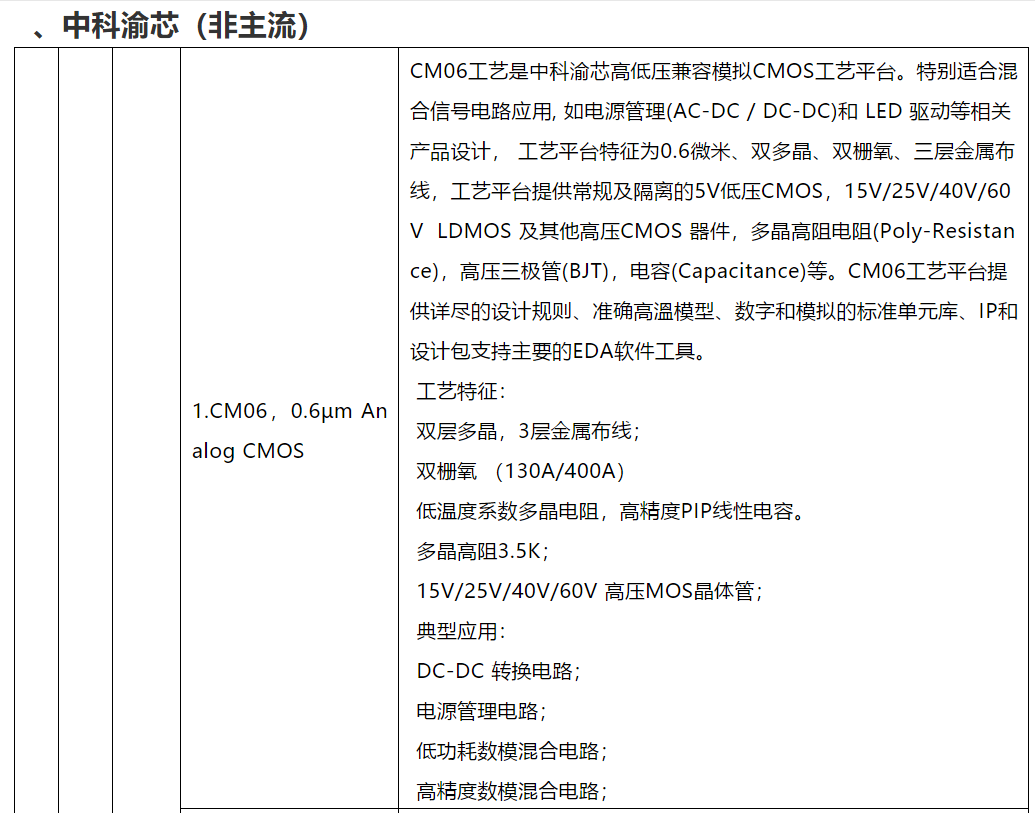

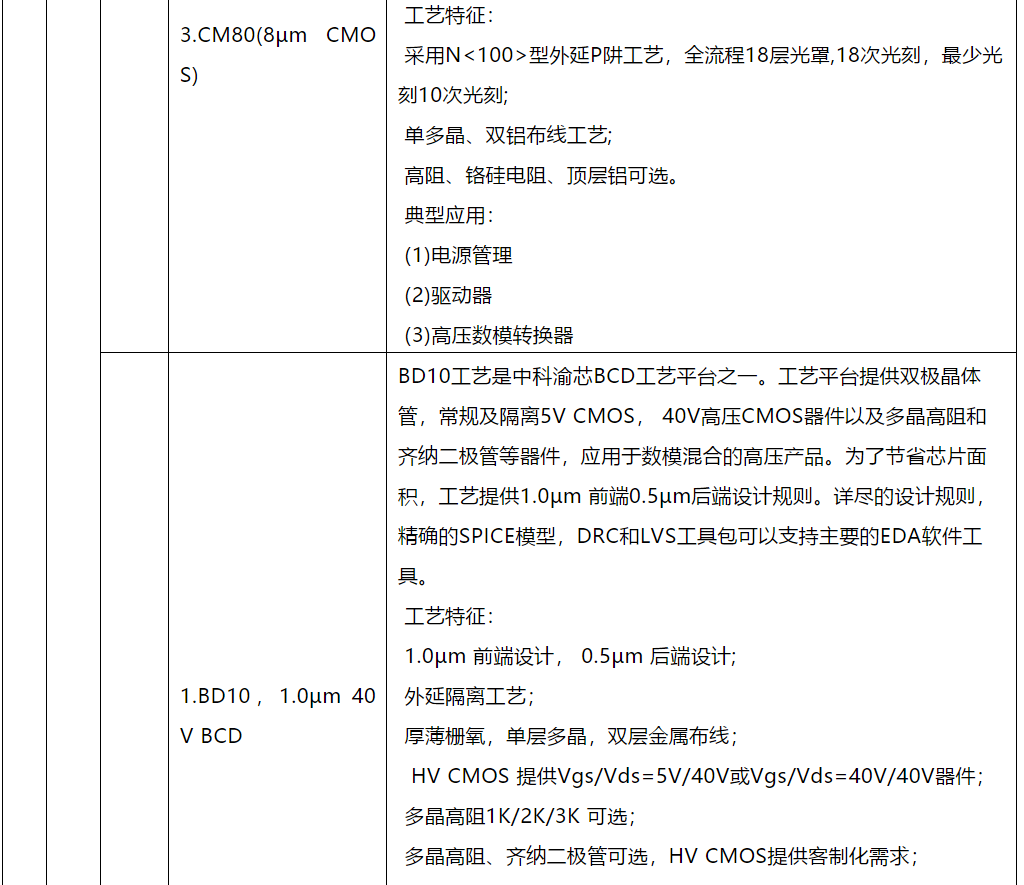

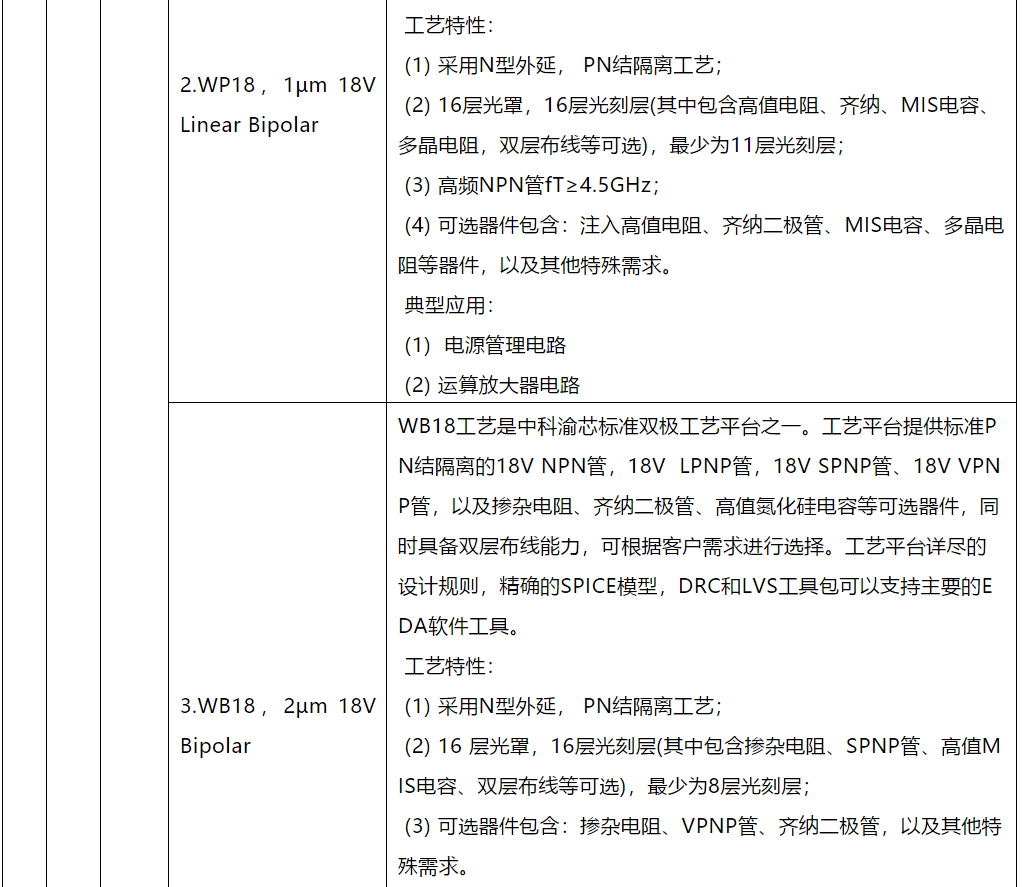

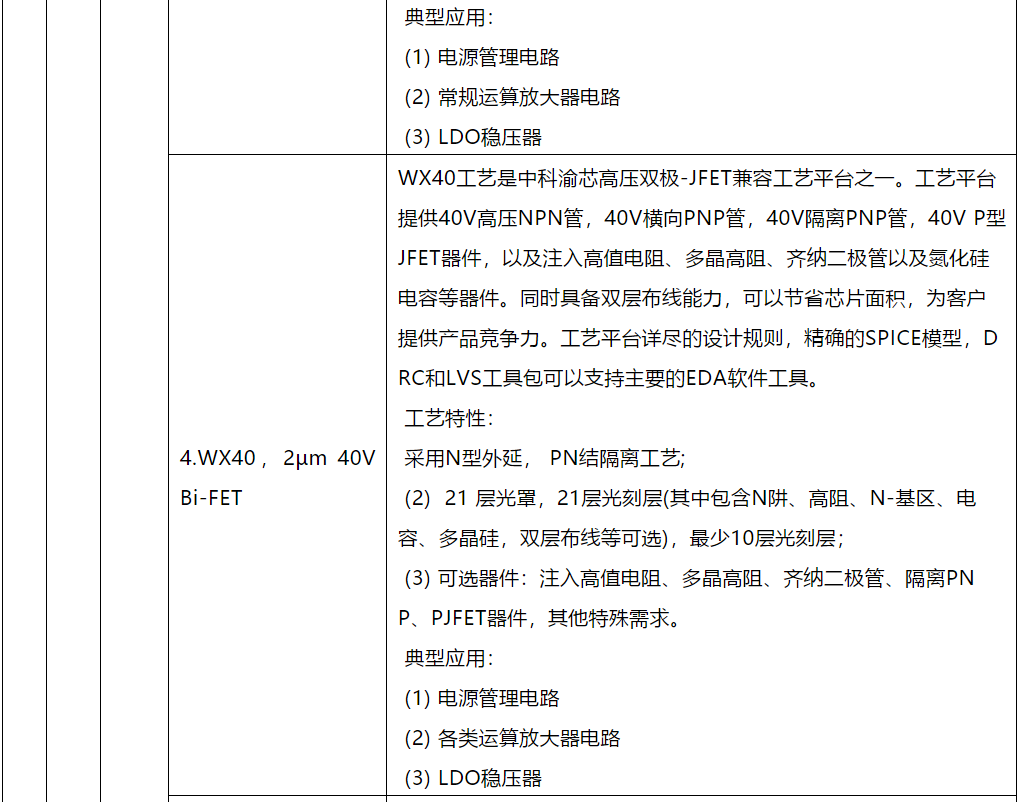

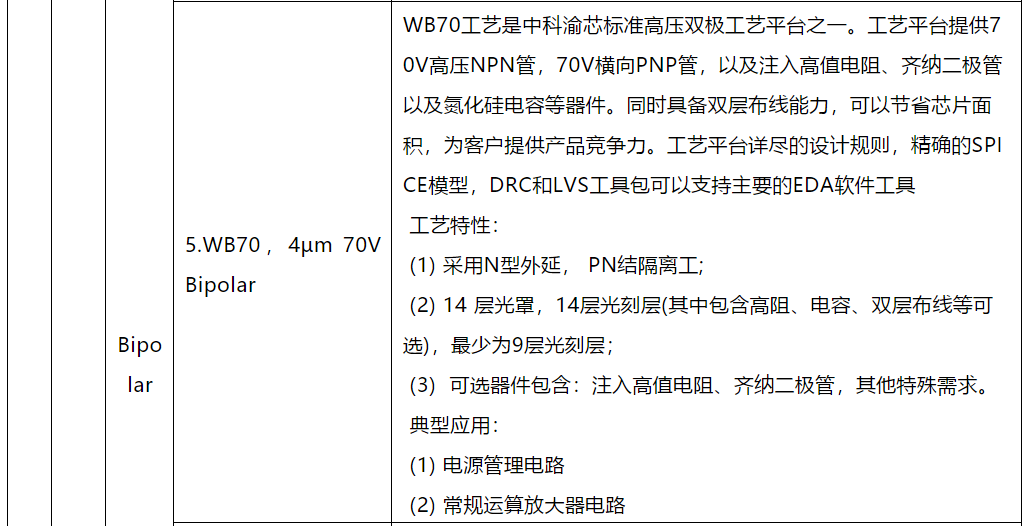

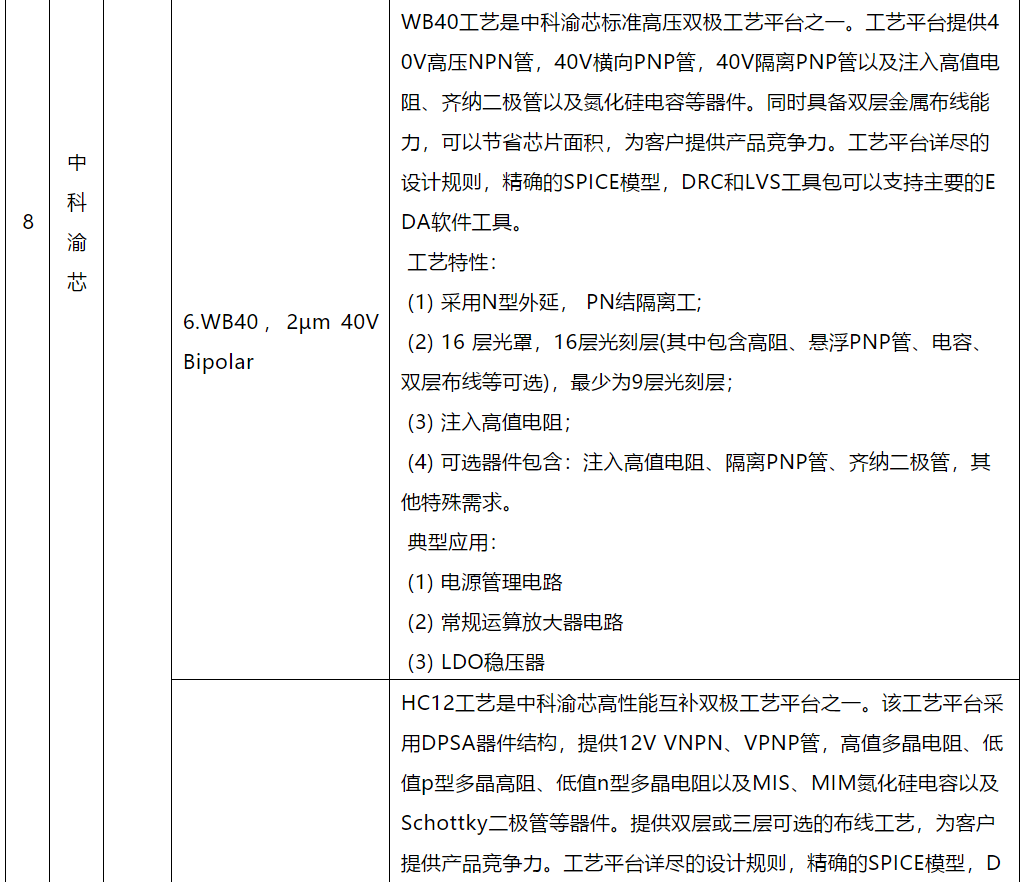

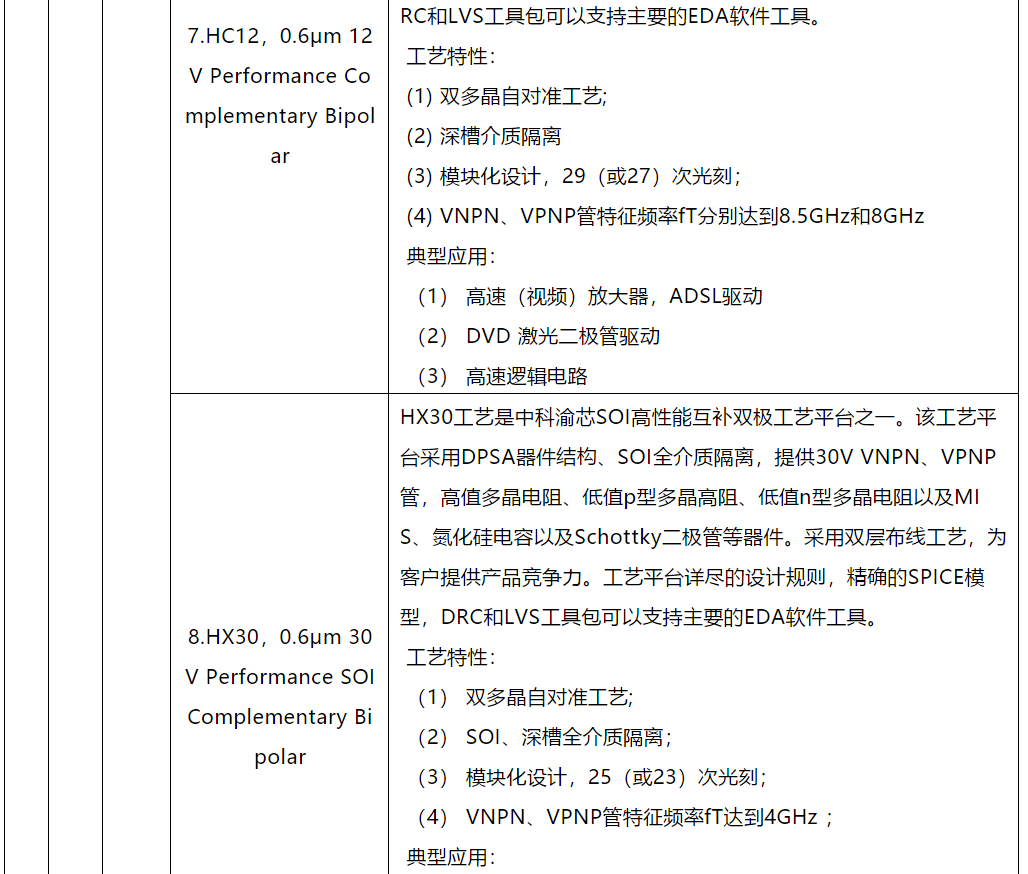

國內(nèi)主流集成電路代工廠、工藝節(jié)點(diǎn)及工藝特征

國內(nèi)主流集成電路代工廠、工藝節(jié)點(diǎn)及工藝特征

評(píng)論