IC Package (IC的封裝形式)指芯片(Die)和不同類型的框架(L/F)和塑封料(EMC)形成的不同外形的封裝體。

IC Package種類很多,可以按以下標(biāo)準(zhǔn)分類:

按封裝材料劃分為:

金屬封裝、陶瓷封裝、塑料封裝

金屬封裝主要用于軍工或航天技術(shù),無商業(yè)化產(chǎn)品;

陶瓷封裝優(yōu)于金屬封裝,也用于軍事產(chǎn)品,占少量商業(yè)化市場;

塑料封裝用于消費電子,因為其成本低,工藝簡單,可靠性高而占有絕大部分的市場份額;

按照和PCB板連接方式分為:

PTH封裝和SMT封裝

PTH-Pin Through Hole, 通孔式;

SMT-Surface Mount Technology,表面貼裝式。

目前市面上大部分IC均采為SMT式的

按照封裝外型可分為:

SOT、SOIC、TSSOP、QFN、QFP、BGA、CSP等;

決定封裝形式的兩個關(guān)鍵因素:

封裝效率。芯片面積/封裝面積,盡量接近1:1;

引腳數(shù)。引腳數(shù)越多,越高級,但是工藝難度也相應(yīng)增加;

其中,CSP由于采用了Flip Chip技術(shù)和裸片封裝,達(dá)到了 芯片面積/封裝面積=1:1,為目前最高級的技術(shù);

QFN—Quad Flat No-lead Package 四方無引腳扁平封裝

SOIC—Small Outline IC 小外形IC封裝

TSSOP—Thin Small Shrink Outline Package 薄小外形封裝

QFP—Quad Flat Package 四方引腳扁平式封裝

BGA—Ball Grid Array Package 球柵陣列式封裝

CSP—Chip Scale Package 芯片尺寸級封裝

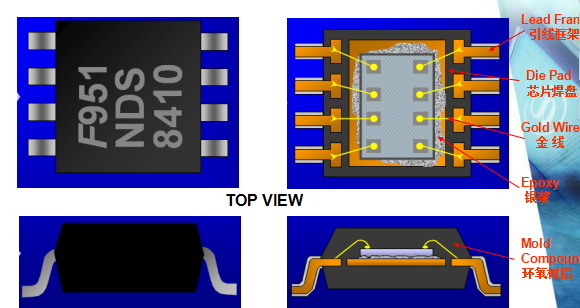

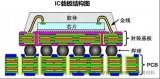

IC Package Structure(IC結(jié)構(gòu)圖)

Raw Material in Assembly(封裝原材料)【W(wǎng)afer】晶圓

【Lead Frame】引線框架

提供電路連接和Die的固定作用;

主要材料為銅,會在上面進(jìn)行鍍銀、 NiPdAu等材料;

L/F的制程有Etch和Stamp兩種;

易氧化,存放于氮氣柜中,濕度小 于40%RH;

除了BGA和CSP外,其他Package都會采用Lead Frame, BGA采用的是Substrate;

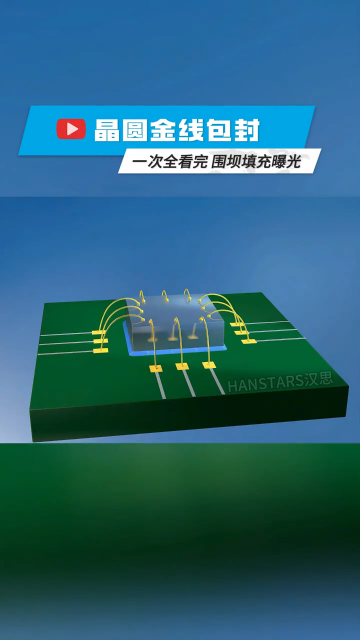

【Gold Wire】焊接金線

實現(xiàn)芯片和外部引線框架的電性和物 理連接;

金線采用的是99.99%的高純度金;

同時,出于成本考慮,目前有采用銅 線和鋁線工藝的。優(yōu)點是成本降低, 同時工藝難度加大,良率降低;

線徑?jīng)Q定可傳導(dǎo)的電流;0.8mil, 1.0mil,1.3mils,1.5mils和2.0mils;

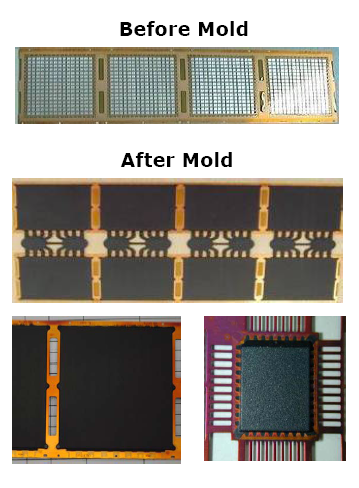

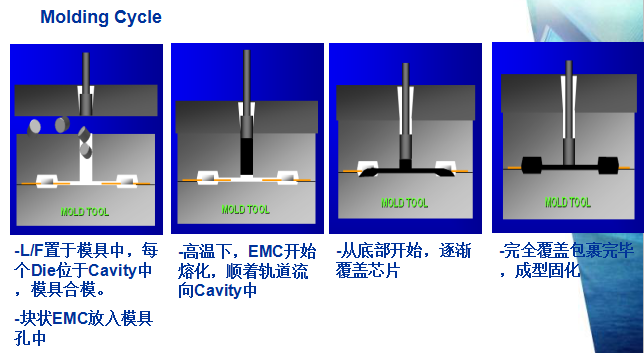

Mold Compound塑封料/環(huán)氧樹脂主要成分為:環(huán)氧樹脂及各種添加劑(固化劑,改性劑,脫 模劑,染色劑,阻燃劑等);

主要功能為:在熔融狀態(tài)下將Die和Lead Frame包裹起來, 提供物理和電氣保護(hù),防止外界干擾;

存放條件:零下5°保存,常溫下需回溫24小時;

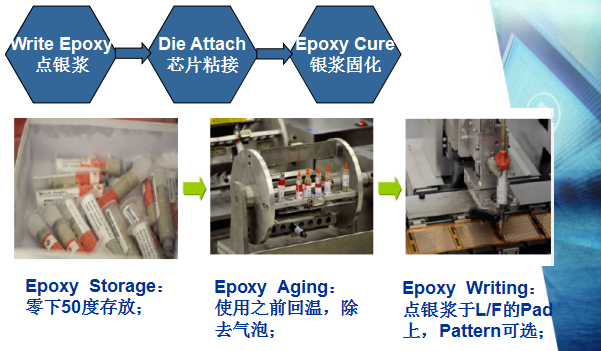

【Epoxy】銀漿

成分為環(huán)氧樹脂填充金屬粉末(Ag);有三個作用:將Die固定在Die Pad上; 散熱作用,導(dǎo)電作用;

-50°以下存放,使用之前回溫24小時;

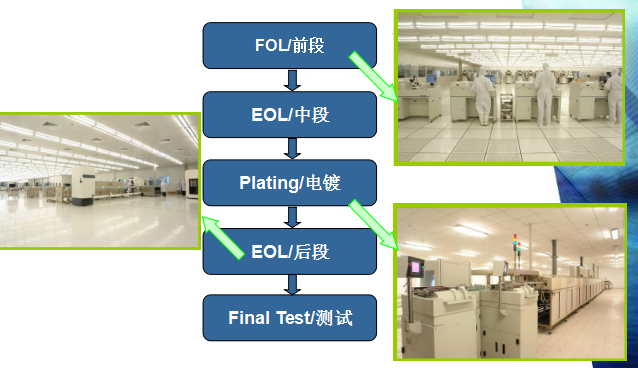

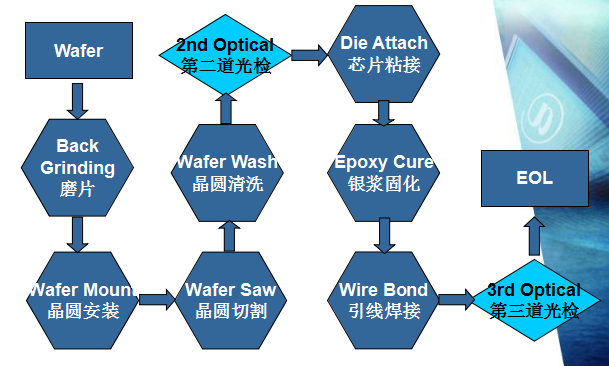

FOL– Front of Line前段工藝

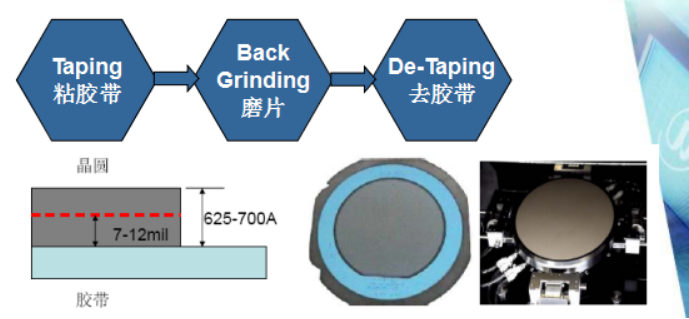

FOL– Back Grinding背面減薄

將從晶圓廠出來的Wafer進(jìn)行背面研磨,來減薄晶圓達(dá)到 封裝需要的厚度(8mils~10mils);

磨片時,需要在正面(Active Area)貼膠帶保護(hù)電路區(qū)域 同時研磨背面。研磨之后,去除膠帶,測量厚度;

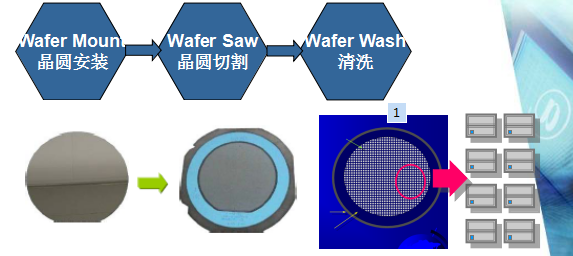

FOL– Wafer Saw晶圓切割

將晶圓粘貼在藍(lán)膜(Mylar)上,使得即使被切割開后,不會散落;

通過Saw Blade將整片Wafer切割成一個個獨立的Dice,方便后面的 Die Attach等工序;

Wafer Wash主要清洗Saw時候產(chǎn)生的各種粉塵,清潔Wafer;

FOL– 2nd Optical Inspection二光檢查

主要是針對Wafer Saw之后在顯微鏡下進(jìn)行Wafer的外觀檢查,是否有出現(xiàn)廢品。

FOL– Die Attach 芯片粘接

芯片拾取過程:

1、Ejector Pin從wafer下方的Mylar頂起芯片,使之便于 脫離藍(lán)膜;

2、Collect/Pick up head從上方吸起芯片,完成從Wafer 到L/F的運輸過程;

3、Collect以一定的力將芯片Bond在點有銀漿的L/F 的Pad上,具體位置可控;

4、Bond Head Resolution:X-0.2um;Y-0.5um;Z-1.25um;

5、Bond Head Speed:1.3m/s;

FOL– Epoxy Cure 銀漿固化

銀漿固化:

175°C,1個小時; N2環(huán)境,防止氧化:

Die Attach質(zhì)量檢查:

Die Shear(芯片剪切力)

FOL– Wire Bonding 引線焊接

利用高純度的金線(Au) 、銅線(Cu)或鋁線(Al)把 Pad 和 Lead通過焊接的方法連接起來。Pad是芯片上電路的外接 點,Lead是 Lead Frame上的 連接點。

W/B是封裝工藝中最為關(guān)鍵的一部工藝。

FOL– 3rd Optical Inspection三光檢查

EOL– End of Line后段工藝

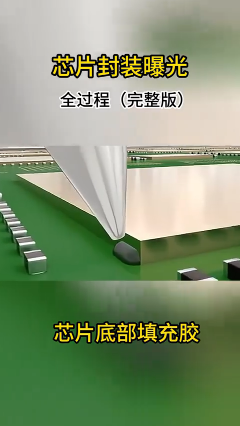

EOL– Molding(注塑)

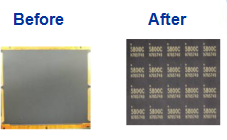

EOL– Laser Mark(激光打字)

在產(chǎn)品(Package)的正面或者背面激光刻字。內(nèi)容有:產(chǎn)品名稱,生產(chǎn)日期,生產(chǎn)批次等;

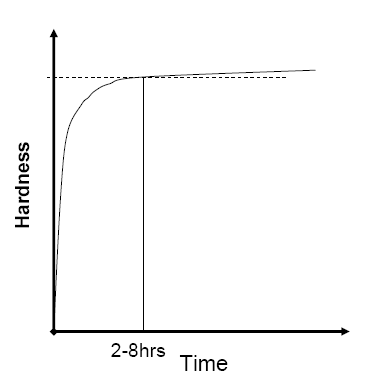

EOL– PostMold Cure(模后固化)

用于Molding后塑封料的固化,保護(hù)IC內(nèi)部結(jié)構(gòu),消除內(nèi)部應(yīng)力。Cure Temp:175+/-5°C;Cure Time:8Hrs

EOL– De-flash(去溢料)

目的:De-flash的目的在于去除Molding后在管體周圍Lead之間 多余的溢料; 方法:弱酸浸泡,高壓水沖洗;

EOL– Plating(電鍍)

利用金屬和化學(xué)的方法,在Leadframe的表面 鍍上一層鍍層,以防止外界環(huán)境的影響(潮濕 和熱)。并且使元器件在PCB板上容易焊接及 提高導(dǎo)電性。

電鍍一般有兩種類型:

Pb-Free:無鉛電鍍,采用的是>99.95%的高純 度的錫(Tin),為目前普遍采用的技術(shù),符合 Rohs的要求;

Tin-Lead:鉛錫合金。Tin占85%,Lead占 15%,由于不符合Rohs,目前基本被淘汰;

EOL– Post Annealing Bake(電鍍退火)

目的:讓無鉛電鍍后的產(chǎn)品在高溫下烘烤一段時間,目的在于 消除電鍍層潛在的晶須生長(Whisker Growth)的問題; 條件:150+/-5C; 2Hrs;

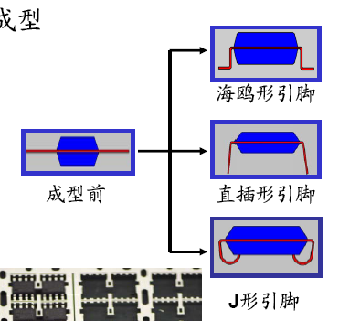

EOL– Trim&Form(切筋成型)

Trim:將一條片的Lead Frame切割成單獨的Unit(IC)的過程; Form:對Trim后的IC產(chǎn)品進(jìn)行引腳成型,達(dá)到工藝需要求的形狀, 并放置進(jìn)Tube或者Tray盤中;

EOL– Final Visual Inspection(第四道光檢)

在低倍放大鏡下,對產(chǎn)品外觀進(jìn)行檢查。主要針對EOL工藝可能產(chǎn)生的廢品:例如Molding缺陷,電鍍?nèi)毕莺蚑rim/Form缺陷等。

原文標(biāo)題:圖文解說:芯片IC的封裝/測試流程

文章出處:【微信公眾號:微波射頻網(wǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

責(zé)任編輯:haq

-

芯片

+關(guān)注

關(guān)注

459文章

52416瀏覽量

439487 -

測試

+關(guān)注

關(guān)注

8文章

5679瀏覽量

128686 -

IC

+關(guān)注

關(guān)注

36文章

6110瀏覽量

179083 -

封裝

+關(guān)注

關(guān)注

128文章

8630瀏覽量

145253

原文標(biāo)題:圖文解說:芯片IC的封裝/測試流程

文章出處:【微信號:mwrfnet,微信公眾號:微波射頻網(wǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

三分鐘帶你搞懂,芯片封裝的發(fā)展路徑!你知道封裝技術(shù)都有哪些嗎?#華芯邦 #芯片封裝 #封裝路徑 #芯片制造

芯片封測架構(gòu)和芯片封測流程

芯片封裝的核心材料之IC載板

數(shù)字設(shè)計ic芯片流程

IC測試基本原理與ATE測試向量生成

【「數(shù)字IC設(shè)計入門」閱讀體驗】+ 數(shù)字IC設(shè)計流程

一文了解芯片測試的重要性

芯片IC的封裝和測試流程是怎么樣的?

芯片IC的封裝和測試流程是怎么樣的?

評論