前言:本文我們介紹下ADC采樣時鐘的抖動(Jitter)參數對ADC采樣的影響,主要介紹以下內容:

時鐘抖動的構成

時鐘抖動對ADC SNR的影響

如何計算時鐘抖動

如何優化時鐘抖動

1.采樣理論

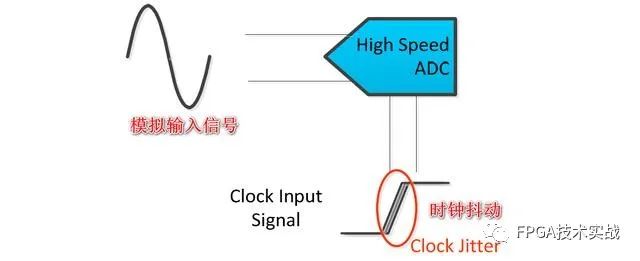

高速ADC使用外部輸入時鐘對模擬輸入信號進行采樣,如圖1所示。圖中顯示了輸入采樣時鐘抖動示意圖。

圖1、ADC采樣

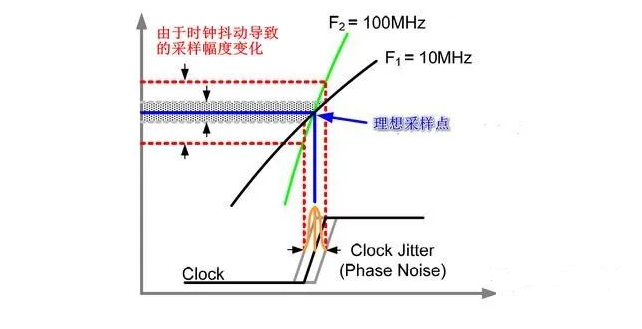

輸入模擬信號的頻率越高,由于時鐘抖動導致的采樣信號幅度變化越大,這點在圖2中顯示的非常明顯。輸入信號頻率為F2=100MHz時,采樣幅度變化如圖紅色虛線所示,明顯大于輸入信號F1=10MHz時采樣幅度的變化。

圖2、時鐘抖動對不同頻率輸入模擬信號的影響

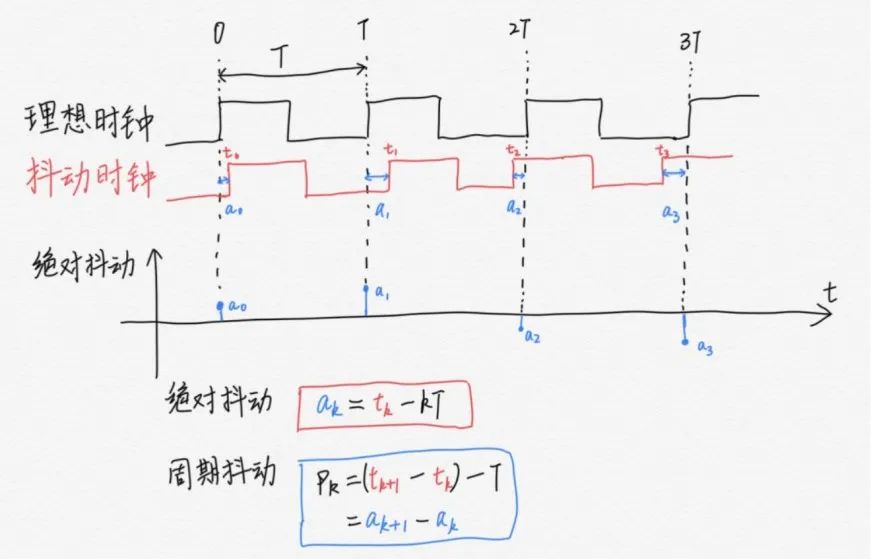

2.采樣時鐘抖動

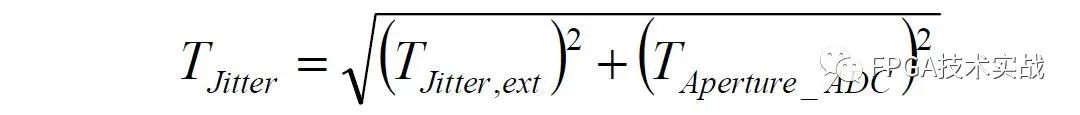

采樣時鐘抖動主要由兩部分組成:

外部輸入時鐘抖動

ADC孔徑抖動

圖3、時鐘抖計算公式

時鐘沿速率越快,帶來的時鐘抖動越小,同時也會增加PCB設計難度。

圖4、時鐘抖動構成

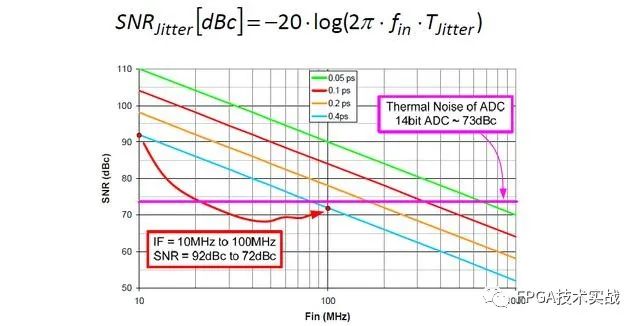

3.時鐘抖動對SNR的影響

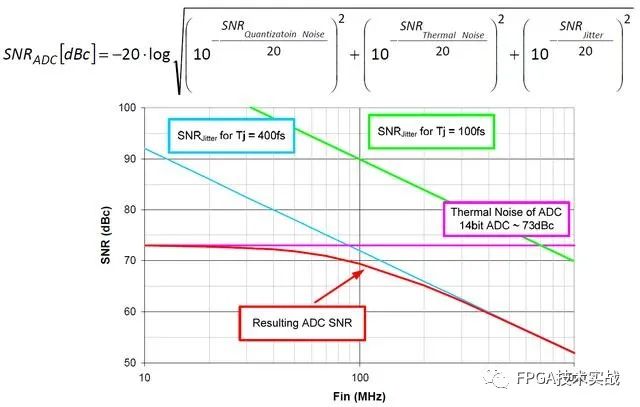

由于時鐘抖動對ADC信噪比SNR的影響由圖5所示公式計算。在圖5中,可以看到時鐘抖動對高頻模擬輸入信號影響更大。

圖5、時鐘抖動對SNR的影響

ADC噪聲下限SNR一般由三部分構成:

ADC量化噪聲

ADC熱噪聲

抖動衰減

圖6、ADC噪聲下限計算

4.計算抖動的幅度

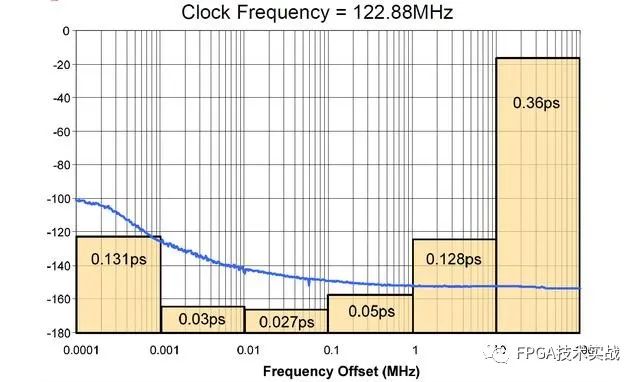

時鐘抖動通過對時鐘信號的相位噪聲進行積分運算得到。典型的計算應用要求如圖7所示。

圖7、典型的時鐘抖動計算要求

積分上限一般由以下因素限制:

時鐘濾波器帶寬

ADC時鐘輸入帶寬

ADC采樣速率

圖8、時鐘頻率偏移對應的抖動值

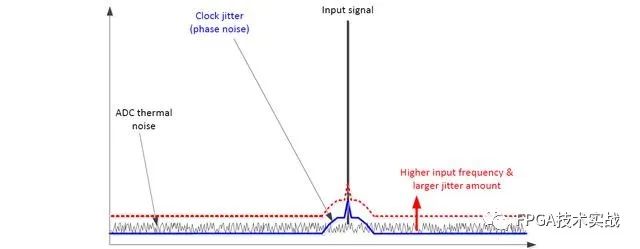

5.SRN在頻率的影響

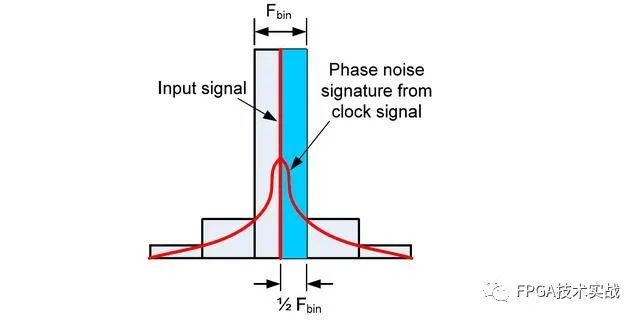

在采樣過程中,時鐘信號相位噪聲被加到輸入信號中。輸入信號頻率越高,相位噪聲幅度越大,越大的相位噪聲會導致越大的ADC噪聲下限惡化,降低ADC有效分辨率。

圖9、相位噪聲在頻率的頻譜圖

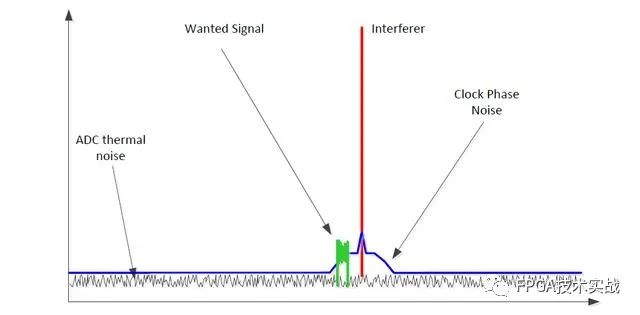

6.為什么時鐘抖動/相位噪聲如此關鍵

典型的接收機在“阻塞條件”下的性能包括兩個方面:

一是,接收機需要在噪聲背景下檢測出想要的小信號

二是,在帶內有大的干擾無法濾除,此干擾會影響小信號檢測

圖10、時鐘抖動增強帶內干擾影響

7.如何優化時鐘抖動性能

為了使給定ADC的信噪比性能最大化,系統設計者可以采取幾個步驟:

使用低抖動/相位噪聲時鐘源

使用低插入損耗的帶通濾波器限制寬帶噪聲衰減

確保時鐘振幅足夠且不會降低ADC孔徑抖動

編輯:jq

-

adc

+關注

關注

99文章

6682瀏覽量

549000 -

相位噪聲

+關注

關注

2文章

187瀏覽量

23285 -

SNR

+關注

關注

3文章

197瀏覽量

24952

原文標題:正確理解采樣時鐘抖動(Jitter)對ADC信噪比SNR的影響

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

收藏!一款高性能轉換器的設計指導

如何為ADC增加隔離而不損害其性能呢?

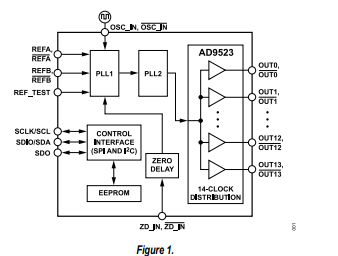

AD9523 14路輸出、低抖動時鐘發生器技術手冊

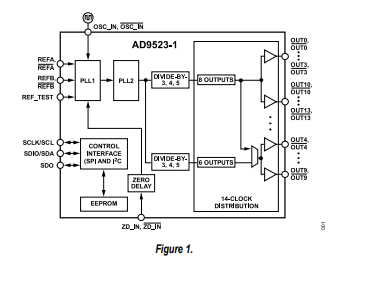

AD9523-1低抖動時鐘發生器,提供14路LVPECL/LVDS/HSTL輸出或29路LVCMOS輸出技術手冊

ADS8363的內部SAR ADC時鐘是否是由CLOCK引腳上輸入的時鐘信號提供的?

請問ADS131A04指標中的Normalized SNR如何理解?

周期性抖動例如電源上的抖動造成時鐘的Dj對 ENOB有影響嗎?如何計算這部分的影響?

抖動的概念和類型 量化時域抖動、隨機抖動和頻域抖動的方法

如何去正確理解采樣時鐘抖動(Jitter)對ADC信噪比SNR的影響

如何去正確理解采樣時鐘抖動(Jitter)對ADC信噪比SNR的影響

評論