從PC時代走向移動與AI時代,芯片的架構也從以CPU為中心走向了以數據為中心。AI帶來的考驗不僅包括芯片算力,也包括內存帶寬。縱使DDR和GDDR速率較高,在不少AI算法和神經網絡上,卻屢屢遇上內存帶寬上的限制,主打大帶寬的HBM也就順勢成了數據中心、HPC等高性能芯片中首選的DRAM方案。

當下JEDEC還沒有給出HBM3標準的最終定稿,但參與了標準制定工作的IP廠商們已經紛紛做好了準備工作。不久前,Rambus就率先公布了支持HBM3的內存子系統,近日,新思科技也公布了業界首個完整HBM3 IP與驗證方案。

IP廠商先行

早在今年初,SK海力士就對HBM3內存產品的性能給出了前瞻,稱其帶寬大于665 GB/s,I/O速度大于5.2Gbps,不過這只是一個過渡的性能。同在今年,IP廠商公布的數據進一步拉高了上限。比如Rambus公布HBM3內存子系統中,I/O速度高達8.4Gbps,內存帶寬最高可至1.075TB/s。

今年6月,臺灣創意電子發布了基于臺積電CoWoS技術的AI/HPC/網絡平臺,搭載了的HBM3控制器與PHY IP,I/O速度最高達到7.2Gbps。創意電子還在申請一項中介層布線專利,支持任何角度的鋸齒形布線,可將HBM3 IP拆分至兩個SoC上使用。

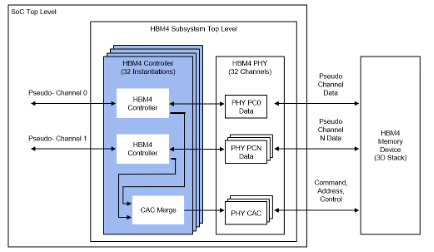

新思科技公布的完整HBM3 IP方案為2.5D多晶片封裝系統提供了控制器、PHY和驗證IP,稱設計者可在SoC中用到低功耗更大帶寬的內存。新思的DesignWare HBM3控制器與PHY IP基于經芯片驗證過的HBM2E IP打造,而HBM3 PHY IP基于5nm制程打造,每個引腳的速率可達7200 Mbps,內存帶寬最高可提升至921GB/s。

封裝加成

以上還只是單層HBM的數據,通過2.5D封裝堆疊2層或者4層后,內存帶寬也將成倍突破。以英偉達的A100加速器為例,英偉達首發的80GB版本采用了4層HBM2達到了1.6TB/s的帶寬,之后推出了5層HBM2E的版本,進一步將帶寬提高至2TB/s。而這樣的帶寬表現,只需2層HBM3即可實現,四五層的配置更是遠超市面上已有的內存規格。

此外,邏輯+HBM的方法已經不新鮮了,已經有不少GPU和服務器芯片都采用了類似的設計。然而隨著晶圓廠不斷在2.5D封裝技術上發力,單個芯片上HBM的數量也在增加。比如上文中提到的臺積電CoWoS技術,可在SoC芯片中集成4個以上的HBM,英偉達的P100就集成了4個HBM2,而NEC的Sx-Aurora向量處理器則集成了6個HBM2。

三星也在開發下一代的I-Cube 2.5D封裝技術,除了支持集成4到6個HBM以外,也在開發兩個邏輯晶片+8個HBM的I-Cube 8方案。類似的2.5D封裝技術還有英特爾的EMIB,但不過HBM主要用于其Agilex FPGA。

結語

目前美光、三星、SK海力士等內存廠商都已經在紛紛跟進這一新的DRAM標準,SoC設計廠商Socionext與新思合作,在其多晶片的設計中引入HBM3,除了必定支持的x86架構外,Arm的Neoverse N2平臺也已計劃了對HBM3的支持,SiFive的RISC-V SoC也加入了HBM3 IP。但即便JEDEC沒有“卡殼”,在年末的關頭發布了HBM3正式標準,我們也可能要等到2022年下半年才能見到HBM3相關產品的面世。

大家都已經在不少高性能芯片上見到了HBM2/2E的身影,尤其是數據中心應用,比如英偉達的Tesla P100/V100、AMD的Radeon Instinct MI25、英特爾的Nervana神經網絡處理器以及谷歌的TPU v2等等。

消費級應用卻似乎正在與HBM漸行漸遠,過去還有AMD的Radeon RxVega64/Vega 56以及英特爾的KabyLake-G這樣利用了HBM的圖形產品,再高一級也有英偉達的Quaddro GP100/GV100和AMD的Radeon Pro WX這樣的專業繪圖GPU。

如今這些產品都用回了GDDR DRAM,畢竟消費級應用目前尚未出現帶寬瓶頸,速率和成本反倒才是芯片制造商最看重的,而HBM3在優點上提及了更大帶寬更高的功效,卻并沒有降低成本。

當下JEDEC還沒有給出HBM3標準的最終定稿,但參與了標準制定工作的IP廠商們已經紛紛做好了準備工作。不久前,Rambus就率先公布了支持HBM3的內存子系統,近日,新思科技也公布了業界首個完整HBM3 IP與驗證方案。

IP廠商先行

早在今年初,SK海力士就對HBM3內存產品的性能給出了前瞻,稱其帶寬大于665 GB/s,I/O速度大于5.2Gbps,不過這只是一個過渡的性能。同在今年,IP廠商公布的數據進一步拉高了上限。比如Rambus公布HBM3內存子系統中,I/O速度高達8.4Gbps,內存帶寬最高可至1.075TB/s。

今年6月,臺灣創意電子發布了基于臺積電CoWoS技術的AI/HPC/網絡平臺,搭載了的HBM3控制器與PHY IP,I/O速度最高達到7.2Gbps。創意電子還在申請一項中介層布線專利,支持任何角度的鋸齒形布線,可將HBM3 IP拆分至兩個SoC上使用。

新思科技公布的完整HBM3 IP方案為2.5D多晶片封裝系統提供了控制器、PHY和驗證IP,稱設計者可在SoC中用到低功耗更大帶寬的內存。新思的DesignWare HBM3控制器與PHY IP基于經芯片驗證過的HBM2E IP打造,而HBM3 PHY IP基于5nm制程打造,每個引腳的速率可達7200 Mbps,內存帶寬最高可提升至921GB/s。

封裝加成

以上還只是單層HBM的數據,通過2.5D封裝堆疊2層或者4層后,內存帶寬也將成倍突破。以英偉達的A100加速器為例,英偉達首發的80GB版本采用了4層HBM2達到了1.6TB/s的帶寬,之后推出了5層HBM2E的版本,進一步將帶寬提高至2TB/s。而這樣的帶寬表現,只需2層HBM3即可實現,四五層的配置更是遠超市面上已有的內存規格。

此外,邏輯+HBM的方法已經不新鮮了,已經有不少GPU和服務器芯片都采用了類似的設計。然而隨著晶圓廠不斷在2.5D封裝技術上發力,單個芯片上HBM的數量也在增加。比如上文中提到的臺積電CoWoS技術,可在SoC芯片中集成4個以上的HBM,英偉達的P100就集成了4個HBM2,而NEC的Sx-Aurora向量處理器則集成了6個HBM2。

三星也在開發下一代的I-Cube 2.5D封裝技術,除了支持集成4到6個HBM以外,也在開發兩個邏輯晶片+8個HBM的I-Cube 8方案。類似的2.5D封裝技術還有英特爾的EMIB,但不過HBM主要用于其Agilex FPGA。

結語

目前美光、三星、SK海力士等內存廠商都已經在紛紛跟進這一新的DRAM標準,SoC設計廠商Socionext與新思合作,在其多晶片的設計中引入HBM3,除了必定支持的x86架構外,Arm的Neoverse N2平臺也已計劃了對HBM3的支持,SiFive的RISC-V SoC也加入了HBM3 IP。但即便JEDEC沒有“卡殼”,在年末的關頭發布了HBM3正式標準,我們也可能要等到2022年下半年才能見到HBM3相關產品的面世。

大家都已經在不少高性能芯片上見到了HBM2/2E的身影,尤其是數據中心應用,比如英偉達的Tesla P100/V100、AMD的Radeon Instinct MI25、英特爾的Nervana神經網絡處理器以及谷歌的TPU v2等等。

消費級應用卻似乎正在與HBM漸行漸遠,過去還有AMD的Radeon RxVega64/Vega 56以及英特爾的KabyLake-G這樣利用了HBM的圖形產品,再高一級也有英偉達的Quaddro GP100/GV100和AMD的Radeon Pro WX這樣的專業繪圖GPU。

如今這些產品都用回了GDDR DRAM,畢竟消費級應用目前尚未出現帶寬瓶頸,速率和成本反倒才是芯片制造商最看重的,而HBM3在優點上提及了更大帶寬更高的功效,卻并沒有降低成本。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

內存

+關注

關注

8文章

3118瀏覽量

75193 -

HBM

+關注

關注

2文章

409瀏覽量

15209 -

HBM3

+關注

關注

0文章

74瀏覽量

319

發布評論請先 登錄

相關推薦

熱點推薦

風景獨好?12層HBM3E量產,16層HBM3E在研,產業鏈涌動

電子發燒友網報道(文/黃晶晶)在早前的報道中,對于HBM產能是否即將過剩,業界有不同的聲音,但絲毫未影響存儲芯片廠商對HBM產品升級的步伐。 ? 三大廠商12 層HBM3E 進展 ? 9月26日SK

HBM3E量產后,第六代HBM4要來了!

電子發燒友網報道(文/黃晶晶)眼下各家存儲芯片廠商的HBM3E陸續量產,HBM4正在緊鑼密鼓地研發,從規格標準到工藝制程、封裝技術等都有所進展,原本SK海力士計劃2026年量產HBM4

HBM格局生變!傳三星HBM3量產供貨英偉達,國內廠商積極布局

電子發燒友網報道(文/吳子鵬)根據韓媒sedaily 的最新報道,三星華城17號產線已開始量產并向英偉達供應HBM3內存。同時,美光已經為英偉達供應HBM3E。至此,高端HBM內存的供應由SK海力士

三星在4nm邏輯芯片上實現40%以上的測試良率

三星電子在 HBM3 時期遭遇了重大挫折,將 70% 的 HBM 內存市場份額拱手送給主要競爭對手 SK 海力士,更是近年來首度讓出了第一大 DRAM 原廠的寶座。這迫使三星在 HBM4 上采用

發表于 04-18 10:52

三星與英偉達高層會晤,商討HBM3E供應

其高帶寬存儲器HBM3E產品中的初始缺陷問題,并就三星第五代HBM3E產品向英偉達供應的相關事宜進行了深入討論。 此次高層會晤引發了外界的廣泛關注。據推測,三星8層HBM3E產品的質量認證工作已接近尾聲,這標志著三星即將正式邁入

三星電子將供應改良版HBM3E芯片

三星電子在近期舉行的業績電話會議中,透露了其高帶寬內存(HBM)的最新發展動態。據悉,該公司的第五代HBM3E產品已在2024年第三季度實現大規模生產和銷售,并在第四季度成功向多家GPU廠商及數據中心供貨。與上一代HBM3相比,

AWG電纜線規的標準定義

AWG(American wire gauge)電纜線規的標準定義如下: 一、基本概念 AWG是美國線規的簡稱,是一種區分導線直徑的標準,也被稱為Brown & Sharpe線規。這種標準化線規系統

蔚來與萬事達卡簽署戰略合作協議

近日,蔚來與萬事達卡在上海簽署戰略合作協議。蔚來聯合創始人、總裁秦力洪,萬事達卡全球執行副總裁兼大中華區總裁常青出席簽約儀式。蔚來商業資源管理副總裁胡崖音與萬事達卡中國區零售和商業總經理張昊代表雙方簽約。

蔚來與萬事達卡達成戰略合作

近日,蔚來與全球知名支付品牌萬事達卡在上海正式簽署了戰略合作協議。此次合作標志著雙方在用戶增值服務、支付創新、數據服務與咨詢、聯合營銷以及ESG(環境、社會和公司治理)等多個領域將展開全方位、多層次

Rambus宣布推出業界首款HBM4控制器IP,加速下一代AI工作負載

基于一百多項HBM成功設計案例,確保芯片一次流片成功 在低延遲下提供超過HBM3兩倍的吞吐量,滿足生成式AI和高性能計算(HPC)工作負載的需求 擴展了業界領先的高性能內存解決方案的半導體IP

發表于 11-13 15:36

?754次閱讀

SK海力士推出48GB 16層HBM3E產品

近日在一次科技展覽上,SK海力士驚艷亮相,展出了全球首款48GB 16層HBM3E(High Bandwidth Memory 3E)產品。這一突破性產品不僅展示了SK海力士在高端存儲技術領域

三星或將HBM產能目標下調至每月17萬顆

據業內人士透露,三星電子已對其2025年底的高帶寬內存(HBM)最大產能目標進行了調整,下調幅度超過10%,從原先計劃的每月20萬顆減至17萬顆。這一變動主要歸因于向主要客戶的量產供應遭遇延遲,導致三星對其尖端的

萬能斷路器欠壓線圈的工作原理是什么

萬能斷路器欠壓線圈的工作原理主要基于電磁感應和磁性材料的特性。以下是對其工作原理的解釋: 一、基本組成 萬能斷路器中的欠壓線圈,也稱為欠電壓

三星HBM3e芯片量產在即,營收貢獻將飆升

三星電子公司近日宣布了一項重要計劃,即今年將全面啟動其第五代高帶寬存儲器(HBM)芯片HBM3e的量產工作,并預期這一先進產品將顯著提升公司的營收貢獻。據三星電子透露,隨著HBM3e芯片的逐步放量

報告稱HBM芯片明年月產能突破54萬顆

,受SK海力士、三星、美光三大行業巨頭強力推動,2025年HBM芯片的月度總產能預計將飆升至54萬顆,與2024年相比,這一數字將激增27.6萬顆,同比增長率高達105%,標志著HBM

HBM3萬事俱備,只欠標準定稿

HBM3萬事俱備,只欠標準定稿

評論