過采樣與位分辨率

數(shù)字信號(hào)處理中提升有效位分辨率的方法

位(比特)分辨率與采樣率是模數(shù)轉(zhuǎn)換器(ADC)最重要的兩個(gè)參數(shù)。高位分辨率的ADC可以有效地減少由采樣造成的量化噪聲,從而提高整個(gè)數(shù)字信號(hào)處理(DSP)的質(zhì)量。大多數(shù)ADC擁有較為固定的位分辨率與采樣率。然而,某些依賴DSP的儀器,比如數(shù)字儲(chǔ)存示波器,可能需要用來接收不同頻段的輸入信號(hào)。因此,使用固定的采樣率與位分辨率進(jìn)行采樣在這類應(yīng)用很可能不是最優(yōu)的解決方案。在這份應(yīng)用指南中,我們將向您介紹如何通過 過采樣 的方式提高有效位分辨率。之后通過實(shí)驗(yàn)向您展示Moku:Lab與Moku:Go是如果通過其強(qiáng)大的機(jī)載運(yùn)算能力,在不同的使用場(chǎng)景下自動(dòng)使用過采樣來提升測(cè)量結(jié)果。

簡(jiǎn)介

在過去的幾十年中,半導(dǎo)體的制造工藝得到指數(shù)級(jí)的提升。單位面積下芯片半導(dǎo)體的數(shù)量也同樣得到了多個(gè)數(shù)量級(jí)的提升。許多信號(hào)處理的設(shè)備,比如音頻錄制與播放設(shè)備,都由模擬信號(hào)處理過渡到了信號(hào)數(shù)字處理。數(shù)字信號(hào)處理(DSP)通常有著更簡(jiǎn)單的結(jié)構(gòu):模數(shù)轉(zhuǎn)換器(ADC)首先將模擬信號(hào)轉(zhuǎn)換成數(shù)字信號(hào)。之后,DSP芯片對(duì)信號(hào)進(jìn)行實(shí)時(shí)處理,再通過數(shù)模轉(zhuǎn)換器(DAC)等設(shè)備輸出給其他裝置。許多儀器通過搭載特殊應(yīng)用集成電路(ASIC)來實(shí)現(xiàn)信號(hào)的處理。然而,現(xiàn)場(chǎng)可編程邏輯門陣列(FPGA)的飛速發(fā)展給我們提供了更加便捷的選項(xiàng)。通過ADC-DSP-DAC的設(shè)計(jì)思路,F(xiàn)PGA的可編程性允許我們將不同的DSP算法部署到同一個(gè)硬件上。Liquid Instruments的Moku實(shí)驗(yàn)平臺(tái)搭載了Xilinx的SoC/FPGA作為核心芯片,可將多達(dá)12種不同的測(cè)試測(cè)量儀器集成到一個(gè)硬件平臺(tái)上。通過簡(jiǎn)單的操作,用戶可以在數(shù)秒內(nèi)切換不同的儀器。Moku平臺(tái)的高集成度與快速切換儀器的特性,使其無論是在本科實(shí)驗(yàn)室教學(xué),科研院所,還是商業(yè)產(chǎn)品研發(fā)中都能提供平滑,無縫的用戶體驗(yàn)。

模數(shù)轉(zhuǎn)換是高質(zhì)量測(cè)量的重要環(huán)節(jié)。ADC通常對(duì)一個(gè)輸入電壓進(jìn)行采樣,然后將這個(gè)電壓轉(zhuǎn)換成一個(gè)固定位數(shù)的二進(jìn)制數(shù)。采樣的速度(采樣率)與輸出的位數(shù)是ADC最重要的兩個(gè)特征值。更高的位數(shù)通常可以使得模擬信號(hào)被更精確的轉(zhuǎn)換并表達(dá)。比如,如果我們有一個(gè)2 Vpp的輸入范圍,一個(gè)8位的ADC最小的量化步驟為 mV。如果我們使用一個(gè)12位的ADC,則最小量化步驟可以被減小到 mV。因此,更高的位數(shù)可以給我們提供更精確的測(cè)量結(jié)果。然而,更高的ADC位數(shù)會(huì)增大整個(gè)DSP的數(shù)據(jù)吞吐量。當(dāng)我們的DSP擁有固定運(yùn)算能力的時(shí)候,ADC最高的位數(shù)通常會(huì)被其最高采樣率所限制。但當(dāng)輸入信號(hào)頻率較低時(shí)(不需要以最高的采樣率進(jìn)行采樣時(shí)),一部分的運(yùn)算能力又可能被浪費(fèi)。為了提高DSP的運(yùn)算效率,過采樣技術(shù)被運(yùn)用到了Moku平臺(tái)中。通過過采樣,我們可以犧牲一部分的采樣率來換取更高的有效位數(shù)(ENOB),保證芯片的運(yùn)算能力被最有效的利用。我們將向您介紹如何通過 過采樣 的方式提高有效位分辨率。之后通過實(shí)驗(yàn)向您展示Moku:Lab與Moku:Go是如果通過其強(qiáng)大的機(jī)載運(yùn)算能力,在不同的使用場(chǎng)景下自動(dòng)使用過采樣來提升測(cè)量結(jié)果。

圖1:Liquid Instruments 搭載FPGA的Moku:Go(左)與Moku:Lab(右)的測(cè)試測(cè)量平臺(tái)。

過采樣的直觀認(rèn)識(shí)

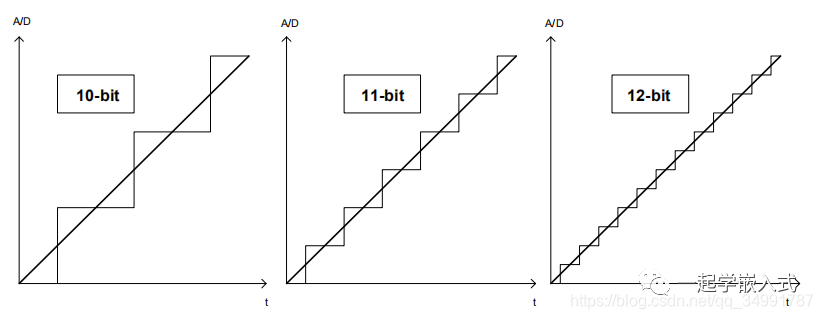

過采樣在時(shí)間軸上,對(duì)n個(gè)采樣點(diǎn)取平均數(shù),之后再將這一個(gè)平均后的單一數(shù)據(jù)點(diǎn)發(fā)送給后續(xù)的數(shù)字信號(hào)處理流程中。這一過程會(huì)使有效采樣率下降n倍。要對(duì)過采樣有一個(gè)直觀的認(rèn)識(shí),首先我們來復(fù)習(xí)一下ADC的基本知識(shí)。

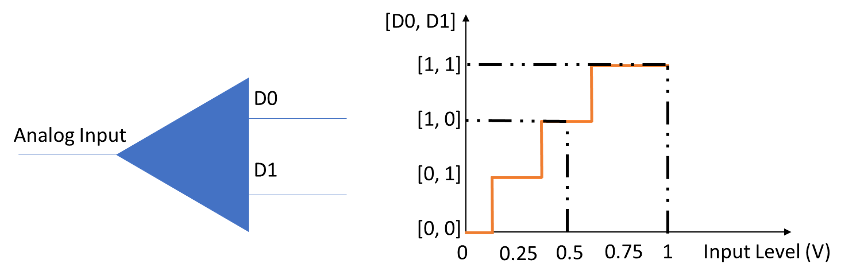

ADC在指定的頻率下測(cè)量一個(gè)模擬輸入(Analog Input)的電壓值,并將所測(cè)得的電壓值根據(jù)輸入電壓的大小轉(zhuǎn)換成一個(gè)二進(jìn)制數(shù)。假設(shè)我們有一個(gè)2位的ADC,它的輸入范圍為0到1 V。圖2中,我們展示了一個(gè)簡(jiǎn)化的ADC結(jié)構(gòu)圖(左),以及根據(jù)輸入電壓(x軸)所產(chǎn)生的二進(jìn)制數(shù)輸出(y軸)。

圖2: 一個(gè)簡(jiǎn)化版的2位ADC(左),與其所對(duì)應(yīng)的輸入輸出值(右)。

我們假設(shè)這個(gè)ADC,在 0 到 0.125 V, 0.125 到 0.375 V, 0.375 到 0.625 V,0.625 到 1 V 的輸入范圍內(nèi),分別對(duì)應(yīng)產(chǎn)生[0, 0], [0, 1],[1 ,0], 與[1, 1]數(shù)字信號(hào)。如果我們的系統(tǒng)從這個(gè)ADC中得到了[1, 0]的輸出,我們估計(jì)輸入的信號(hào)為0.5 V。假設(shè)實(shí)際的輸入信號(hào)為0.4 V,那么在這個(gè)過程中,系統(tǒng)產(chǎn)生了0.1 V的量化誤差。這個(gè)量化誤差可以通過提高有效位寬得以減小。

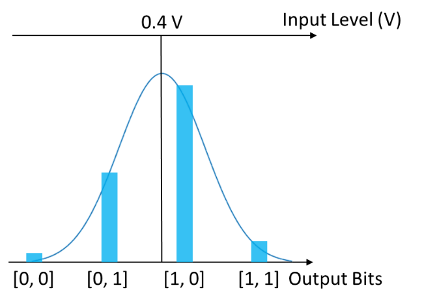

現(xiàn)在,讓我們來看一下平均如何幫助我們提高分辨率的。在實(shí)際場(chǎng)景中,ADC的輸入電壓與讀取包含了一定輸入噪聲。在這個(gè)展示中,我們假設(shè)噪聲為高斯形狀的白噪聲,并且中心值為0.4 V。通過多次采樣,我們可以構(gòu)建一個(gè)所得二進(jìn)制數(shù)輸出的直方圖。

圖3:0.4 V為中心,高斯型狀噪聲的信號(hào)演示圖。藍(lán)色的直方圖展示了多次采樣后,一種可能的ADC輸出分布。

從圖中可以看出,盡管大多數(shù)采樣點(diǎn)都落在了[1, 0],然而依然有一些采樣點(diǎn)落在了其他區(qū)域中。如果我們?nèi)∑骄担涂梢缘贸鰧?shí)際電壓在0.25 V和0.5 V之間,并更趨近于0.5 V。因此,通過多次采樣(過采樣),我們可以對(duì)輸入電壓的實(shí)際值有更好的預(yù)估,打破原有的位數(shù)限制。

然而,在這個(gè)過程中我們做了以下假設(shè):首先,輸入的信號(hào)或ADC本身所產(chǎn)生的噪聲為高斯白噪聲。而且,這個(gè)噪聲本身超出了相鄰的兩個(gè)數(shù)位的檢測(cè)界限。如果這些條件不能達(dá)成,則過采樣可能并不能有效提高分辨率。

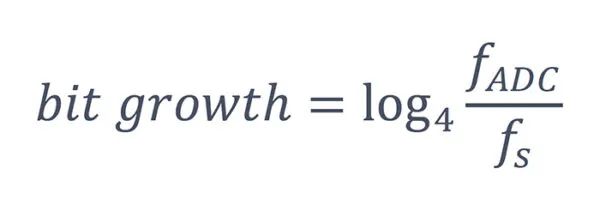

過采樣對(duì)分辨率的影響可以通過下面的公式來表述,其中 是ADC原有的采樣率, 為過采樣之后的有效采樣率。

有關(guān)這個(gè)公式的具體推導(dǎo),請(qǐng)參見下列書籍:

Li, Tan. Digital Signal Processing. Academic Press, 2008

過采樣在Moku當(dāng)中的應(yīng)用

過采樣在許多Moku的儀器中,會(huì)根據(jù)用戶的設(shè)置自動(dòng)啟動(dòng)。在這個(gè)應(yīng)用指南中,我們將展示Moku:Go的數(shù)據(jù)記錄儀與PID控制器是如何通過過采樣來提高測(cè)量質(zhì)量的。

Moku:Go數(shù)據(jù)記錄儀

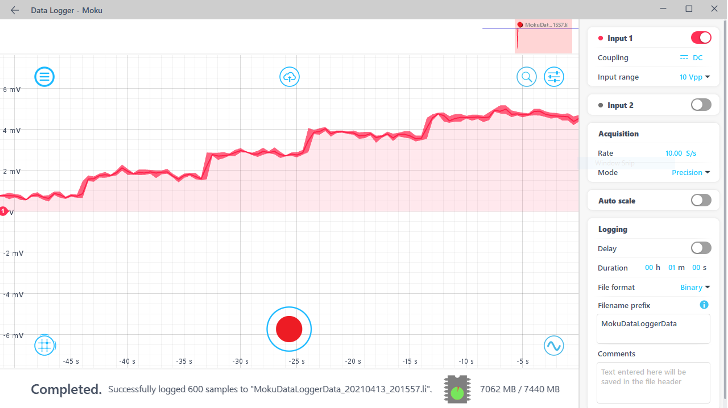

Moku:Go本身搭載了12位的ADC,擁有10或者50 Vpp的輸入范圍。在10 Vpp的范圍下,理論最小量化步驟為10/212,大約為2.44 mV。通過選擇Precision(精準(zhǔn))模式,數(shù)據(jù)記錄儀會(huì)自動(dòng)過采樣以提供更高的分辨率。我們將一個(gè)波形發(fā)生器的輸出連入Moku:Go,輸入一個(gè)0 V直流信號(hào)。然后,我們每10秒增加1 mV的電壓,并使用數(shù)據(jù)記錄儀在10 Sa/s的采樣率下記錄數(shù)據(jù)。

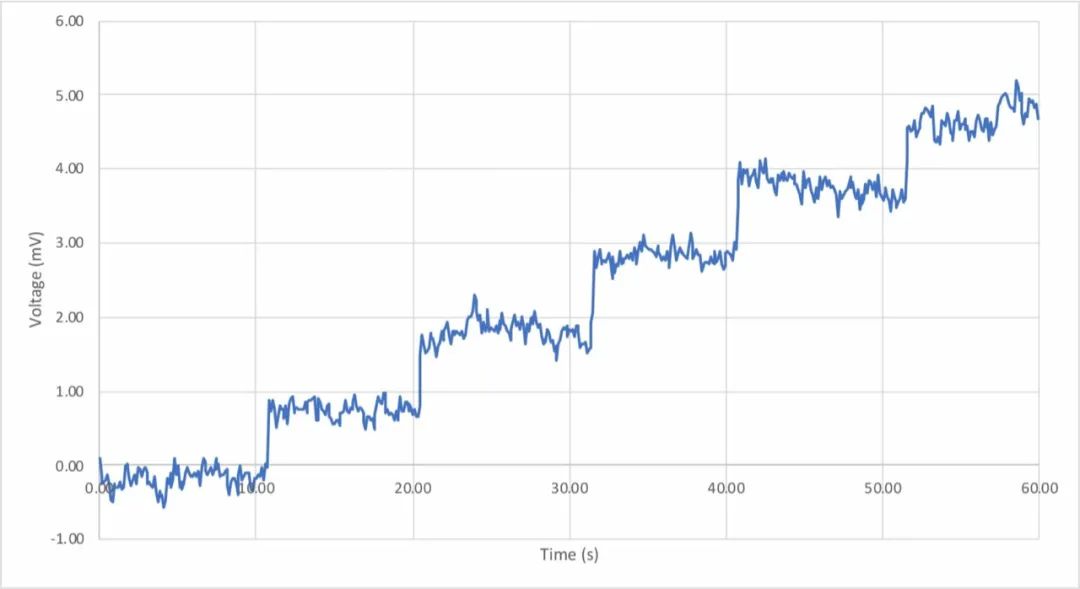

圖4: 通過Moku:Go數(shù)據(jù)記錄儀記錄1 mV階梯形狀信號(hào)。

所采集的數(shù)據(jù)被轉(zhuǎn)存為.csv格式發(fā)送到電腦中。所測(cè)得的電壓被繪制到了下圖中。我們可見,雖然ADC自身只有12位的分辨率,然后儀器依然可以解析1 mV的增長(zhǎng)。

圖5:數(shù)據(jù)記錄儀準(zhǔn)確記錄了1 mV的增長(zhǎng)。

Moku:Go PID控制器

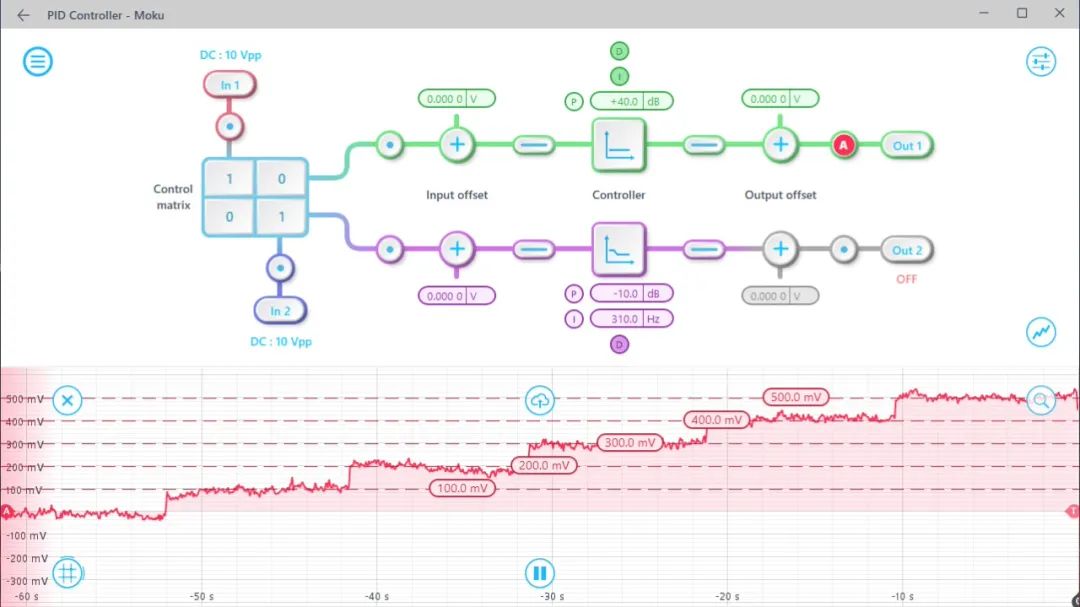

PID控制器是閉環(huán)控制中常用到的元件。Moku:Go所搭載的FPGA可使其擁有在20 kHz小于30°的輸入輸出延時(shí),可用來控制一些高帶寬設(shè)備。由于輸入輸出延時(shí),Moku的PID可以遠(yuǎn)小于125 MSa/s的速率進(jìn)行采樣。這樣可以提高大約2位的分辨率,使其可以分辨1 mV的信號(hào)。在這個(gè)實(shí)驗(yàn)中,我們將演示Moku:Go的PID是如何自動(dòng)應(yīng)用過采樣的。我們關(guān)閉I與D控制器,并將P控制器調(diào)節(jié)到40 dB的增益。這樣,任何輸入信號(hào)都會(huì)被放大100倍。我們?cè)俅屋斎雸D5中所展示的1 mV階梯信號(hào),并通過PID自帶的觀測(cè)點(diǎn)觀察輸出(圖6)。

圖6:Moku:Go PID自動(dòng)過采樣輸入信號(hào),并將信號(hào)再放大100倍后,以100 mV的增長(zhǎng)輸出。

輸出的信號(hào)被展示在內(nèi)置的示波器中。我們可以看到,盡管ADC的自身分辨率只有2.44 mV,PID依然可以解析1 mV的信號(hào)。

結(jié)論

過采樣是一種通過調(diào)節(jié)采樣率,有效提升DSP有效位分辨率的方法。Moku設(shè)備依托于其強(qiáng)大的FPGA信號(hào)處理能力,自動(dòng)將這一個(gè)方法應(yīng)用到諸多儀器中,有效的提高了測(cè)量的準(zhǔn)確性和精度。

原文標(biāo)題:【分享】數(shù)字信號(hào)處理中提升有效位分辨率的方法

文章出處:【微信公眾號(hào):貝思科爾】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

459文章

52355瀏覽量

438730 -

adc

+關(guān)注

關(guān)注

99文章

6671瀏覽量

548724 -

測(cè)量

+關(guān)注

關(guān)注

10文章

5215瀏覽量

113144

原文標(biāo)題:【分享】數(shù)字信號(hào)處理中提升有效位分辨率的方法

文章出處:【微信號(hào):BasiCAE,微信公眾號(hào):貝思科爾】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

通過ADC的過采樣提高測(cè)量的分辨率

ADC的噪聲、ENOB及有效分辨率

示波器的垂直分辨率相關(guān)知識(shí)分享

SAR adc 為什么經(jīng)過過采樣和噪聲整形以后能有10+的有效位數(shù)?

采樣頻率與分辨率分別是什么

峰峰值分辨率與有效分辨率

通過過采樣提高SOC單片機(jī)片內(nèi)A_D分辨率

利用過采樣技術(shù)提高ADC測(cè)量分辨率

如何通過過采樣的方式提高有效位分辨率

如何通過過采樣的方式提高有效位分辨率

評(píng)論