什么是低電平有效

首先這是一個輸入引腳才存在有效這個溫暖體。低電平有效表示這個當這個引腳上電壓為低(0-2V)時,這個腳的功能觸發(當然要把引腳功能選擇為對應的功能)。

為什么要低電平有效

在數字系統中,比較容易出現在低電平上疊加一個噪聲正脈沖。如果采用高電平有效的方式,就可能在無效的低電平上,出現高電平噪聲,從而使某個信號在不應當有效的時候,出現有效的高電平。而在高電平上,出現一個負噪聲脈沖,從而導致某個信號在不應當有效的時候,出現有效的低電平的幾率,要小得多。所以在數字系統中,大多數信號的有效電平為低電平。

且低電平時電路的阻抗低,噪聲造成的電平變化小,也就是說,抗干擾能力更強。

本文綜合整理自nereus78e904、fml003、xiaofeng06、盲文

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

脈沖

+關注

關注

20文章

901瀏覽量

97076 -

引腳

+關注

關注

16文章

1676瀏覽量

52668 -

低電平

+關注

關注

1文章

177瀏覽量

13644

發布評論請先 登錄

相關推薦

熱點推薦

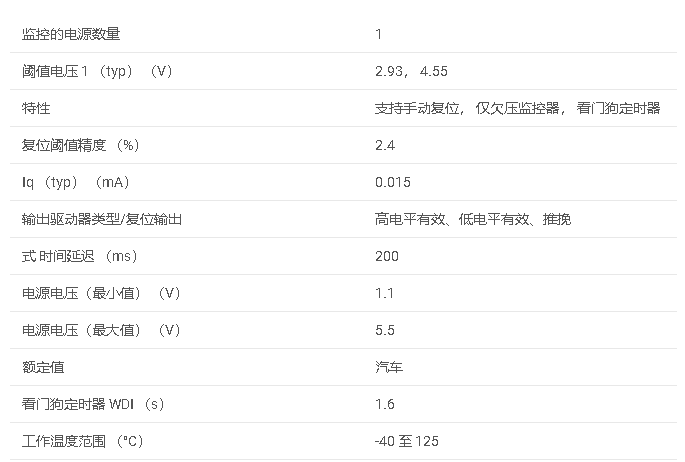

TPS3824-Q1 高電平和低電平有效,汽車電壓監控器(復位IC)帶看門狗和手動復位技術手冊

閾值電壓 VIT? 以下,電源電壓監控器就會監控 VDD 并保持 RESET 低電平。內部定時器延遲輸出返回到非活動狀態 (高),以驗證系統復位是否正確。延遲時間 td 在 VDD 上升到閾值電壓 VIT - 以上后開始。當電源電壓降至閾值電壓 VIT? 以下時,輸出再次變為有效

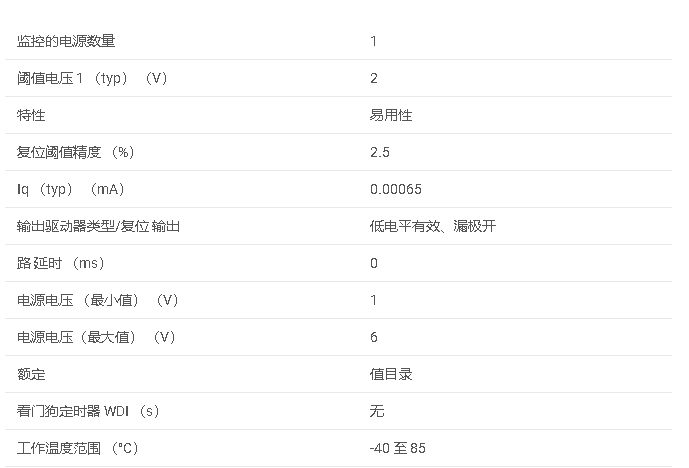

LM8364系列 具有低靜態電流和2.5%閾值精度的低電平有效監視器數據手冊

LM8364 系列是微功率欠壓傳感電路,非常適合用于 基于電池供電的微處理器系統,其中延長電池壽命是關鍵 要求。

閾值電壓范圍為 2.0V 至 4.5V,低電平有效開路 drain 輸出。這些

THS1206寫使能是下降沿有效,還是低電平有效?

在向THS1206寫控制字時,要寫四次。

開始按照寫使能,然后連續寫四次數據,結果控制字沒寫進去;

寫使能,寫一次數據后關閉寫使能,第二次寫時再打開寫使能,這樣依次寫四次,控制字才寫入。

請問為什么呢?不知道寫使能是下降沿有效,還是低

發表于 02-14 08:09

TTL電平與低電平信號的區別

在數字電子學中,信號的傳輸和處理依賴于電壓水平來表示邏輯狀態。TTL電平和低電平信號是兩種常見的電壓水平,它們在數字電路中扮演著重要的角色。 TTL電平 TTL電平是一種廣泛使用的數字

為什么ISO7230M輸入高電平時輸出確偶發了低電平?

示波器通道1監測輸入通道A(input)一直為高電平,高電平時偶爾有干擾,但是示波器通道2監測輸出通道A(output)由高電平變為了低電平。而低

發表于 01-13 06:52

低電平靈敏專用儀器的技術原理和應用場景

放大電路:為了將微弱的電信號放大到可測量的范圍,低電平靈敏專用儀器內部配備了精密的放大電路。這些放大電路具有低噪聲、低失真和高增益的特點,能夠有效地放大信號并保持其原始特性。

先進的信號處理技術

發表于 12-06 14:45

利用低電平有效輸出驅動高端輸入開關

,斷開系統電源,然后再次連接電源以重啟系統。本文將探討使用什么方法和技術可以監控電路的低電平有效輸出來驅動高端輸入開關,從而執行系統電源循環。

高電平輸入和低電平輸入是什么意思

在現代電子系統中,數字電路扮演著至關重要的角色。這些電路處理的是二進制信號,即由邏輯“1”和邏輯“0”組成的信號。這些邏輯狀態通常通過電壓水平來表示,其中高電平代表邏輯“1”,低電平代表邏輯“0

rca輸出是低電平還是高電平

(黃色插頭)。這些連接器通常用于連接家庭影院系統、音響設備、游戲機和其他多媒體設備。 關于RCA輸出是低電平還是高電平,這實際上是一個關于信號電平的問題。在電子學中,電平通常指的是信號

雙色led燈的引腳為高電平還是低電平

雙色LED燈的引腳電平(高電平或低電平)取決于其電路設計和控制方式。雙色LED燈通常包含兩個LED芯片(如紅色和綠色),它們共用一個引腳(共陰或共陽),另外兩個引腳則分別控制這兩個LED芯片的開關。

芯片引腳懸空是高電平還是低電平

芯片引腳懸空時的電平狀態(高電平或低電平)并不是一個固定答案,它取決于多個因素,包括芯片類型、生產廠家、引腳特性以及周圍電路環境等。 首先,從邏輯門電路的角度來看,當引腳懸空時,其電平

請問如何將CD74HC154這個譯碼器的低電平輸出轉換為高電平有效呢?

請問如何將CD74HC154這個譯碼器的低電平輸出轉換為高電平有效呢?初步考慮是給輸出接一個反相器,如CD4069。或者有直接高電平輸出

發表于 08-09 06:11

高電平和低電平輸入有什么區別

在數字電子學中,高電平和低電平是兩種基本的信號狀態,它們分別代表二進制數字1和0。這兩種電平狀態在數字電路設計、通信和計算機系統中扮演著至關重要的角色。 高電平和

clk是高電平有效還是低電平有效

在數字電路中,"clk"通常指的是時鐘信號(clock signal),它是一種周期性的信號,用于同步數字電路中的各種操作。時鐘信號的高低電平有效性取決于具體的電路設計和應用場景。 1. 時鐘信號

低電平復位脈沖寬度有沒有要求? 給低電平后需要延時多久合適?

低電平復位脈沖寬度有沒有要求? 給低電平后需要延時多久合適?

另外復位的時候如果我給的低電平持續時間很長,比如說1s,會不會導致這期間重復復位?

發表于 07-19 14:22

什么是低電平有效?為什么要低電平有效呢

什么是低電平有效?為什么要低電平有效呢

評論