從2020.2開始,XRT提供了新的Native API,以區別行業標準OpenCL API的,在FPGA加速應用上,兩者都是可以使用的。XRT Native API的優勢是更加契合FPGA加速應用,而OpenCL的優勢則是平臺通用性比較好。

XRT Native API里面有兩個API比較有意思,可能會產生混淆,一個是xrt_kernel,另一個是xrt_ip。IP這個概念,在FPGA中還是比較常用的,典型的就是IP catalog里面的IP,當然這次講到的IP更傾向于custom IP,即用戶自定義IP(以下略作IP)。無論使用Vitis_hls, V++,Package_xo中哪種生成方法,最后生成的kernel的端口類型都是固定的,另外控制端口AXI_LITE的寄存器配置也是保持固定的(當然會因參數數量不同而變化)。

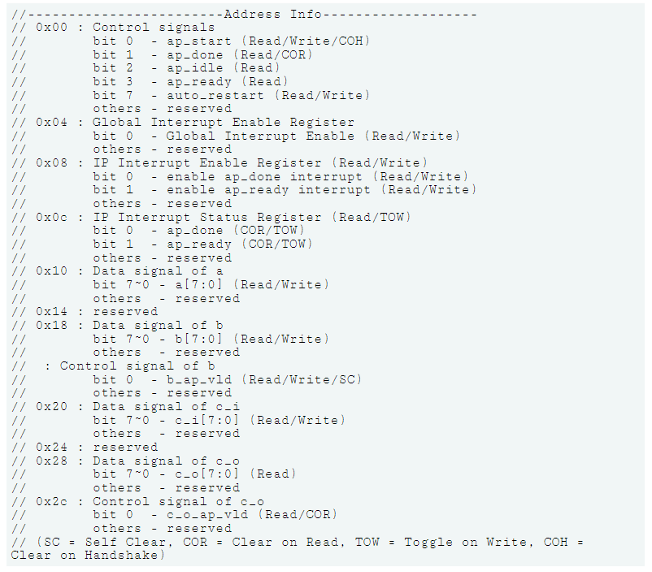

截取以下網址-page 274 S_AXILITE Control Register Map作參考:

(https://www.xilinx.com/support/documentation/sw_manuals/xilinx2021_2/ug1399-vitis-hls.pdf )

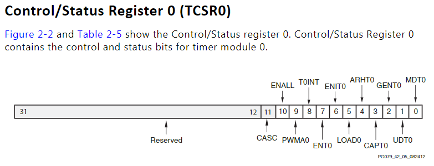

這些寄存器設置都是工具自動生成的,用戶不需要進行修改。具體這些信號是如何讓控制這些模塊的,以后有機會可以再講。那么如果有些需求是,我是一名RTL設計者,設計里面有Xilinx IP需要配置功能,我想用更多一點的寄存器空間作額外配置,現有的寄存器空間不夠,不能滿足我的要求:假設,一個IP中內嵌了一個axi_timer IP(截圖取自:https://www.xilinx.com/support/documentation/ip_documentation/axi_timer/v2_0/pg079-axi-timer.pdf page 12)

那么我該如何配置它呢?

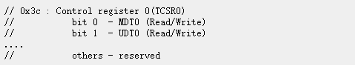

這時,之前提到xrt_ip就可以派上用場了,用戶可以自己定制控制寄存器而不用受限于規定的control register map,當然端口類型還是需要按照kernel的要求來設計。沿用上述的寄存器配置,我們可以額外地添加寄存器:

所以我們可以看到,kernel應該算IP中的一個子集,只是IP的話更加的靈活些。但是由于IP控制寄存器配置的不固定,導致xrt無法自動管理IP(不知道哪個寄存器代表的含義),所以只能提供了寄存器接口讓用戶自己訪問控制。從這方面來說,使用的便利性會降低,無論是IP的啟動停止,還是寄存器配置都需要用戶來控制。相對來說,xrt_kernel匹配的set_arg,run,wait等操作,它能夠代替用戶做一些底層操作,更加地省時省力。

原文標題:開發者分享|XRT Native API: XRT_Kernel & XRT_IP 介紹

文章出處:【微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1645文章

22025瀏覽量

617521 -

寄存器

+關注

關注

31文章

5433瀏覽量

124188 -

IP

+關注

關注

5文章

1800瀏覽量

152383 -

API

+關注

關注

2文章

1580瀏覽量

63869 -

Kernel

+關注

關注

0文章

49瀏覽量

11659

原文標題:開發者分享|XRT Native API: XRT_Kernel & XRT_IP 介紹

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

IP6825+IP5306充電寶:重新定義便攜電源的無線充電體驗

博世GTM IP模塊架構介紹

android如何獲取本機ip地址及ip歸屬地

理解彈性IP與浮動IP

XRT_Kernel與XRT_IP介紹

XRT_Kernel與XRT_IP介紹

評論