如今,供應(yīng)鏈安全是一個熱門話題。芯片供應(yīng)商特別關(guān)注,因為他們提供最容易受到信息提取和操縱的組件。同時,原始設(shè)備制造商 (OEM) 對了解其芯片供應(yīng)商供應(yīng)鏈中的風(fēng)險以及這些風(fēng)險如何影響其最終產(chǎn)品具有既得利益。因此,雖然產(chǎn)品開發(fā)的雙方都存在安全威脅,但特定于 OEM 生命周期階段的風(fēng)險也是一個問題。

這個由兩部分組成的系列將著眼于芯片供應(yīng)商和 OEM 之間的相互關(guān)系,以及他們必須如何合作以保護(hù)所有制造階段的漏洞。第一篇文章確定了 IC 生產(chǎn)生命周期每個步驟中的威脅,并描述了如何緩解這些威脅。第二篇文章側(cè)重于 OEM 特定的安全風(fēng)險,并描述了最終產(chǎn)品制造商和芯片供應(yīng)商如何承擔(dān)責(zé)任。這些文章將表明 OEM 和芯片供應(yīng)商可以通過在其每個生產(chǎn)階段承擔(dān)風(fēng)險來防止大部分安全攻擊。

IC 生命周期每個階段的安全威脅

無論是由于代工廠的故意行為還是不良行為者的滲透,IC 生命周期的每個階段都存在多種威脅,可能使最終產(chǎn)品面臨風(fēng)險。

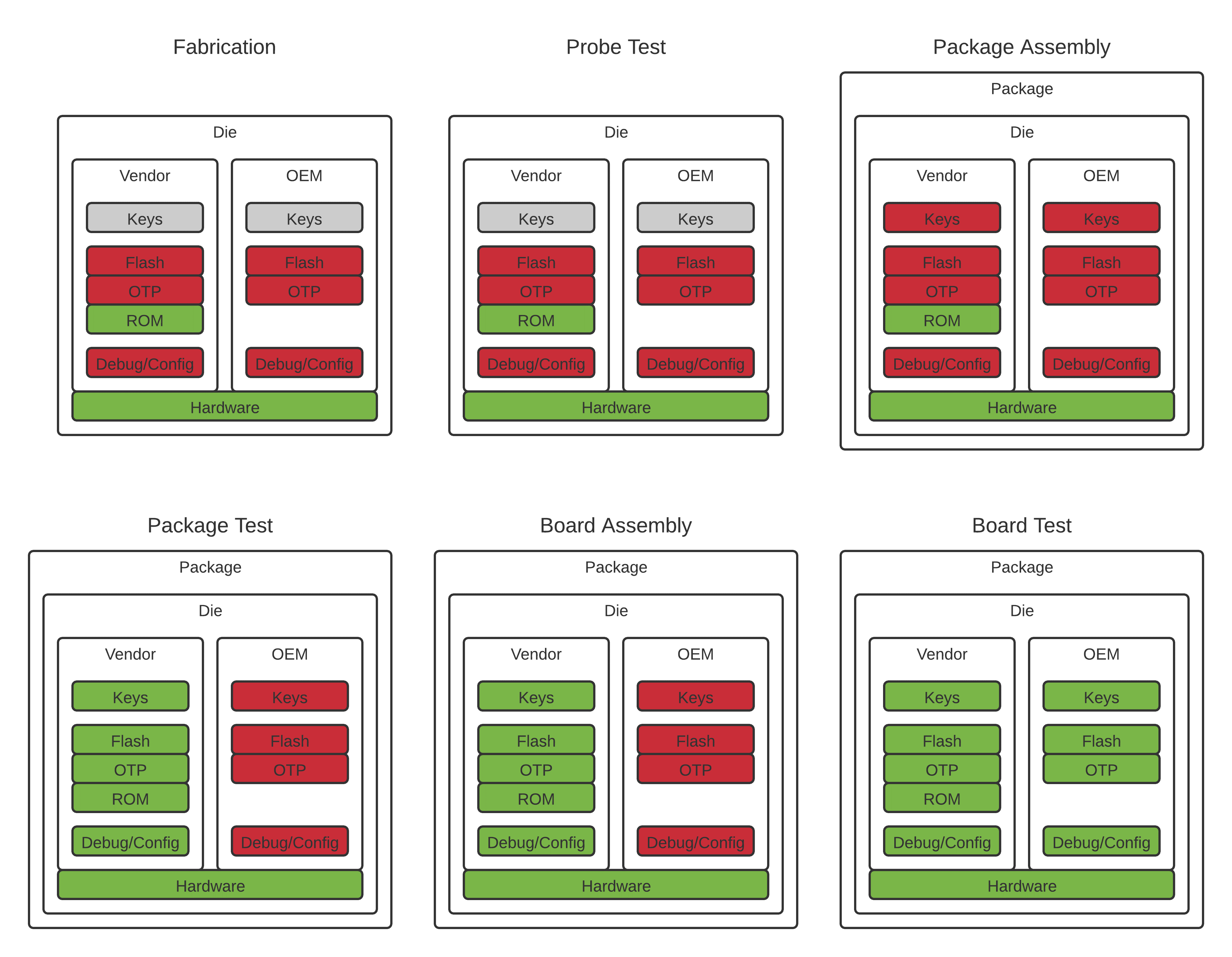

制造生命周期包括以下步驟,如圖 1 所示。

制造

探針測試

封裝組裝

電路板組裝(OEM 擁有和控制)

電路板測試(OEM 擁有和控制)

圖 1 上述概要顯示了 IC 生命周期開發(fā)的六個關(guān)鍵階段。資料來源:硅實驗室

IC 開發(fā)從制造階段開始,在該階段設(shè)備在代工廠中進(jìn)行物理制造。此時 IC 的 ROM 已編程,但所有其他存儲器(OTP、閃存和 RAM)均未編程。下一步是探針測試,其中 IC 在從硅片上切下之前先進(jìn)行功能測試。在這個階段,沒有安裝永久配置,并且在制造過程中插入的任何數(shù)據(jù)都將作為測試過程的一部分被刪除。

在封裝組裝階段,將單個裸片放入封裝中。這一步是一個完全機械的過程,不進(jìn)行編程或測試。一旦進(jìn)入封裝,IC 就會進(jìn)行封裝測試,通常被硅供應(yīng)商稱為“最終測試”,因為這是他們運行的最終測試。

該測試有多種用途:尋找組裝過程中的缺陷,檢查設(shè)備是否存在參數(shù)問題,例如功耗過大或特性不合格。此外,它使用任何硅供應(yīng)商提供的數(shù)據(jù)初始化設(shè)備。然后將設(shè)備出售給執(zhí)行電路板組裝的 OEM,然后將設(shè)備安裝到系統(tǒng)中。接下來,在電路板測試中,IC 接受最終測試、配置和編程。

通過對 IC 生命周期步驟的基本了解,我們現(xiàn)在可以深入了解每個步驟中存在的威脅。在討論這些步驟時,我們將使用 Silicon Labs 的制造生命周期作為 IC 開發(fā)模型。其他半導(dǎo)體供應(yīng)商將大體相似,因此本概述應(yīng)適用于大多數(shù)供應(yīng)商。

制造

針對此步驟的攻擊極不可能發(fā)生,因為它們成本高昂,并且需要生成至少一個新的掩碼集、對設(shè)備的深入分析以及高度的專業(yè)知識。此外,這一步的任何攻擊都不能輕易針對特定的最終產(chǎn)品。由于代工廠生產(chǎn)多個晶圓,每個晶圓上都有數(shù)千個設(shè)備,攻擊者無法知道哪些設(shè)備最終會用于哪些最終產(chǎn)品。此外,在此開發(fā)階段對設(shè)計進(jìn)行的任何修改都會影響該制造設(shè)備的每個副本,從而使其更容易檢測。但是,此階段的漏洞確實會帶來安全風(fēng)險,如以下小節(jié)所述。

數(shù)據(jù)提取

代工廠的一種可能的攻擊向量是訪問使最終產(chǎn)品面臨風(fēng)險的機密信息。例如,如果 IC 在 ROM 中具有對稱或私鑰——或硬編碼到寄存器等其他硬件中——代工廠可以輕松提取該值。同樣重要的是要記住,任何可以從設(shè)計中輕松提取的數(shù)據(jù)也可以通過逆向工程從設(shè)備的物理副本中獲得。例如,一些實驗室將以不到 1 萬美元的價格對 ROM 數(shù)據(jù)進(jìn)行反處理和提取,這可能比從代工廠獲取布局更具成本效益。為避免此問題,精心設(shè)計的產(chǎn)品絕不應(yīng)包含機密信息。

邏輯變化

一個更合理的威脅是鑄造廠修改設(shè)備以引入可利用的缺陷。這種修改可能包括修改 ROM 的內(nèi)容或邏輯以改變設(shè)備的行為或引入額外的功能。雖然這些類型的更改既困難又昂貴,但基本操作完全在攻擊者的能力范圍內(nèi),可以破壞代工廠。

針對這種攻擊的一個很好的對策是進(jìn)行抽樣測試,以驗證生產(chǎn)線下隨機設(shè)備的功能。例如,Silicon Labs 每年可以隨機抽取幾個樣本,并運行測試來驗證 ROM 的內(nèi)容、驗證邏輯以及測試其他功能。如果代工廠進(jìn)行更改,這些測試將失敗。雖然可能會引入此測試無法捕捉到的邏輯更改,但此類更改的效果將受到嚴(yán)重限制,可能會達(dá)到無用的地步。在受信任的站點(例如,公司總部)執(zhí)行樣品測試可以極大地降低代工廠對硬件進(jìn)行更改并成功破壞旨在檢測它的測試的風(fēng)險。

篡改檢測的未來改進(jìn),例如基于機器學(xué)習(xí)的圖像分析,可能會進(jìn)一步防止未經(jīng)授權(quán)的芯片修改,但這些選項今天不可用。

設(shè)備復(fù)制

在這種類型的攻擊中,代工廠生產(chǎn)過多的設(shè)備,然后作為合法設(shè)備出售。例如,攻擊者可以用修改過的 ROM 過量生產(chǎn)部件,并將它們作為合法的 OEM 出售,繞過旨在捕獲此類更改的測試。這種方法允許攻擊者直接針對 OEM,因為這些設(shè)備不再流經(jīng)供應(yīng)商的供應(yīng)鏈。

防止過度生產(chǎn)的最佳方法是在包測試時提供加密憑證。然后,OEM 可以檢查這些憑據(jù),以確保他們從該供應(yīng)商處收到了正品設(shè)備。盡管代工廠可以生產(chǎn)物理上相同的設(shè)備,但他們無法為其生成有效憑證,并且 OEM 會檢測到任何假貨。

這種緩解需要標(biāo)準(zhǔn)的未鎖定設(shè)備來安全地保存密鑰。Silicon Labs 提供具有此功能的 Vault-High EFR 產(chǎn)品。使用安全級別較低的設(shè)備(例如 Vault-Mid 設(shè)備而不是 Vault-High 設(shè)備)的 OEM 可以通過使用像 Silicon Labs 的定制部件這樣的定制編程服務(wù)來實現(xiàn)類似的效果(盡管保護(hù)級別較低)制造服務(wù)(CPMS)。在這種情況下,對設(shè)備內(nèi)容的訪問在發(fā)貨之前被鎖定,以便密鑰可以保密地存儲在非易失性存儲器 (NVM) 中。

設(shè)備分析

器件分析是代工廠中最現(xiàn)實的威脅。設(shè)備在不安全的解鎖狀態(tài)下制造,提供對成品中不可用的邏輯和系統(tǒng)的訪問。雖然訪問空白的開放部件不會構(gòu)成直接的安全威脅,但攻擊者可以利用這個機會分析設(shè)備并尋找可以在配置和鎖定部件上利用的弱點。

雖然這種威脅存在于制造過程中,但它更有可能發(fā)生在組裝步驟中,下面將進(jìn)行更詳細(xì)的討論。

探針測試

An exploit targeting probe test costs less than that of making modifications in the foundry as it only requires the test program or tester to be compromised. However, as with attacks targeting fabrication, probe test attacks are systemic and can’t easily target a specific end-product or OEM.

Malicious code injection

An attacker may attempt to inject malicious code onto the device during probe test. However, any content injected at this step will either be erased at package test or cause the package test to fail when the vendor can’t program the correct content. In addition, secure boot will prevent any attempt to install unauthorized code once enabled in package test. This threat is not realistic for well-implemented products and production lifecycles.

Device analysis

理論上,在探測測試中控制測試儀的攻擊者可以執(zhí)行設(shè)備分析,類似于通過代工廠的過度生產(chǎn)可以實現(xiàn)的分析。但是,攻擊者更有可能在組裝步驟中嘗試獲得此訪問權(quán)限。

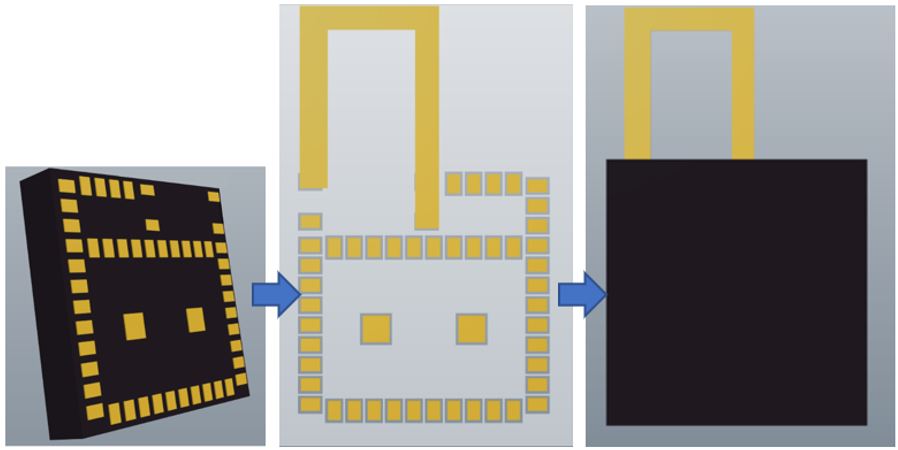

封裝組裝

由于這是供應(yīng)商將設(shè)備放入最終外形尺寸的步驟,因此封裝組裝是攻擊者最有可能竊取空白、打開的設(shè)備以進(jìn)行復(fù)制和分析的地方。

點擊查看完整大小的圖片

圖 2 芯片制造商必須確保降低與開放樣品相關(guān)的風(fēng)險。資料來源:硅實驗室

盜竊

竊取空白設(shè)備的目的是獲取開放樣本,以對攻擊者有利的方式對其進(jìn)行配置,然后將它們作為合法設(shè)備交付給目標(biāo) OEM。此策略允許針對特定的 OEM 或產(chǎn)品并繞過供應(yīng)商的最終測試,否則會覆蓋或檢測修改。

與沒有輸入數(shù)量的制造步驟不同,組裝現(xiàn)場接收并生產(chǎn)已知數(shù)量的 IC,因此通過比較這些數(shù)字應(yīng)該很容易發(fā)現(xiàn)任何重大盜竊行為。

而且,與制造一樣,我們可以通過在封裝測試中對加密憑證進(jìn)行編程來防止被盜的開放設(shè)備被假冒為正品。例如,為此目的,所有 EFR Vault-High 產(chǎn)品都配備了加密憑證,并且提供了 CPMS 以在沒有 Vault-High 功能集的設(shè)備上配置憑證。

設(shè)備分析

此階段設(shè)備分析的最明顯示例是攻擊者在安全引擎 (SE) 被編程和鎖定之前竊取設(shè)備,并使用該訪問權(quán)限來了解郵箱機制和 SE 硬件的功能。從理論上講,這種訪問可以讓攻擊者識別出一個弱點,然后可以將其轉(zhuǎn)化為針對鎖定 SE 的漏洞利用。

器件分析只需要從組裝現(xiàn)場獲取少量器件。雖然限制對開放樣本的訪問是理想的防御層,但應(yīng)該假設(shè)攻擊者將在某個時候獲得對開放樣本的訪問權(quán)限。IC 的設(shè)計方式不應(yīng)造成不可接受的風(fēng)險或破壞系統(tǒng)的安全性。

Silicon Labs 采取了幾個步驟來降低與開放樣品相關(guān)的風(fēng)險,包括審核組裝承包商的流程和程序,跟蹤內(nèi)部用于開發(fā)的任何開放設(shè)備,以及在不再需要時銷毀開放樣品。此外,產(chǎn)品旨在保持安全,即使是針對具有開放樣本和完全訪問設(shè)計的攻擊者。最后,內(nèi)部和第三方滲透測試均由具有開放樣本、全面設(shè)計知識和高度專業(yè)知識的個人執(zhí)行。

硬件改造

今天,使用更改或附加組件修改包裝所帶來的風(fēng)險相當(dāng)小。這不是一個高風(fēng)險的攻擊媒介有幾個原因。首先,組裝距離終端系統(tǒng)足夠遠(yuǎn),因此很難針對特定的終端設(shè)備(如門鎖)。此外,空間限制使得隱藏 IC 的任何添加變得困難。最后,抽樣測試可以通過對幾個單元進(jìn)行 X 射線檢測以識別意外組件來檢測任何大規(guī)模攻擊。

封裝測試

有許多通用方法可以使包測試階段的漏洞利用變得更加困難,包括限制對測試站點的訪問和維護(hù)日志記錄控制。首先,應(yīng)遵守網(wǎng)絡(luò)和 PC 的正常安全做法。例如,測試系統(tǒng)不應(yīng)直接連接到 Internet,也不應(yīng)使用可通信的登錄憑據(jù)。供應(yīng)商應(yīng)對這些流程和系統(tǒng)進(jìn)行定期審查,以確保它們不被更改或利用。這些簡單的操作會使攻擊者更難獲得對測試系統(tǒng)的訪問權(quán)限。

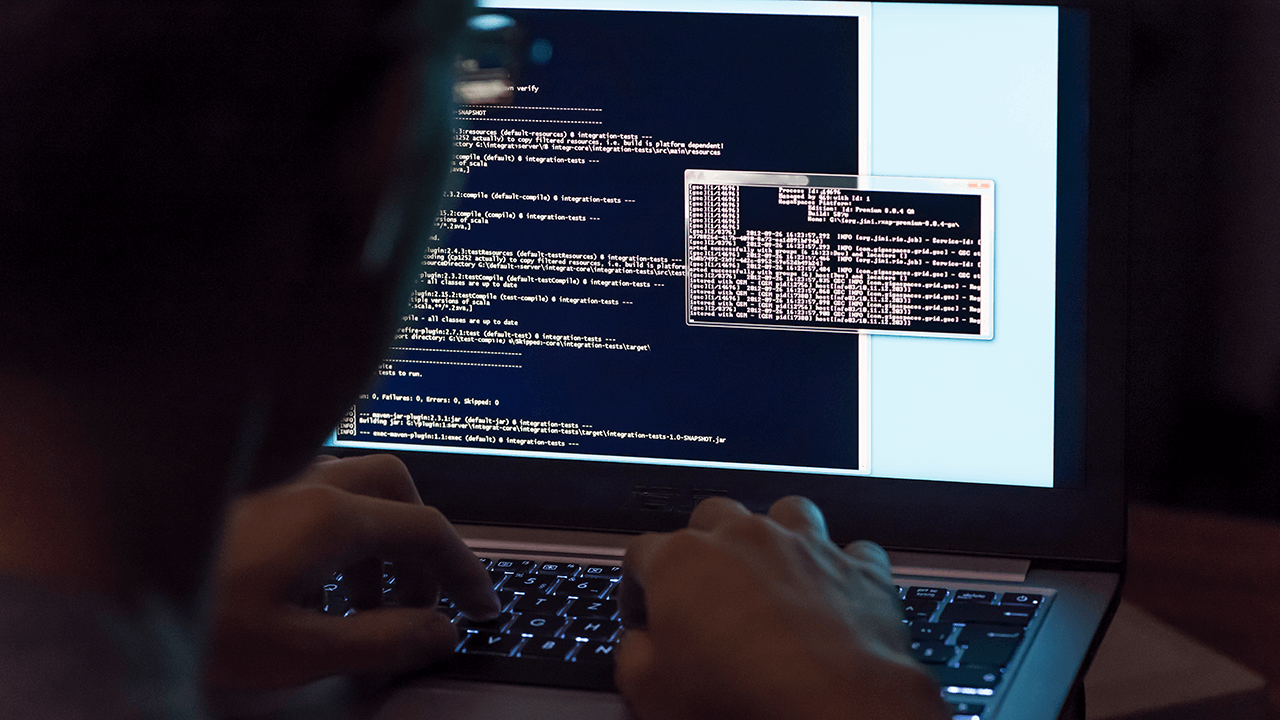

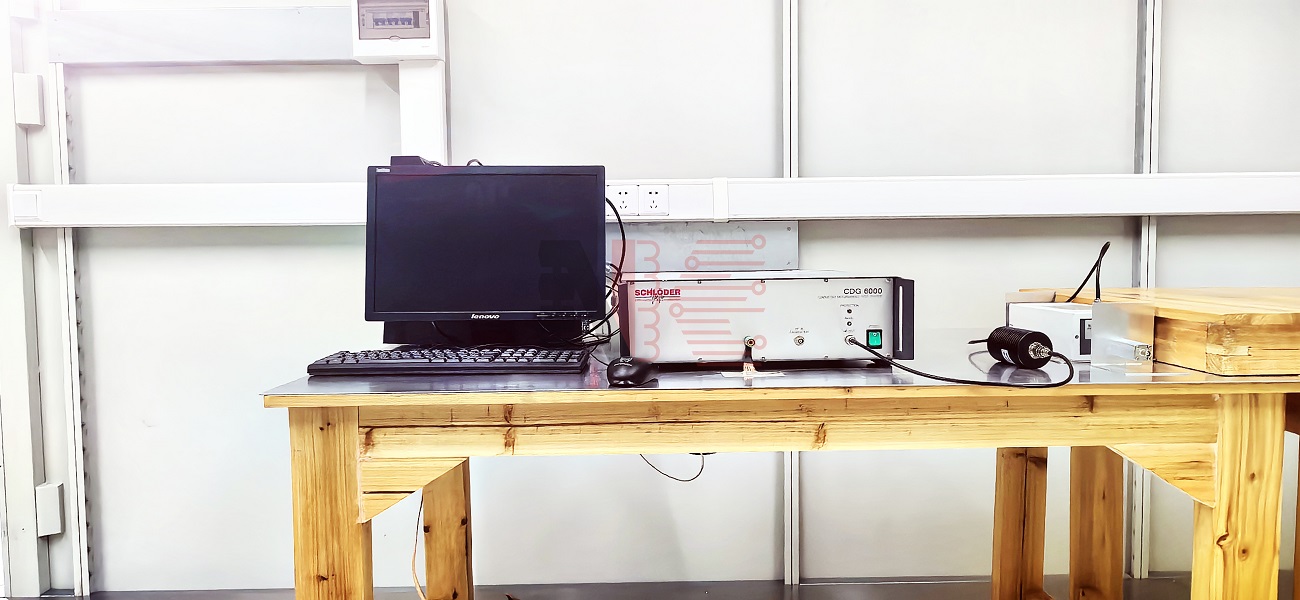

圖 3 在封裝測試站點,擁有不受其他供應(yīng)商影響的受信任機器至關(guān)重要。資料來源:硅實驗室

Silicon Labs 部署了多種技術(shù)來在其測試站點提供增強的安全性。例如,該公司委托不與其他供應(yīng)商共享的安全強化測試人員。此外,Silicon Labs 為測試站點提供了一臺受信任的機器,該機器不受其影響,可用于監(jiān)控和支持測試人員。這臺機器位于服務(wù)器機房中,沒有本地接口,并且包含旨在抵御物理攻擊的硬件。

惡意代碼注入

在這個階段最明顯的攻擊方法是注入惡意代碼來編輯設(shè)備的行為。芯片廠商在此步驟提供的代碼,例如 SE 固件,不會被板測試覆蓋;但是,如果可以更改,則可以運送受損設(shè)備。

這種風(fēng)險可以通過在 ROM 中使用帶有公鑰的安全引導(dǎo)來消除,從而確保只有正確簽名的代碼才能運行。如果攻擊者試圖修改程序代碼,它將不再被正確簽名,并且設(shè)備將停止運行。由于用于簽名的密鑰存儲在硬件安全模塊 (HSM) 中,受到嚴(yán)格控制,并且在任何生產(chǎn)環(huán)境中都不可用,因此攻擊者極不可能為被操縱的圖像生成正確的簽名。

由于測試要求,固件編程后啟用安全啟動。盡管復(fù)雜,但這種生產(chǎn)流程使攻擊者有可能破壞包測試,從而對惡意映像進(jìn)行編程并禁用安全啟動。

為了完全消除這種威脅,IC 應(yīng)允許 OEM 驗證設(shè)備的狀態(tài),而不受任何編程代碼的影響。例如,Silicon Labs 設(shè)備有一個硬件寄存器,用于指示 SE 子系統(tǒng)是否已鎖定,并允許 OEM 應(yīng)用程序或測試程序驗證設(shè)備配置是否正確。通過此驗證,OEM 可以檢測到任何封裝測試更改或惡意代碼,并丟棄這些更改的部分。

提取機密信息

如果在包測試期間對任何機密信息進(jìn)行了編程,攻擊者可能會通過破壞測試系統(tǒng)來尋求訪問權(quán)限。對于標(biāo)準(zhǔn)嵌入式產(chǎn)品,與憑證關(guān)聯(lián)的密鑰是唯一存在的機密信息。對于在機上生成這些密鑰的設(shè)備,將無法提取;但是,如果測試系統(tǒng)注入密鑰,那么攻擊者可以獲得所需的訪問權(quán)限,以便在編程時查看這些值。

使用機密的、OEM 特定信息定制的設(shè)備特別容易受到此類攻擊的威脅。但是,遵循本系列文章中建議的芯片供應(yīng)商可以提供達(dá)到或超過大多數(shù)電路板測試設(shè)施的安全級別。始終建議 OEM 與芯片供應(yīng)商合作,以確定設(shè)備編程的最佳解決方案。

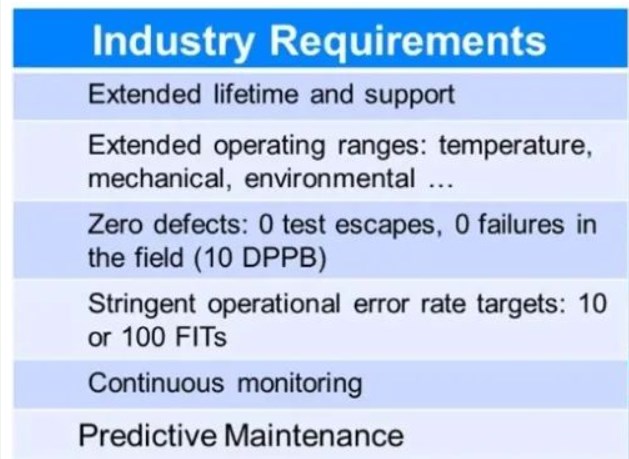

供應(yīng)鏈安全需要分層方法

安全性是一個系統(tǒng)級問題,需要供應(yīng)商和 OEM 在開發(fā)互聯(lián)產(chǎn)品時作為值得信賴的合作伙伴共同努力。隨著我們在構(gòu)建物聯(lián)網(wǎng) (IoT) 方面取得進(jìn)展,對于 OEM 來說,評估其芯片供應(yīng)商在其制造生命周期中處理安全性的成功程度至關(guān)重要。在決定使用哪些供應(yīng)商時,OEM 應(yīng)考慮供應(yīng)商提供的透明度和徹底性水平,以及其 IC 的成本和性能。

立即與您的供應(yīng)商討論他們的制造安全性以及他們?nèi)绾螏椭_保您的最終產(chǎn)品的安全性。

本系列文章的第二部分將解釋 IC 制造生命周期的最后兩個階段,這與 OEM 特定的安全風(fēng)險有關(guān)。

— Joshua Norem是 Silicon Labs的高級 系統(tǒng) 工程師 。

審核編輯 黃昊宇

-

OEM

+關(guān)注

關(guān)注

4文章

408瀏覽量

51506 -

IC制造

+關(guān)注

關(guān)注

2文章

32瀏覽量

16471 -

安全知識

+關(guān)注

關(guān)注

0文章

14瀏覽量

8918

發(fā)布評論請先 登錄

關(guān)于生命周期中的aboutToAppear和onPageShow的理解和應(yīng)用

如何在MCXN947微控制器上配置安全啟動和生命周期

ServiceAbility的生命周期介紹

UIAbility組件生命周期介紹

KaihongOS操作系統(tǒng):頁面的生命周期介紹

KaihongOS操作系統(tǒng):UIAbility的生命周期

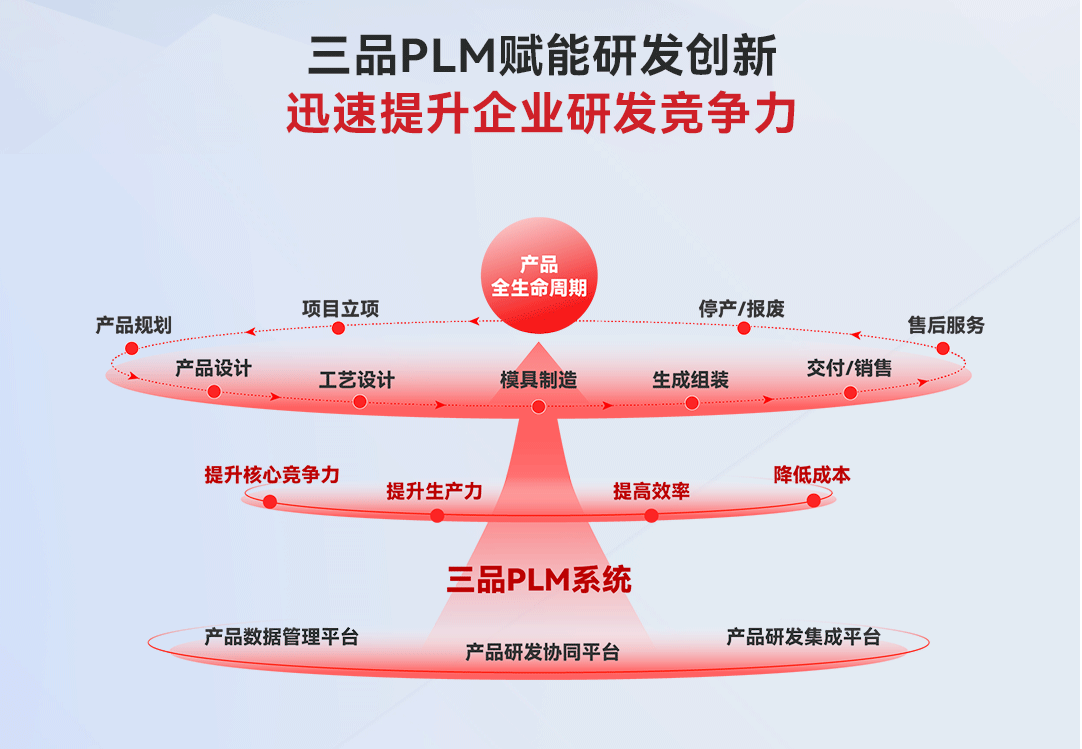

一文讀懂產(chǎn)品生命周期管理系統(tǒng)(PLM)?

醫(yī)療設(shè)備全生命周期管理,守護(hù)健康生命線

PLM產(chǎn)品生命周期管理系統(tǒng)需要采集哪些數(shù)據(jù)

設(shè)備全生命周期管理系統(tǒng),一站式管控設(shè)備 “一生”

PLM解決方案,產(chǎn)品生命周期管理軟件

什么是PLM產(chǎn)品生命周期管理系統(tǒng)?

PLM助力企業(yè)實現(xiàn)產(chǎn)品全生命周期管理與智能化升級

如何確保車規(guī)級芯片全生命周期的安全

IC 制造生命周期中的安全基礎(chǔ)知識

IC 制造生命周期中的安全基礎(chǔ)知識

評論