大概率您會(huì)這么想:

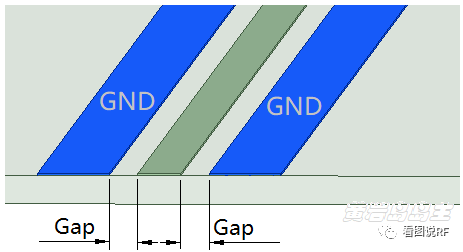

單面PCB,沒(méi)有地平面,采用雙側(cè)都有地線的共面波導(dǎo)結(jié)構(gòu),就能實(shí)現(xiàn)布線阻抗控制:

想得美,理論豐滿,現(xiàn)實(shí)骨感。

能想到用單面PCB實(shí)現(xiàn)布線阻抗控制的老板,一定在物料成本上考慮到了極致:

與常規(guī)雙面PCB相比,單面PCB少了過(guò)孔金屬化、背面銅蝕刻、背面絲印、背面綠油等工序,減少了PCB制造成本;

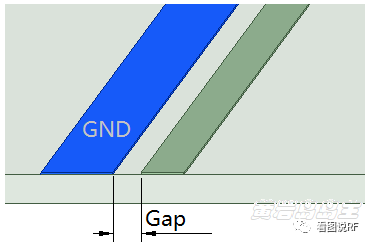

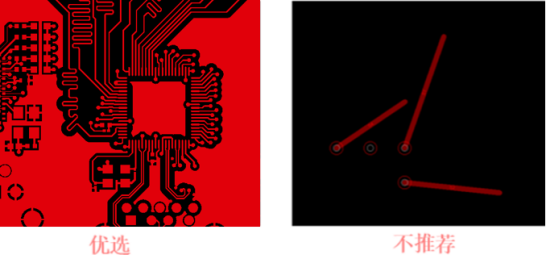

單面布線面積也一定會(huì)盡量減小,兩側(cè)鋪地增加了布線面積、增加了布通難度,所以只能單側(cè)鋪地(跟隨地線)。

那么,單側(cè)鋪地的阻抗由鋪地間隙Gap大小決定?

那又單純了,典型的沒(méi)經(jīng)過(guò)社會(huì)拷打。

能想到單面布線阻抗控制的老板,一定會(huì)找個(gè)極低成本的三線PCB廠家加工,別指望線寬(等同于線間隙Gap)加工精度了。這種三線PCB廠家只保證基本的通斷。

單側(cè)鋪地的Gap與阻抗關(guān)系

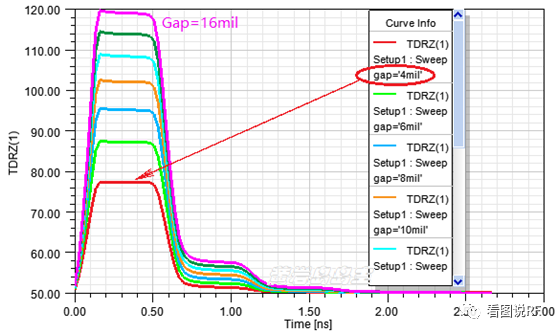

為了讓大家死心,特意用HFSS建模,F(xiàn)R4介質(zhì)厚度20mil,銅厚1.4mil,線寬30mil。看一眼單側(cè)鋪地的Gap與阻抗關(guān)系:

看一眼單側(cè)鋪地的Gap與阻抗關(guān)系:

30mil線寬單面布線,鋪銅間隙Gap=4mil(主流PCB廠家普通制造工藝能加工的鋪銅間隙),阻抗也只能做到77歐,與50歐相差太遠(yuǎn)。

鋪銅間隙Gap=4mil大概是主流PCB廠家能保證通斷能力的鋪銅間隙,實(shí)際加工出來(lái)的Gap可能3~5mil范圍,有+/-1mil誤差是很正常的,會(huì)導(dǎo)致阻抗控制誤差超過(guò)20%。

即使如此,別指望低成本的三流PCB廠家也能加工出4mil鋪銅間隙。

上圖的紫色線,對(duì)應(yīng)鋪銅間隙Gap=16mil。

解決方案

根據(jù)公式Z0 = sqrt(L0/C0),增加單位長(zhǎng)度的電容量,就能降低阻抗到50歐。

單位長(zhǎng)度,是指遠(yuǎn)小于導(dǎo)波波長(zhǎng)的長(zhǎng)度。

單位長(zhǎng)度的電容量,用均勻排列的貼片電容實(shí)現(xiàn)。

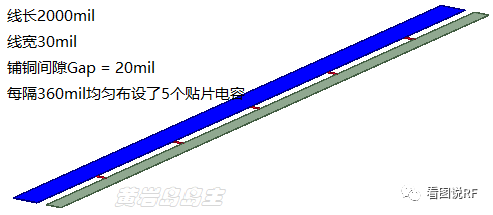

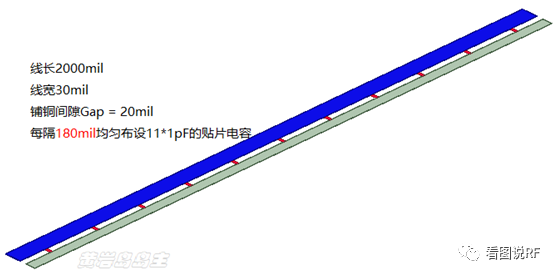

下圖模型:

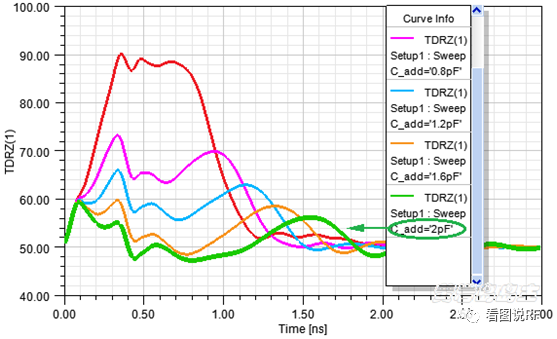

仿真出來(lái)的阻抗如下:

紅線0.4pF,TDR曲線顯示的阻抗88歐;

綠線2pF,TDR曲線是最接近于50歐的;

說(shuō)明這個(gè)長(zhǎng)度2000mil的布線結(jié)構(gòu),需要用貼片電容增加總共5*2 = 10pF左右的附加電容,才能將阻抗壓到50歐左右。

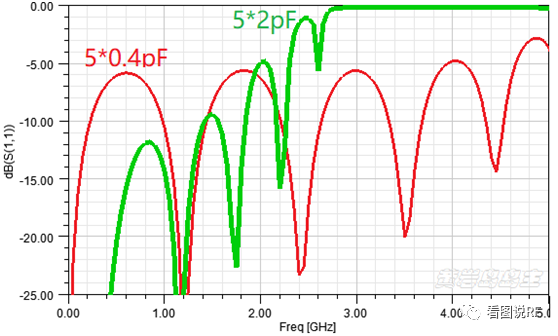

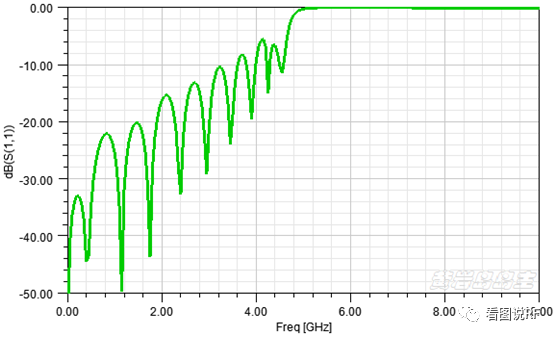

看看回波損耗:

對(duì)于數(shù)字電路,假設(shè)以回波損耗10dB為限:

5*2pF拓樸結(jié)構(gòu),大致能傳輸1Gbps信號(hào)。

5*0.4pF拓樸結(jié)構(gòu),大致能傳輸0.15Gbps信號(hào)。

還是有收獲的。

單位長(zhǎng)度減半

下圖模型:

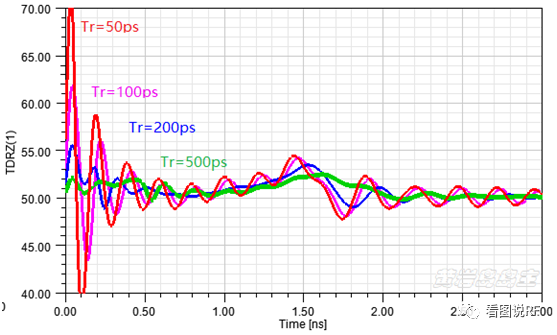

看看上圖拓樸結(jié)構(gòu)的TDR瞬時(shí)阻抗,與上升沿Tr關(guān)系:

藍(lán)線阻抗大致控制在+/-10%,對(duì)應(yīng)上升時(shí)間Tr=200ps。

綠線阻抗大致控制在+/-5%,對(duì)應(yīng)上升時(shí)間Tr=500ps。

再看看回波損耗:

按照前面假設(shè)的標(biāo)準(zhǔn),每隔180mil布局1pF電容,大致能傳輸2.2Gbps數(shù)據(jù)信號(hào)。

本文的模型,用了HFSS的LumpRLC邊界條件,這與實(shí)際的貼片元件仍然有分布參數(shù)的差異,低頻率時(shí)誤差不大。

總結(jié)

共面波導(dǎo)結(jié)構(gòu)理論上能實(shí)現(xiàn)單面PCB布線的50歐阻抗控制,但實(shí)際工程上是很難實(shí)現(xiàn)的:因?yàn)橐箐併~間隔Gap小于4mil。

可以采用大的鋪銅間隔Gap=20mil,但每隔單位長(zhǎng)度布局貼片電容的辦法實(shí)現(xiàn)50歐阻抗控制:

每隔360mil布局2pF電容,大致能傳輸1Gbps數(shù)據(jù)信號(hào)。

每隔180mil布局1pF電容,大致能傳輸2Gbps數(shù)據(jù)信號(hào)。

依此類(lèi)推。

電容間隔總不能小于封裝本體吧?因此,這種拓樸結(jié)構(gòu)只能用于低頻低速信號(hào)。

-

pcb

+關(guān)注

關(guān)注

4362文章

23458瀏覽量

408306 -

TDR

+關(guān)注

關(guān)注

1文章

71瀏覽量

20316 -

貼片電容

+關(guān)注

關(guān)注

13文章

553瀏覽量

28561

原文標(biāo)題:038_單面PCB布線阻抗的工程設(shè)計(jì)

文章出處:【微信號(hào):看圖說(shuō)RF,微信公眾號(hào):看圖說(shuō)RF】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

受控阻抗布線技術(shù)確保信號(hào)完整性

必學(xué)!PCB設(shè)計(jì)布線技巧、電機(jī)控制、電源管理設(shè)計(jì)教程等精華資料

每周推薦!PCB設(shè)計(jì)布線技巧、電機(jī)控制、電源管理芯片設(shè)計(jì)教程等精華資料

建議收藏,這31條PCB設(shè)計(jì)布線技巧

揭秘PCB阻抗控制:如何影響你的電子設(shè)備性能?

揭秘PCB阻抗在高速信號(hào)傳輸中的重要性

深度解析:雙面PCB板與單面PCB板的制造差異

104條關(guān)于PCB布局布線的小技巧

影響PCB阻抗的三大因素

技術(shù)資訊 I 如何使用 Allegro X PCB Editor 優(yōu)化RF布線和阻抗

在DSP上實(shí)現(xiàn)DDR2 PCB布局布線

如何用單面PCB實(shí)現(xiàn)布線阻抗控制

如何用單面PCB實(shí)現(xiàn)布線阻抗控制

評(píng)論