迄今為止,大多數 NEC 的微控制器封狀都有相鄰電源引腳。這引腳使 PCB 設計者能更輕易地減少微控制器與退耦電容之間的電流環路面積,當然,要最小化環路面積,每相鄰電源引腳對之間要有一個電容。不僅降低了環路面積,也減少了退耦電容的連接阻抗。

需要在PCB設計方面的工作:

盡可能地靠近供應引腳放置退耦電容,把每條線當成具有阻抗的導線考慮,尤其是去耦電路和供電系統板之間的連接應慎重考慮。

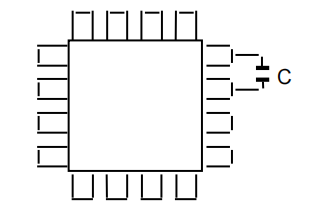

圖 4-4: 鄰近的電源引腳

以上所列出的只是少數當今可行的 EMC 措施。一般來講, 越接近噪聲源使用和在設計處理過程中考慮的越早,完成 EMC 的效果越好,如果在后期的應用試驗階段發現 EMC 問題,不僅導致矯正成本高,而且有時還延遲整體應用系統的上市時間,另外,在此階段一些重大決定已經作出,如器件選擇等,因此考慮 LSI 的 EMC 措施優先于為下個項目選擇一個新的微處理器。

審核編輯:湯梓紅

-

微控制器

+關注

關注

48文章

7933瀏覽量

154108 -

電源

+關注

關注

185文章

18329瀏覽量

255661 -

pcb

+關注

關注

4362文章

23458瀏覽量

408290

發布評論請先 登錄

10 cm 電容式接近檢測參考設計

怎么用一個單芯片實現電感鄰近度感測

TI的CapTIvate? 技術實現鄰近度和手勢感測

電源和地的設計及PCB走線說明

求教DCDC BS引腳的電容是什么作用?

一種可保護隱私的快速鄰近監測方法

芯片電源引腳的電容選擇

村田貼片電容的引腳如何檢查?

鄰近的電源和地引腳電容

鄰近的電源和地引腳電容

評論