第二屆SmartNIC&DPU技術創新峰會在北京舉行,云脈芯聯在2022 SmartNIC&DPU Awards年度評選中榮獲匠心技術獎。云脈芯聯創始人&CEO劉永鋒出席峰會并發表《融合、開放、極致—DPU的未來之路》的主題演講。

在本次演講在峰會上引起了參會者的廣泛關注。以下為演講中的主要內容。

DPU發端于網絡

探究DPU的緣起,要從了解數據中心架構的演進開始。從數據中心的發展來看,隨著規模的不斷擴大和承載業務的不同,基礎架構經歷了比較明顯的底層網絡技術的代次演進,從IT機房階段的二層網絡、IT數據中心階段的三層網絡到云原生數據中心階段的虛擬網絡。

進入到云基礎設施時代,為滿足高帶寬、大規模和低延遲的需求,數據中心基礎架構又經歷了三個階段的演進,我們稱之為計算聯網,計算云網和智算云網時代。

在最初的計算聯網階段,交換機的SDN虛擬網絡方案就可以滿足業務的需求。而到了計算云網階段則需要通過主機overlay網絡的方式在進一步擴大網絡規模的同時將虛擬網絡同物理網絡解耦,以追求更快的業務迭代和更高的穩定性。很明顯,CPU在為更多的基礎設施服務消耗越來越多的算力。在CPU算力增長遭遇瓶頸,業務數據和網絡帶寬不斷增長的情況下,網絡基礎架構需要進一步演進來實現整個數據中心維度的降本增效。

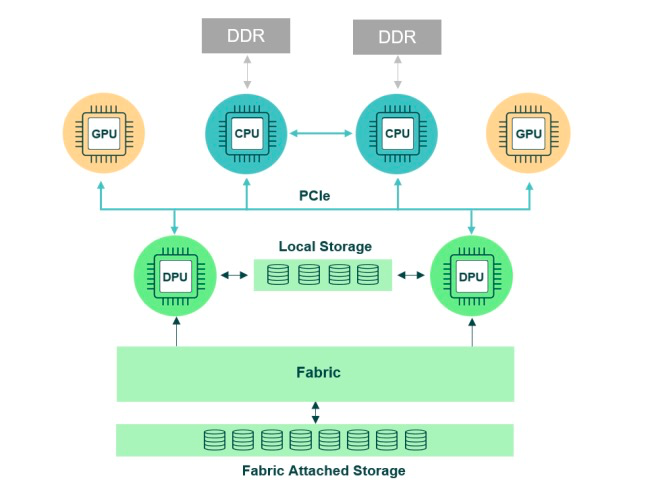

因此,DPU的出現不僅僅是為解決CPU的算力瓶頸,而是要通過先天的網絡屬性,在數據中心整體TCO的維度提升算力。我們把DPU提升數據中心算力手段總結為算力卸載、算力釋放和算力擴展三種方式。

#算力卸載

即以更高的能效比卸載CPU的部分算力,主要是網絡,存儲,安全等基礎設施服務。

#算力釋放

即無需CPU介入多次訪問內存和外設,避免不必要的數據搬運、拷貝和上下文的切換,直接在網卡硬件上對數據完成處理并交付給最終消費數據的應用。

#算力擴展

是指通過有效避免擁塞消除跨節點的網絡通信瓶頸,顯著降低分布式應用任務周期中的通信耗時占比,在大規模的集群維度提升計算集群的整體算力。

因此,DPU成為了數字基礎設施邁向“連接+計算”的關鍵一步。

融合、開放、極致——DPU未來發展愿景

第一、融合。 DPU需要一個全新的融合架構來實現進一步的軟硬件融合,能夠支持云原生的軟件定義接口,面向海量連接的資源共享架構,多種協議融合兼容的傳輸層實現。

第二,開放。 從軟硬件協同的角度,首先DPU需要一個通用的CPU架構平臺來實現管控平面的軟件無縫遷移,傳統只能滿足靈活性需求的NP則不適合用于管控平面的卸載。其次,從數據平面的卸載角度,DPU需要具備靈活的可編程能力,同時向上兼容面向應用的開放軟件接口。

第三,極致。 極致則是指DPU最終需要通過創新架構實現極致的高帶寬、低延遲,極致的高性能、低功耗和極致的大規模、高可靠。

在演講的最后,劉永鋒現場展示了云脈芯聯基于FPGA實現的DPU產品metaFusion50在RDMA場景下的測試效果,metaFusion50擁塞控制實現機制可以迅速響應網絡擁塞,通過硬件機制準確、及時降速,并確保帶寬公平分配,同時可以及時、準確全面的上報監控信息。云脈芯聯metaFusion 的RDMA功能,能夠實現多打一網絡擁塞下的擁塞控制。這種通過硬件實現端到端網絡擁塞控制的機制是RDMA高性能網絡的關鍵技術,可以滿足算存分離,GPU內存共享以及AI模型訓練等高價值場景的需求。

編輯:黃飛

-

FPGA

+關注

關注

1645文章

22015瀏覽量

616845 -

cpu

+關注

關注

68文章

11065瀏覽量

216577 -

DPU

+關注

關注

0文章

393瀏覽量

24836

原文標題:融合、開放、極致——DPU的未來之路

文章出處:【微信號:SDNLAB,微信公眾號:SDNLAB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

《數據處理器:DPU編程入門》讀書筆記

《數據處理器:DPU編程入門》DPU計算入門書籍測評

IaaS+on+DPU(IoD)+下一代高性能算力底座技術白皮書

專?數據處理器 (DPU) 技術??書

英偉達DPU的過“芯”之處

【書籍評測活動NO.23】數據處理器:DPU編程入門

很好的書籍,學以致用

什么是DPU?

《數據處理器:DPU編程入門》+初步熟悉這本書的結構和主要內容

什么是DPU 未來的DPU智能?卡硬件形態

被稱為數據中心“第三顆主力芯片”,DPU憑什么?

節能環保:NVIDIA BlueField DPU 提升數據中心效率

DPU處理器在數據中心的作用是什么?

DPU處理器在數據中心的作用是什么

探究DPU的緣起,DPU提升數據中心算力的三種方式

探究DPU的緣起,DPU提升數據中心算力的三種方式

評論