電阻式隨機(jī)存取存儲器 (ReRAM) 是開發(fā)更具可擴(kuò)展性、高容量、高性能、更可靠的存儲解決方案的競爭中下一個有前途的存儲器技術(shù)。

電阻式隨機(jī)存取存儲器 (ReRAM) 正在成為一種替代性的非易失性存儲器 (NVM) 解決方案,特別是在需要不斷提高性能和能效的云和數(shù)據(jù)中心環(huán)境中。隨著人類通過視頻流等優(yōu)質(zhì)服務(wù)以及機(jī)器通過物聯(lián)網(wǎng)(IoT)對數(shù)據(jù)的需求不斷增長,ReRAM技術(shù)表現(xiàn)出比閃存更低的讀取延遲和更快的寫入性能,同時還實(shí)現(xiàn)了64pJ / cell的程序能量,比NAND提高了20%。

在數(shù)據(jù)中心環(huán)境中,3D垂直ReRAM陣列提供高性能內(nèi)存子系統(tǒng),能夠取代傳統(tǒng)的基于DRAM或閃存的SSD,以更小的外形尺寸和更低的能源需求加快數(shù)據(jù)處理,存儲和檢索。借助 ReRAM,在提供 1 個 GIOP/U 的架構(gòu)中,可以實(shí)現(xiàn)低于 5 納秒的延遲。

典型的ReRAM電池包含夾在兩個金屬電極之間具有不同電阻特性的開關(guān)材料。ReRAM的開關(guān)效應(yīng)基于離子在電場影響下的運(yùn)動和開關(guān)材料存儲離子分布的能力。反過來,這會導(dǎo)致ReRAM器件的電阻發(fā)生可測量的變化,從而減少介電擊穿的影響,隨著時間的推移,介電擊穿會降低存儲器元件的性能。

ReRAM技術(shù)最常見的挑戰(zhàn)是溫度靈敏度,與標(biāo)準(zhǔn)CMOS技術(shù)和制造工藝的集成,以及各個ReRAM單元的選擇機(jī)制。因此,設(shè)計人員根據(jù)他們選擇的開關(guān)材料和存儲單元組織,采用許多不同的方法來實(shí)施ReRAM技術(shù)。

結(jié)合這些變量,可能會導(dǎo)致ReRAM技術(shù)的性能顯著差異。因此,在評估 ReRAM 時應(yīng)考慮的四個關(guān)鍵領(lǐng)域是:

可制造性

性能

密度

能源

讓我們仔細(xì)看看每一個。

可制造性

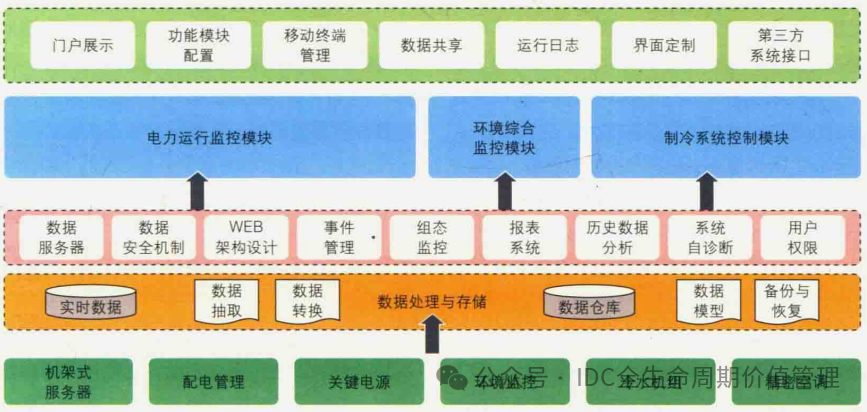

在制造ReRAM器件時,CMOS友好型材料和標(biāo)準(zhǔn)制造工藝是首選,因為它允許該技術(shù)在兩條金屬線之間輕松集成,直接連接到CMOS IP邏輯塊,并在現(xiàn)有晶圓廠中生產(chǎn),而無需專用設(shè)備或材料(圖1)。由于 ReRAM 是一種低溫、后端生產(chǎn)線 (BEOL) 工藝集成,因此可以在 CMOS 邏輯晶圓的頂部集成多層 ReRAM 陣列,以構(gòu)建 3D ReRAM 存儲芯片。這使得在單個芯片上實(shí)現(xiàn)由片上NVM、處理內(nèi)核和模擬子系統(tǒng)組成的極其集成的解決方案,從而成為優(yōu)雅且低成本的解決方案。

與閃存單元中的電子存儲相比,少數(shù)電子損耗會導(dǎo)致可靠性,保留和循環(huán)問題并導(dǎo)致降解,Crossbar的ReRAM單元操作基于非導(dǎo)電層中的金屬絲。橫桿的 ReRAM 縮放不會影響器件性能,并且有可能實(shí)現(xiàn)低于 10 nm 的縮放。

性能

在程序操作方面,當(dāng)前的 MLC/TLC NAND 或 3D NAND 閃存需要大約 600 μs 到 1 ms 的時間來編程 8 到 16 KB 的頁面,對于 4 到 8 MB 的大塊頁面,大約需要 10 ms。

在編程之前,還必須擦除 NAND 閃存。垃圾回收是NAND閃存中數(shù)據(jù)管理的附加層,當(dāng)存儲空閑時,需要它來正確釋放具有過時數(shù)據(jù)的塊。當(dāng)垃圾回收在塊之間移動數(shù)據(jù)時收到新請求時,這會產(chǎn)生問題,從而在秒內(nèi)引入長時間且不確定的延遲。因此,SSD 寫入通常包括在 SSD 控制器、NAND 閃存和 DRAM 組件之間多次寫入數(shù)據(jù),最初是在保存數(shù)據(jù)時寫入數(shù)據(jù),后來是在多個垃圾回收周期中移動有效數(shù)據(jù)時寫入數(shù)據(jù)。因此,寫入SSD閃存的數(shù)據(jù)比主機(jī)系統(tǒng)最初發(fā)出的數(shù)據(jù)要多,這種情況很常見。這種差異被稱為寫入放大(WA)。

WA是不可取的,因為這意味著更多的數(shù)據(jù)被寫入介質(zhì),增加磨損,并通過消耗本來會保留給閃存預(yù)期功能的操作的帶寬來對性能產(chǎn)生負(fù)面影響。這在較小的進(jìn)程節(jié)點(diǎn)上尤其重要,其中NAND存儲單元的最大周期減少到3,000個程序周期以下。

相反,ReRAM使用位可更改的無擦除操作,與NAND閃存相比,讀取延遲降低了100倍,寫入性能提高了1000倍,而不受構(gòu)建大塊存儲器陣列的限制。ReRAM執(zhí)行獨(dú)立原子操作的能力允許將其構(gòu)建成更小的頁面(例如,256 B頁面與NAND中的16 KB頁面),每個頁面都可以單獨(dú)重新編程。這種類型的體系結(jié)構(gòu)通過刪除通常在垃圾回收期間訪問的大部分后臺內(nèi)存來減輕存儲控制器的負(fù)擔(dān)。NAND閃存系統(tǒng)的WA分?jǐn)?shù)通常在三到四個范圍內(nèi),而ReRAM的特性使WA等于1。這有利于存儲解決方案的讀取和寫入延遲、能耗和生存期。

針對ReRAM優(yōu)化的下一代SSD控制器將能夠更快地更新更小的頁面,進(jìn)一步減少與NAND相關(guān)的后臺存儲器操作,并提供更低,更確定的讀取延遲,約為數(shù)十μs。

能源

減少后臺內(nèi)存操作的數(shù)量可以提高數(shù)據(jù)存儲解決方案的性能和整體耐用性,還可以降低存儲控制器的整體功耗、DRAM 使用率以及數(shù)據(jù)存儲組件消耗的讀寫功耗預(yù)算。

密度

高密度ReRAM面臨的一個技術(shù)挑戰(zhàn)是潛行(或泄漏)電流。使用具有1個TnR存儲單元陣列的選擇器器件可以緩解這種情況,這使得單個晶體管可以管理大量互連的存儲單元。這可實(shí)現(xiàn)高容量固態(tài)存儲。

雖然1 TnR使單個晶體管能夠以低功耗驅(qū)動2,000多個存儲單元,但它也會引發(fā)潛行路徑電流的泄漏,從而干擾ReRAM陣列的性能和可靠性。Crossbar的現(xiàn)場輔助超線性閾值器件能夠抑制低于0.1 nA的泄漏電流,并已成功在4 Mb,3D可堆疊無源集成陣列中進(jìn)行演示。它實(shí)現(xiàn)了 10^10 的最高報告選擇性,以及小于 5 mV/dec 的極銳開啟斜率、快速啟動和恢復(fù) (《50 ns)、大于 100 M 循環(huán)耐久性以及低于 300 °C 的加工溫度。

為云和數(shù)據(jù)中心提供更快、更高效的存儲

ReRAM 技術(shù)通過更快、更密集和超低延遲的解決方案實(shí)現(xiàn)下一代企業(yè)存儲,這些解決方案能夠滿足不斷增長的數(shù)據(jù)需求。隨著能源使用和壽命成為云和數(shù)據(jù)中心環(huán)境中的關(guān)鍵總擁有成本(TCO)指標(biāo),ReRAM的進(jìn)步和數(shù)量的增加將繼續(xù)推動ReRAM的價值主張。

審核編輯:郭婷

-

DRAM

+關(guān)注

關(guān)注

40文章

2345瀏覽量

185421 -

存儲器

+關(guān)注

關(guān)注

38文章

7644瀏覽量

166990 -

數(shù)據(jù)中心

+關(guān)注

關(guān)注

16文章

5194瀏覽量

73392

發(fā)布評論請先 登錄

小型數(shù)據(jù)中心晶振選型關(guān)鍵參數(shù)全解

數(shù)據(jù)中心液冷技術(shù)和風(fēng)冷技術(shù)的比較

適用于數(shù)據(jù)中心和AI時代的800G網(wǎng)絡(luò)

優(yōu)化800G數(shù)據(jù)中心:高速線纜、有源光纜和光纖跳線解決方案

數(shù)據(jù)中心機(jī)房冷水系統(tǒng)

數(shù)據(jù)中心配電系統(tǒng)精密配電柜運(yùn)行狀態(tài)監(jiān)測管理平臺 功能介紹

光通信在數(shù)據(jù)中心的應(yīng)用

面向Switchtec和數(shù)據(jù)中心應(yīng)用的預(yù)配置時鐘發(fā)生器器件編號

華為數(shù)據(jù)中心能源榮膺W.Media 2024技術(shù)領(lǐng)袖獎

如何選擇數(shù)據(jù)中心服務(wù)

當(dāng)今數(shù)據(jù)中心新技術(shù)趨勢

怎樣保障數(shù)據(jù)中心不間斷電源不斷電 提供可靠安全的供配電#數(shù)據(jù)中心

需要合理規(guī)劃數(shù)據(jù)中心不能盲目建設(shè)

評估云和數(shù)據(jù)中心應(yīng)用的ReRAM技術(shù)選擇

評估云和數(shù)據(jù)中心應(yīng)用的ReRAM技術(shù)選擇

評論