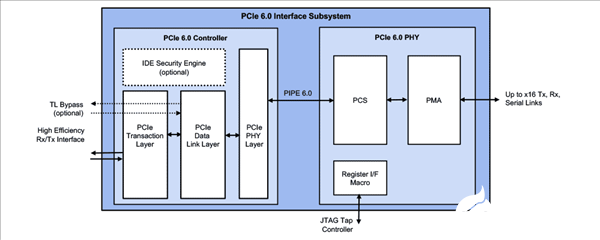

10月25日,大名鼎鼎的Rambus宣布,推出全球首個PCIe 6.0接口子系統(tǒng),主要面向高性能數(shù)據(jù)中心、AI SoC等領(lǐng)域。

Rambus的這套方案包括完整的PHY物理層、控制器IP,完整符合PCIe 6.0規(guī)范,針對異構(gòu)計算架構(gòu)全面優(yōu)化,同時也支持最新的CXL 3.0規(guī)范,可優(yōu)化內(nèi)存資源。

其中的PCIe 6.0控制器,就是Rambus今年年初發(fā)布的,也是全球第一個同類方案。

PCIe 6.0被認(rèn)為該標(biāo)準(zhǔn)誕生19年來最具革命性的一次飛躍,不僅數(shù)據(jù)傳輸率再次翻番最高可達(dá)64GT/s,x16單向帶寬128GB/s、雙向帶寬256GB/s,更是升級為1b/1b編碼的PAM4脈沖調(diào)制、提升信號完整性和信號穩(wěn)定性的ECC前向糾錯機制、提升高帶寬效率的FLIT流量控制單元、更高安全級別的IDE引擎。

當(dāng)然,它依然保持了對PCIe 5.0、PCIe 4.0、PCIe 3.1/3.0的向下兼容。

現(xiàn)階段,PCIe 5.0才剛剛開始進入市場,PCIe 6.0為時尚早,首批支持的平臺之一將是Intel下下下下代至強,代號Diamond Rapids。

-

AI

+關(guān)注

關(guān)注

88文章

34780瀏覽量

277095 -

PCIe

+關(guān)注

關(guān)注

16文章

1331瀏覽量

84902

發(fā)布評論請先 登錄

PCIe 5.0市場加速滲透,PCIe 6.0研發(fā)到來

全球首個AI設(shè)計芯片系統(tǒng)誕生,來自中科院

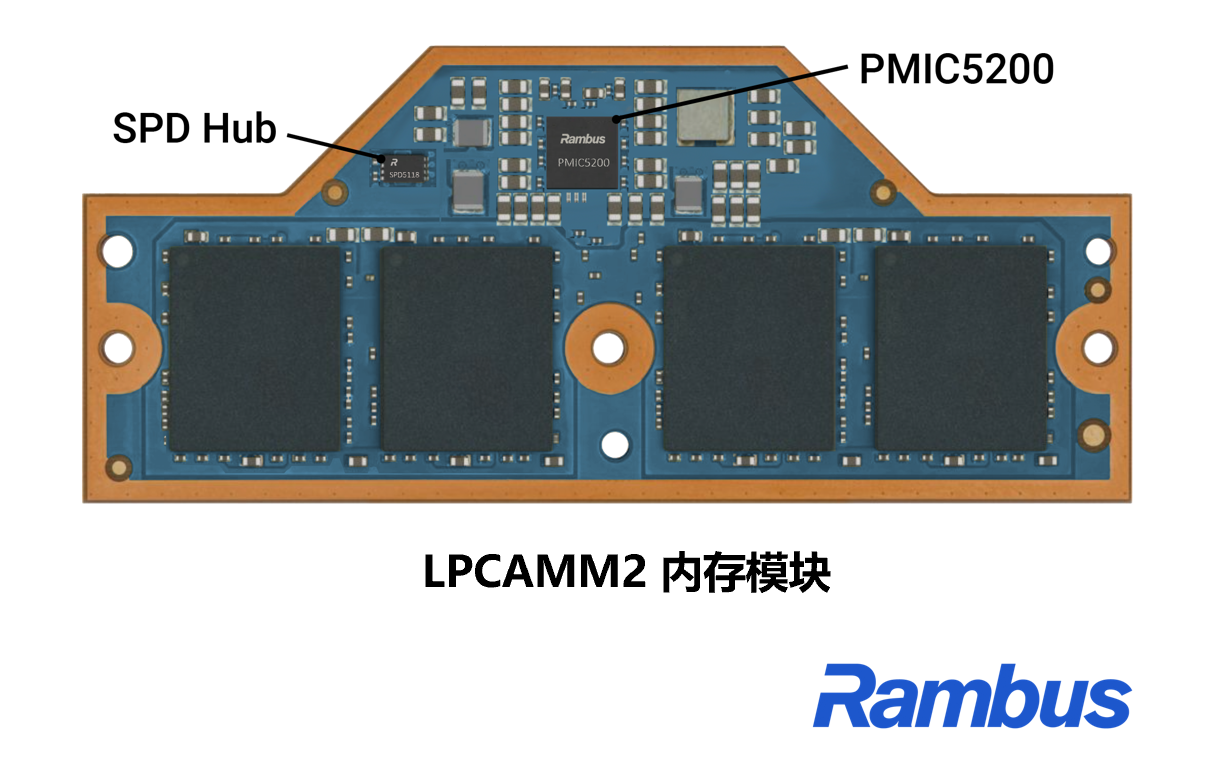

Rambus推出面向下一代AI PC內(nèi)存模塊的業(yè)界領(lǐng)先客戶端芯片組

【高清視頻案例分享】CameraLink接口的PCIe采集卡 ,基于FPGA開發(fā)平臺

核芯互聯(lián)推出面向PCIe 5.0/6.0的32/64Gbps高速重驅(qū)動器芯片CLH3264R

詳解PCIe 6.0中的FLIT模式

PCIe 6.0時代的測試挑戰(zhàn)和解決方案

Rambus推出全球首個PCIe 6.0接口子系統(tǒng) 面向大數(shù)據(jù)與AI領(lǐng)域

Rambus推出全球首個PCIe 6.0接口子系統(tǒng) 面向大數(shù)據(jù)與AI領(lǐng)域

評論