電子發(fā)燒友網(wǎng)報道(文/周凱揚)盡管制造工藝的推進速度已經(jīng)放緩,芯片設(shè)計的復(fù)雜程度依然絲毫不減,對于芯片設(shè)計者來說,在這樣一個AI驅(qū)動的時代下,如果不能將AI為自己所用,無疑會讓自己乃至整個設(shè)計項目的效率停滯不前。雖說大家都已經(jīng)察覺到AI開始滲透進EDA工具中,那么現(xiàn)階段的AI,究竟能解決哪些設(shè)計上的挑戰(zhàn)呢?

驗證

驗證是芯片設(shè)計中最大的挑戰(zhàn)之一,我們已經(jīng)見識過了價格高昂的專用驗證硬件,以及驗證上云的潮流,這些都足以說明驗證是芯片設(shè)計中一個多么耗費資源的過程,這里指代的也不僅僅是硬件計算資源,還有時間資源。驗證所耗時間甚至可能高過其他流程,這些年諸多芯片開發(fā)團隊中的驗證工程師人數(shù)也在逐漸增長,增速甚至已經(jīng)超過了設(shè)計工程師,然而業(yè)內(nèi)卻很少有人去優(yōu)化驗證這個流程。

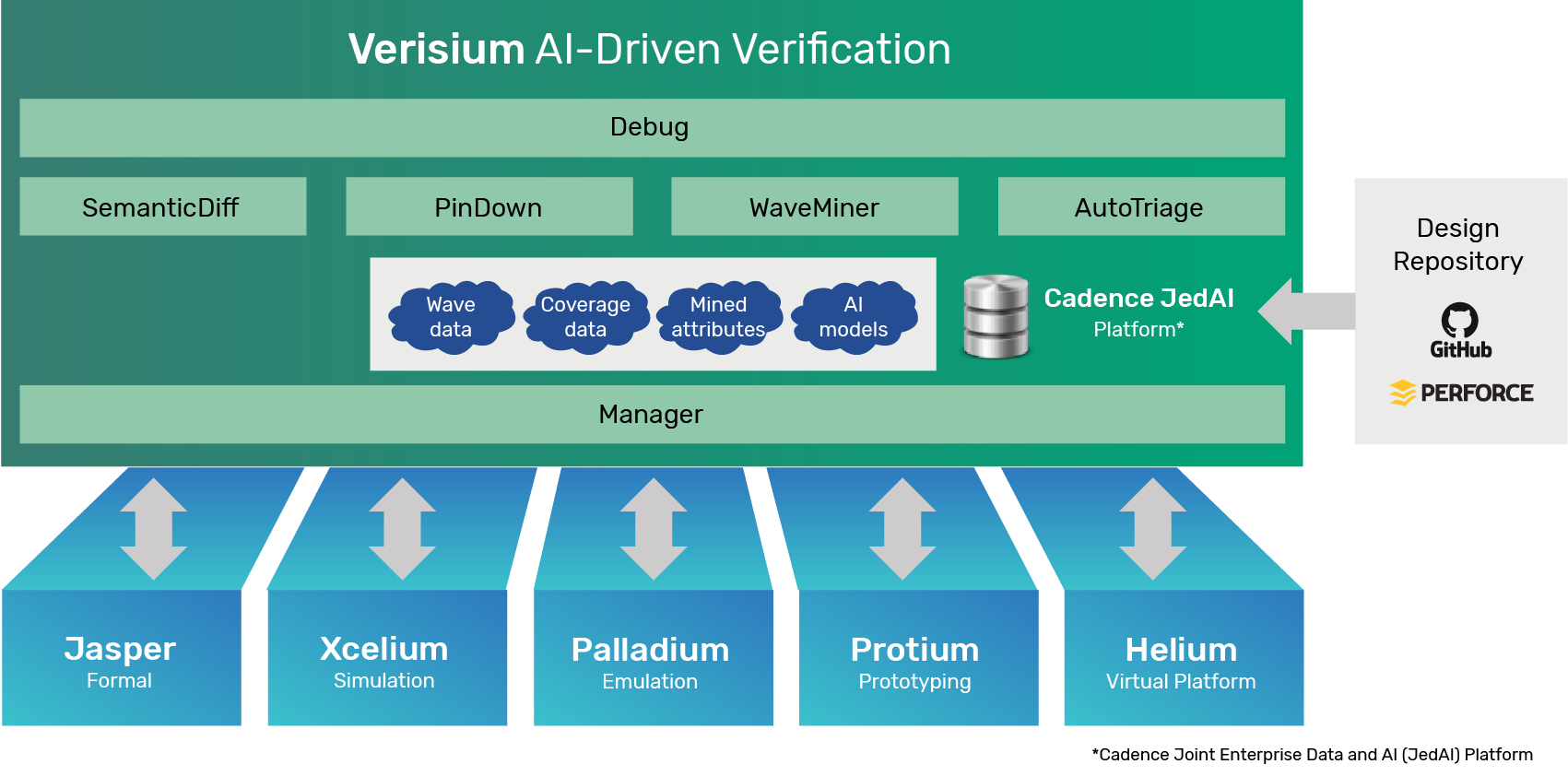

AI的出現(xiàn)終于讓這個缺口出現(xiàn)了松動,不少廠商都開始利用AI去優(yōu)化驗證這一流程,比如通過覆蓋率預(yù)測和激勵優(yōu)化來加速覆蓋率達標。Cadence也在今年發(fā)布了Verisium AI驅(qū)動驗證平臺,根據(jù)Cadence的說法,Verisium 的出現(xiàn)意味著SoC驗證從單運行單引擎算法,轉(zhuǎn)向了由AI和大數(shù)據(jù)輔助的多運行多引擎算法,從而減少了調(diào)試周轉(zhuǎn)時間、提高了調(diào)試效率,還會自動對失敗測試案例分類,減少人為分析的工作量。

模擬設(shè)計自動化

相對數(shù)字IC設(shè)計來說,模擬IC的設(shè)計顯然在自動化程度上還是差了不少的。在數(shù)字電路的設(shè)計過程中,整個流程的自由度是在逐級降低的。模擬電路設(shè)計雖然也是如此,但其下降幅度還是不比數(shù)字電路設(shè)計的,尤其是在布局布線和驗證上,所以自動化一直沒有提上日程,現(xiàn)階段大部分模擬電路設(shè)計主要還是取決于設(shè)計者本身的直覺、技能和經(jīng)驗。

有了AI的幫助后,EDA工具在大量數(shù)據(jù)的訓(xùn)練下給出了先進的機器學習算法,使得模擬電路的布局布線有了更高效的自動化流程,尤其是在約束提取和生成,布局優(yōu)化上,模擬電路的優(yōu)化和生成及仿真驗證也可以在AI驅(qū)動下獲得提速。如此一來,每個模擬電路設(shè)計的迭代數(shù)量會進一步減少,芯片的上市周期也隨之縮短。

系統(tǒng)集成

近幾年流行起來的UCIe、Chiplet、3D封裝等,其實都是一個系統(tǒng)集成的概念。以此引入的設(shè)計與制造優(yōu)化方案也受到了持續(xù)關(guān)注,比如DTCO等。如何集成更多的晶體管、更多的內(nèi)存以及邏輯+內(nèi)存集成,還有最后軟件聯(lián)合硬件的熱管理等,都是系統(tǒng)集成需要考慮的問題。

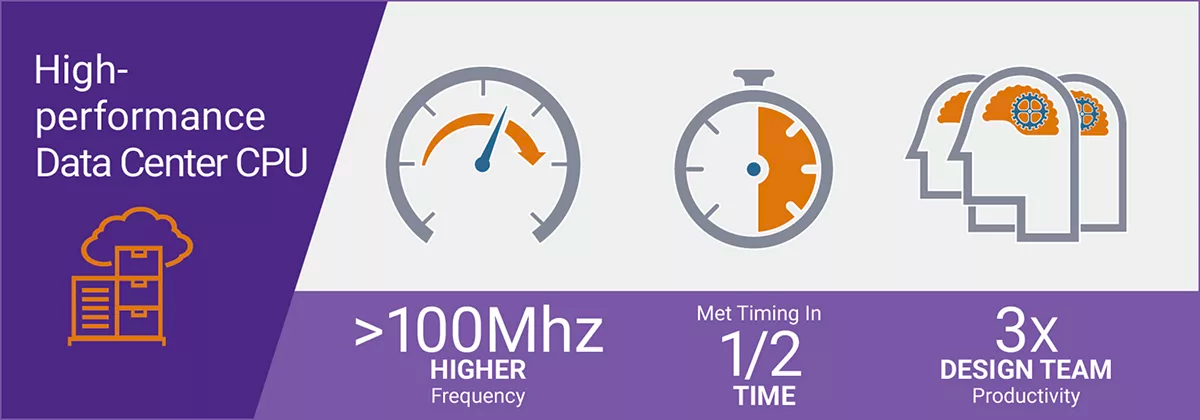

那么AI該如何從系統(tǒng)集成上進行優(yōu)化呢?答案就是提供一個更高效探索設(shè)計空間的路線,能夠給出預(yù)測模型和更快的實現(xiàn)方式,例如新思的DSO.ai和Fusion Complier,就提供了完備的AI設(shè)計方案,以求實現(xiàn)更好的PPA和更快的設(shè)計驗收。據(jù)了解,新思的這些方案最近在臺積電的N3E工藝上得到了驗證,為高性能計算、AI和移動設(shè)備等計算密集負載提供了增強的功耗、性能和良率。

寫在最后

其實一旦芯片設(shè)計進入AI輔助的時代,也對設(shè)計工程師們提出了相應(yīng)的更高要求,因為不少低級設(shè)計問題已經(jīng)被AI預(yù)測、優(yōu)化和生成給解決了。設(shè)計工程師們需要在更高層級的設(shè)計上實現(xiàn)創(chuàng)新,比如系統(tǒng)/軟件聯(lián)合優(yōu)化等等,這樣自己才不會被“優(yōu)化”掉。設(shè)計工程師們的專業(yè)技能,未來也會更加趨向于數(shù)據(jù)科學家需要掌握的技能,而數(shù)據(jù)科學家們也說不定會因此獲得搶設(shè)計工程師飯碗的機會。

驗證

驗證是芯片設(shè)計中最大的挑戰(zhàn)之一,我們已經(jīng)見識過了價格高昂的專用驗證硬件,以及驗證上云的潮流,這些都足以說明驗證是芯片設(shè)計中一個多么耗費資源的過程,這里指代的也不僅僅是硬件計算資源,還有時間資源。驗證所耗時間甚至可能高過其他流程,這些年諸多芯片開發(fā)團隊中的驗證工程師人數(shù)也在逐漸增長,增速甚至已經(jīng)超過了設(shè)計工程師,然而業(yè)內(nèi)卻很少有人去優(yōu)化驗證這個流程。

AI的出現(xiàn)終于讓這個缺口出現(xiàn)了松動,不少廠商都開始利用AI去優(yōu)化驗證這一流程,比如通過覆蓋率預(yù)測和激勵優(yōu)化來加速覆蓋率達標。Cadence也在今年發(fā)布了Verisium AI驅(qū)動驗證平臺,根據(jù)Cadence的說法,Verisium 的出現(xiàn)意味著SoC驗證從單運行單引擎算法,轉(zhuǎn)向了由AI和大數(shù)據(jù)輔助的多運行多引擎算法,從而減少了調(diào)試周轉(zhuǎn)時間、提高了調(diào)試效率,還會自動對失敗測試案例分類,減少人為分析的工作量。

模擬設(shè)計自動化

相對數(shù)字IC設(shè)計來說,模擬IC的設(shè)計顯然在自動化程度上還是差了不少的。在數(shù)字電路的設(shè)計過程中,整個流程的自由度是在逐級降低的。模擬電路設(shè)計雖然也是如此,但其下降幅度還是不比數(shù)字電路設(shè)計的,尤其是在布局布線和驗證上,所以自動化一直沒有提上日程,現(xiàn)階段大部分模擬電路設(shè)計主要還是取決于設(shè)計者本身的直覺、技能和經(jīng)驗。

有了AI的幫助后,EDA工具在大量數(shù)據(jù)的訓(xùn)練下給出了先進的機器學習算法,使得模擬電路的布局布線有了更高效的自動化流程,尤其是在約束提取和生成,布局優(yōu)化上,模擬電路的優(yōu)化和生成及仿真驗證也可以在AI驅(qū)動下獲得提速。如此一來,每個模擬電路設(shè)計的迭代數(shù)量會進一步減少,芯片的上市周期也隨之縮短。

系統(tǒng)集成

近幾年流行起來的UCIe、Chiplet、3D封裝等,其實都是一個系統(tǒng)集成的概念。以此引入的設(shè)計與制造優(yōu)化方案也受到了持續(xù)關(guān)注,比如DTCO等。如何集成更多的晶體管、更多的內(nèi)存以及邏輯+內(nèi)存集成,還有最后軟件聯(lián)合硬件的熱管理等,都是系統(tǒng)集成需要考慮的問題。

那么AI該如何從系統(tǒng)集成上進行優(yōu)化呢?答案就是提供一個更高效探索設(shè)計空間的路線,能夠給出預(yù)測模型和更快的實現(xiàn)方式,例如新思的DSO.ai和Fusion Complier,就提供了完備的AI設(shè)計方案,以求實現(xiàn)更好的PPA和更快的設(shè)計驗收。據(jù)了解,新思的這些方案最近在臺積電的N3E工藝上得到了驗證,為高性能計算、AI和移動設(shè)備等計算密集負載提供了增強的功耗、性能和良率。

寫在最后

其實一旦芯片設(shè)計進入AI輔助的時代,也對設(shè)計工程師們提出了相應(yīng)的更高要求,因為不少低級設(shè)計問題已經(jīng)被AI預(yù)測、優(yōu)化和生成給解決了。設(shè)計工程師們需要在更高層級的設(shè)計上實現(xiàn)創(chuàng)新,比如系統(tǒng)/軟件聯(lián)合優(yōu)化等等,這樣自己才不會被“優(yōu)化”掉。設(shè)計工程師們的專業(yè)技能,未來也會更加趨向于數(shù)據(jù)科學家需要掌握的技能,而數(shù)據(jù)科學家們也說不定會因此獲得搶設(shè)計工程師飯碗的機會。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

AI

+關(guān)注

關(guān)注

88文章

34912瀏覽量

277920

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

紫光同芯安全芯片如何破解防偽溯源行業(yè)痛點

近日,2025安全識別技術(shù)展覽會暨高峰論壇期間,紫光同芯高級產(chǎn)品經(jīng)理劉嘉維發(fā)表了題為《防偽溯源最佳實踐之安全芯片技術(shù)》的主題演講,系統(tǒng)性闡述了安全芯片如何破解防偽溯源行業(yè)痛點,并分享了

傳統(tǒng)攝像頭為什么需要升級為AI盒子?多場景痛點解析

系統(tǒng)具備了“看得懂”的能力,大幅提升了管理效率并降低了人力成本。?? 那么, 為什么傳統(tǒng)攝像頭需要升級AI盒子? 哪些場景必須依賴AI分析?小編將從安防、零售、工業(yè)三大典型場景出發(fā),解析傳統(tǒng)方案的痛

首創(chuàng)開源架構(gòu),天璣AI開發(fā)套件讓端側(cè)AI模型接入得心應(yīng)手

,成為開發(fā)者最頭疼的三大痛點。在Neutron Studio出現(xiàn)之前,AI應(yīng)用開發(fā)往往意味著多個工具鏈的反復(fù)切換,兼容適配問題頻發(fā),開發(fā)效率大打折扣。

而聯(lián)發(fā)科的AI應(yīng)用全流程開發(fā)工具

發(fā)表于 04-13 19:52

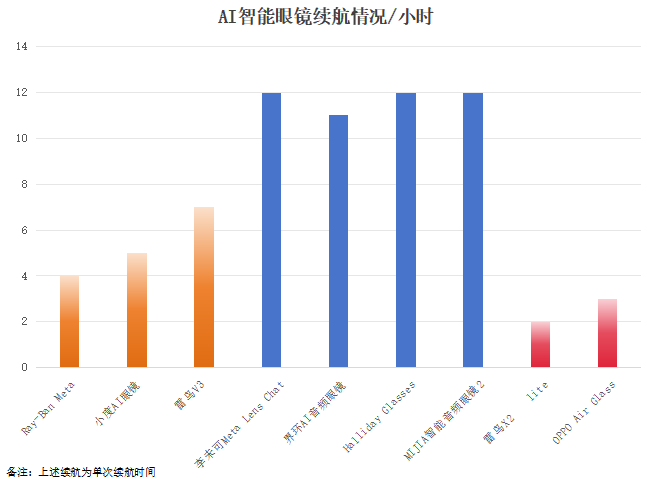

AR顯示+攝像頭成續(xù)航殺手?70uA超低功耗芯片直擊痛點

電子發(fā)燒友網(wǎng)報道(文/莫婷婷)功耗和續(xù)航是AR智能眼鏡等電子消費產(chǎn)品的核心痛點。以語音喚醒為例,無論是AI耳機還是智能眼鏡,語音喚醒作為服務(wù)入口。尤其在使用了更復(fù)雜的算法或模型之后,功耗問題成為一大

PT2513B芯片如何解決電剪刀電機控制器痛點

在電動工具市場中,電剪刀作為一款常用設(shè)備,其性能的優(yōu)劣直接影響到工作效率和用戶體驗。而電機控制器作為電剪刀的核心部件,其性能的好壞又取決于所采用的芯片。鈞敏科技主推的普誠(PTC)無刷電機控制芯片 PT2513B,正是一款專為解決電剪刀電機控制器

武漢特高壓串聯(lián)諧振如何突破行業(yè)三大痛點?

? 一、行業(yè)痛點與用戶需求 ? 痛點 傳統(tǒng)方案缺陷 武漢特高壓解決方案 設(shè)備笨重,搬運困難 電抗器數(shù)量多,總重超10噸 輕量化設(shè)計,總重降低60% 測試波形失真率高 諧波干擾導(dǎo)致誤判

新能源物流車如何破解傳統(tǒng)運輸痛點

樂趣橫生的參與感,更是通過沉浸式場景體驗,向果蔬運輸從業(yè)者展示新能源物流車如何破解傳統(tǒng)運輸痛點,助力行業(yè)綠色經(jīng)濟低碳轉(zhuǎn)型。

AI在芯片上的應(yīng)用:革新設(shè)計與功能

AI在芯片上的應(yīng)用正在深刻改變著芯片設(shè)計、制造和應(yīng)用的全過程。未來,隨著AI技術(shù)的不斷進步和應(yīng)用場景的不斷拓展,AI

應(yīng)急救援的痛點:大核桃單北斗防爆手持終端如何成為破局者?

在應(yīng)急救援的緊張與緊迫中,每一秒都至關(guān)重要。然而,傳統(tǒng)的應(yīng)急通訊設(shè)備往往面臨諸多挑戰(zhàn),從定位不準確到通信不穩(wěn)定,再到功能單一,這些問題都極大地限制了救援工作的效率與安全性。面對這些痛點,大核桃單北斗

【直播預(yù)告】ADI &amp; WT·世健MCU痛點問題探索季:MCU應(yīng)用難題全力擊破!

面臨著諸多挑戰(zhàn)與痛點,這些問題不僅關(guān)乎系統(tǒng)的性能與可靠性,更直接影響著整個系統(tǒng)的穩(wěn)定性與用戶體驗。為了深入剖析這些難題,WT文曄科技聯(lián)合ADI在行業(yè)媒體eeworld論壇發(fā)起了"

軟銀AI芯片代工轉(zhuǎn)投臺積電,Intel代工業(yè)務(wù)受挫

半導(dǎo)體代工領(lǐng)域近期發(fā)生重大變動,Intel的代工業(yè)務(wù)遭遇重大挫折。據(jù)業(yè)界消息,軟銀集團已決定將其AI芯片的代工訂單從Intel轉(zhuǎn)交給臺積電,這一決定標志著Intel在代工市場的初步嘗試面臨嚴峻挑戰(zhàn)。

光伏電站運維系統(tǒng)解決傳統(tǒng)光伏電站運維痛點

光伏電站運維系統(tǒng)解決傳統(tǒng)光伏電站運維痛點 隨著光伏電站的日益普及,光伏運維成為保障光伏電站安全、高效運行的重要手段,但是傳統(tǒng)的運維方式面臨著一系列挑戰(zhàn),為了應(yīng)對這些挑戰(zhàn)并提高運維效率,陜西公眾

IO模塊助力水處理行業(yè)升級,破解行業(yè)發(fā)展痛點

水處理行業(yè)作為關(guān)乎國計民生的重要領(lǐng)域,其發(fā)展水平直接影響到水資源利用效率和生態(tài)環(huán)境保護。然而,傳統(tǒng)水處理行業(yè)面臨諸多挑戰(zhàn)。明達技術(shù)利用IO模塊解決水處理行業(yè)的痛點問題,推動行業(yè)技術(shù)升級和可持續(xù)發(fā)展。

放心交給AI解決的芯片設(shè)計痛點

放心交給AI解決的芯片設(shè)計痛點

評論