一、SRIO協議與PCIe的區別

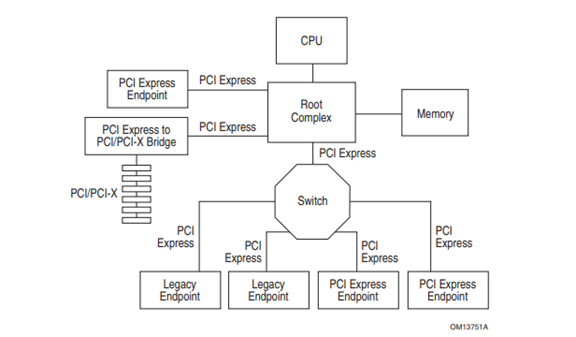

典型的PCIe結構定義了一個以單個中央處理器為核心的計算機系統,如常見的工控機、PXIe機箱控制器、服務器內的IO設備。從系統架構來看,這個結構的優勢在于可有統一的軟件驅動,軟件模型,設備間具備優異的兼容性。兼容性才是王道,廠商就可以用一個標準包打天下。

圖1 PCIe 互聯架構

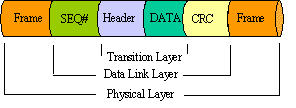

PCIe 的幀格式如下圖所示。

幀由 1 字節的幀起始、2 字節的序列號、16 或 20 字節的報頭、0 到 4096 字節的數據字段、0 到 4 字節的 ECRC 字段、4 字節的 LCRC、和 1 字節的幀結束。

數據字段中傳輸的位數越少,開銷就越大。零字節數據字段會導致 100% 的開銷,因為沒有傳輸數據。

圖 2 PCIe 的幀格式

二、RapidIO

RapidIO定義了一種高性能、分組交換互連技術,用于在微處理器、DSP、通信和網絡處理器、系統內存和外圍設備之間傳遞數據和控制信息。

RapidIO 適用于點對點的設備間通訊,不需要經過一個中央處理器進行調度,就可以完成設備間的通訊,并且包長度簡單,效率相對于PCIe要更高,有效數據傳輸速度更快。

但是RapidIO沒有定義標準的軟件模型,這就導致廠家之間的設備大概率無法兼容,從而只能在某些領域進行部署,不易推廣。 RapidIO 由于比PCIe更簡單、更高效、延遲更低等特點,已經在嵌入式領域、圖像處理、通訊系統、軍工航天有了大量的應用。

在實際的應用場景中,例如醫學影像等圖像處理領域,經常需要擴展單塊DSP、FPGA的計算能力,這時候需要將多個DSP或者FPGA通過高速串口進行互聯,此時RapidIO就是當前互換性最好的一個最佳選擇,因為PCIe太過復雜,Xilinx的Auraro效率也不滿足要求,并且互換性不好。

三、可用的SRIO驗證硬件

目前具備SRIO接口的硬件不多,

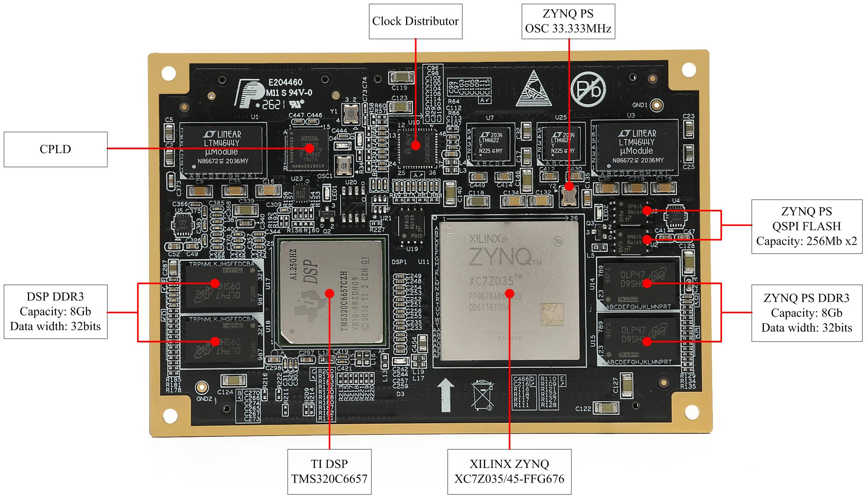

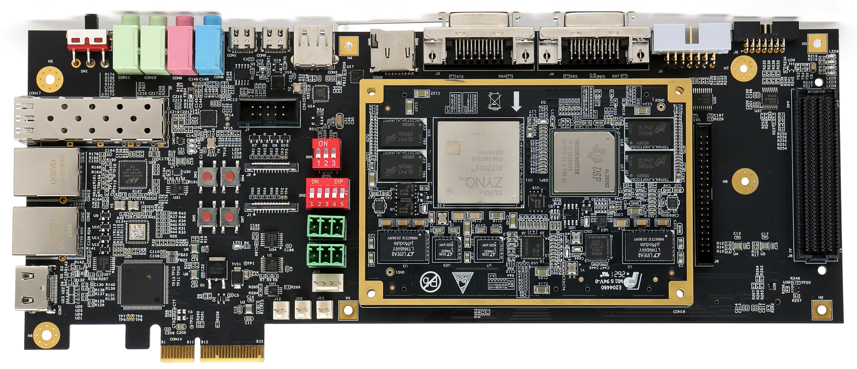

推薦廣州星嵌電子科技有限公司開發的DSP+FPGA+RAM開發板

也可用于評估EMIF等接口。

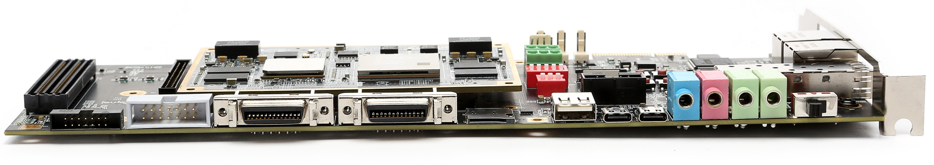

XQ6657Z35/45-EVM評估板,由廣州星嵌電子科技有限公司采用核心板+底板架構設計。

DSP選用TI TMS320C6657 雙核C66x 定點/浮點,主頻 1.25GHz/核;

FPGA選用Xilinx Zynq SoC處理器采用的XC7Z035-2FFG676I 或 XC7Z045-2FFG676I。

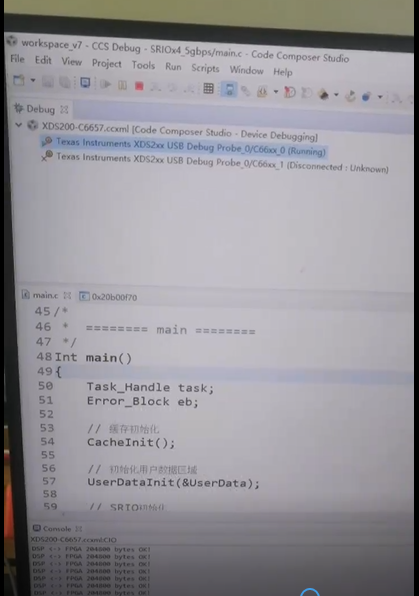

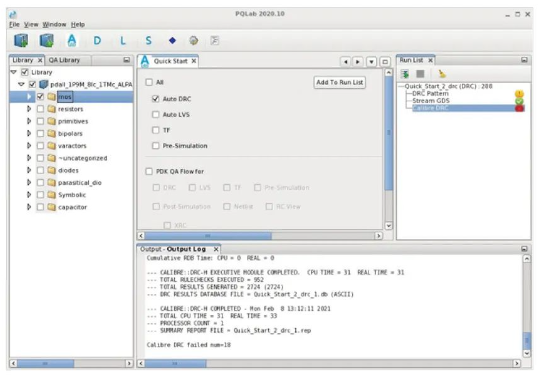

SRIO測試截圖

多核DSP C6657+ZYNQ7035工業核心板

多核DSP C6657+ZYNQ7035評估板正面俯視圖

多核DSP C6657+ZYNQ7035評估板側面圖1

多核DSP C6657+ZYNQ7035評估板側面圖2

審核編輯 黃昊宇

-

sRIO

+關注

關注

1文章

31瀏覽量

21269 -

PCIe

+關注

關注

16文章

1333瀏覽量

84940

發布評論請先 登錄

推動硬件輔助驗證平臺增長的關鍵因素

超大規模芯片驗證:基于AMD VP1902的S8-100原型驗證系統實測性能翻倍

概倫電子先進PDK驗證平臺PQLab介紹

概倫電子集成電路工藝與設計驗證評估平臺ME-Pro介紹

IC驗證云平臺優勢明顯,這家本土EDA公司如何御風先行?

西門子Veloce硬件輔助驗證平臺升級

憶聯天工平臺:加速SSD產品驗證,釋放超凡產能

憶聯企業級測試驗證平臺 以天工之智加速產品驗證,釋放超凡產能

DS64MB201在做自檢的時候,另外一個通路(正常通信)與板外依然保持LINK么?

TMS320C645x DSP串行RapidIO用戶指南

求助,關于TMS320C6678 datasheet問題求解

Nordic推出最新物聯網原型驗證平臺Thingy:91 X

SRIO介紹及xilinx的vivado 2017.4中生成srio例程代碼解釋

快速部署原型驗證:從子卡到調試的全方位優化

可用的SRIO RapidIO (SRIO)驗證平臺

可用的SRIO RapidIO (SRIO)驗證平臺

評論