關于軍事情報、監視和偵察 (ISR) 應用的一個簡單但必不可少的事實是,支持它們所需的傳感器帶寬和計算能力不斷增加。例如,今天,傳感器開放系統架構(SOSA)聯盟正在推動數據記錄儀的行業發展,該數據記錄儀可以支持100 Gb以太網和加密,以支持美國國防部(DoD)ISR路線圖。

直到最近,部署的數據存儲系統還基于串行 ATA (SATA) 總線接口,最高可達 3 Gb/s。按照這個速度,即使是具有RAID設計和多個加密器的用戶也無法達到所需的帶寬性能。好消息是,盡管SATA已經耗盡了最高性能ISR應用要求的燃料,但基于高速非易失性存儲器高速(NVMe)協議的新一代數據存儲系統的出現可以使傳輸/存儲性能比早期基于SATA的解決方案提高近50%,使Type 1 NSA加密和數據存儲達到以前無法實現的速度。

傳統接口(如 SCSI、ATA 和 SATA)最初設計用于基于旋轉介質的硬盤驅動器。如今,將 SATA 與更快的固態硬盤 (SSD) 內存結合使用會產生系統瓶頸。相比之下,NVMe內存被設計為與固態介質一起使用,并使數據能夠以閃存本身的完整讀/寫速度存儲。雖然前幾代數據記錄儀具有SATA接口,或者在存儲之前將PCIe轉換為SATA,但當今最先進的數據記錄儀使用NVMe內存來減少延遲并提高帶寬。

現在,得益于高速 Type 1 加密設計和使用 NVMe 消除存儲接口瓶頸,系統設計人員可以在整個數據存儲系統中實現更高的速率性能,從而為基于 SATA 的較慢的傳統加密解決方案提供強大的替代方案。

最近,在2019年9月舉行的美國空軍主辦的FACE [未來機載能力環境]/SOSA博覽會和技術交流會議上,Curtiss-Wright和L3Harris合作展示了基于高速PCIe Gen3通信和高性能NVMe存儲技術的下一代分類靜態數據戰術數據存儲系統的首次現場演示。演示系統自動監控射頻頻譜,以檢測、隔離和分類ISR通信信號,從而安全地了解任務環境。生成的元數據經過加密并安全存儲,允許進行后處理和進一步分析。

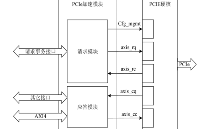

該演示系統采用L3Harris新的NSA Type-1認證就緒PCIe Gen3基于DataCrypt NVMe加密模塊,該模塊在Curtiss-Wright DSP模塊上運行,每個數據通道的讀/寫吞吐量為10/17 Gbps(標稱/最大)。每個加密設備都設計為支持兩個數據通道,當它們一起使用時,可提供 34 Gbps 的聚合吞吐量。此外,可以集成多個聚合模塊,以提供 100 Gbps 以太網速率。該演示系統安裝在Elma的符合SOSA標準的E-Frame開發平臺中,該平臺專為C4ISR / EW模塊化開放標準套件(CMOSS)而設計。它還具有基于AI的機器學習軟件應用程序,該應用程序提供了前面描述的信號分類功能,以及符合CMOSS標準且與SOSA對齊的2 MHz至6 GHz相位相干數字化調諧器。

除了新的 Type 1 加密器模塊外,演示還展示了為符合 SOSA 技術標準而開發的堅固耐用的開放式架構 OpenVPX 模塊,包括支持安全的 DSP 引擎、基于英特爾 Coffee Lake 的單板計算機和以太網交換機。

硬數字:數據存儲系統演示具有高達 34 Gbps 的總讀寫吞吐量、與主機和存儲設備的本機 NVMe 驅動程序 (NVMe 1.2) 的互操作性、從未分類到絕密的機密級別的并發多級安全處理、NSA Type 1 認證就緒加密引擎、符合 VITA 42.0 XMC(74 x 149 毫米)的單寬 XMC 夾層卡, 以及標準 VITA 42.0 XMC 和 VITA 42.3 XMC PCI Express 協議層 (PCIe Gen3)。

該演示表明,ISR 系統設計人員可以開始過渡到 PCIe Gen3/NMVe 架構的過程,以達到以前無法達到的加密數據存儲吞吐率。它還表明,100 Gb/s 的性能不再“遙遙無期”,而是現在可以實現的。

審核編輯:郭婷

-

傳感器

+關注

關注

2565文章

52869瀏覽量

766410 -

以太網

+關注

關注

41文章

5628瀏覽量

175656 -

SSD

+關注

關注

21文章

2965瀏覽量

119439

發布評論請先 登錄

NVMe協議研究掃盲

nvme IP開發之PCIe下

nvme IP開發之PCIe上

NVMe協議簡介2

PCIe與NVMe存儲的關系

Xilinx 7系列FPGA PCIe Gen3的應用接口及特性

陸芯科技推出650V60A GEN3 IGBT單管

PCIe Gen3和NVMe驅動分類靜態數據存儲速率

PCIe Gen3和NVMe驅動分類靜態數據存儲速率

評論