本文介紹了在低功耗系統中降低功耗同時保持測量和監控應用所需的精度的時序因素和解決方案。它探討了模擬前端時序、ADC時序和數字接口時序。它還將提供分析控制評估(ACE)定時工具的示例,以幫助系統設計人員和軟件工程師可視化測量時序的影響或設置。第1部分首先概述兩種主要的ADC類型,主要關注Σ-Δ架構。與SAR ADC架構相關的注意事項將在第2部分中介紹。

介紹

“時間至關重要”——這是一個古老的成語,可以應用于任何領域,但當應用于現實世界信號的采樣時,它是我們工程學科的支柱。當試圖降低功耗、滿足時序目標并保持性能要求時,必須考慮在測量信號鏈、Σ-Δ或逐次逼近寄存器(SAR)中選擇的ADC架構類型。一旦選擇了特定的架構,系統設計人員就會創建獲得必要系統性能所需的電路。此時,設計人員需要考慮其低功耗精密信號鏈最重要的時序因素。

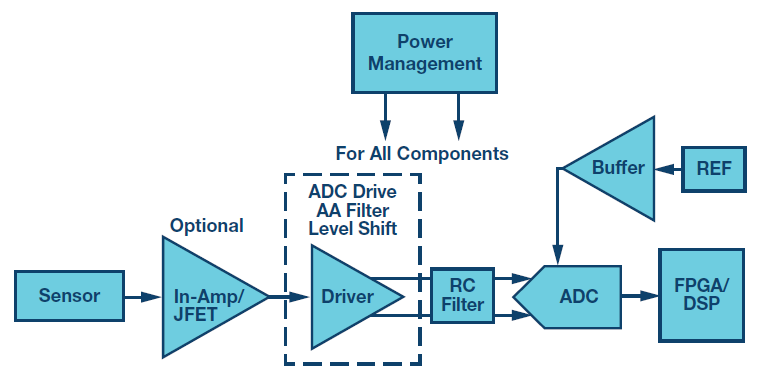

圖1.信號鏈時序考慮因素。

對速度的需求:低功率信號鏈的SAR或Σ-Δ?

我們將重點介紹測量帶寬低于10 kHz的精密低功耗測量和信號(如溫度、壓力和流量)(有關更多詳細信息,請參見精密低功耗),盡管本文中涵蓋的許多主題都可以應用于更寬帶寬的測量系統。

在探索低功耗系統時,從歷史上看,設計人員會選擇Σ-Δ型ADC來對慢速移動信號進行更高精度的測量。SAR被認為對于轉換更多通道的高速測量更有用,但AD4630-24等新SAR正在進入傳統上與Σ-Δ型ADC相關的高精度領域,因此這不是硬性規定。為了給出ADC架構的真實示例,在考慮與ADC信號鏈架構相關的時序時,我們看一下兩種低功耗產品,即AD4130-8 Σ-Δ型ADC和AD4696 SAR ADC,如表1所示。

| AD4130-8 | AD4696 | |

| 建筑 | Σ-Δ型ADC | 合成孔徑雷達 |

| 渠道 | 16 | 16 |

| 分辨率 | 24 位 | 16 位 |

| 最大速度 | 2.4 千米 | 1 兆微安全 |

| 電流消耗 | 轉換:2.4 kSPS 時為 32 μA 待機:0.5 μA | 轉換:10 kSPS 時為 58 μA 待機:2 μA |

| 低功耗特性 | 占空比先進先出 | 雙SDO自動循環 |

采樣頻率還是輸出數據速率?

SAR轉換器對輸入進行采樣,并在已知時間點捕獲信號電平。在初始采樣(和保持)階段之后,有一個轉換階段。獲得結果所需的時間主要取決于采樣頻率。

Σ-Δ轉換器以調制器頻率采集樣本。調制器過采樣,采樣速率遠高于輸入信號的奈奎斯特頻率。額外的頻率跨度允許噪聲轉移到更高的頻率。然后,ADC在調制器輸出端使用稱為抽取的過程,降低采樣速率以換取更高的精度。它是通過數字低通濾波器完成的,相當于時域平均。

由于技術達到轉換結果的方式存在差異,因此基于 SAR 的文檔將參考采樣頻率 (f樣本),而Σ-Δ數據手冊將側重于輸出數據速率(ODR)。我們將引導讀者區分兩者,因為我們更詳細地討論了有關時間的架構。

圖2.A SAR (?樣本) 與西格瑪增量 (ODR)。

對于在多個通道上執行一個轉換的多路復用ADC,在所有通道上執行轉換所需的時間(包括設置時間等)稱為吞吐速率。

信號鏈的第一個時序考慮因素是偏置/激勵傳感器和為信號鏈上電所需的時間。電壓和電流源必須打開,傳感器偏置,并考慮啟動時間規格。例如,對于基準電壓引腳上的特定負載電容,AD4130-8片內基準電壓源的開啟時間為280 μs。片內偏置電壓可用于激勵傳感器,其相關啟動時間為每nF3.7 μs,但這取決于連接到模擬輸入引腳的電容量。

在研究信號鏈中的上電時間后,我們需要考慮時序因素,具體取決于ADC架構。我們將從本文的下一部分開始,重點介紹在超低功耗應用中使用以Σ-Δ ADC為核心的測量信號鏈,以及與此類ADC相關的重要時序考慮因素。SAR和Σ-Δ信號鏈之間會有一些重疊,這會影響時序,例如使用旨在最小化微控制器交互時間的技術來實現系統級功耗的改進。當我們進入SAR ADC信號鏈時,這些將得到強調。

使用Σ-Δ型ADC時的信號鏈時序考慮因素

如果選擇的ADC是Σ-Δ而不是SAR,則需要考慮一組特定的時序考慮因素。在研究信號鏈時,需要探索的主要領域是模擬前端時序、ADC時序和數字接口時序,如圖1所示。

模擬前端時序注意事項

我們將從模擬前端(AFE)開始,分別關注這三個模塊。AFE可能因設計類型而異,但有一些共同的方面可以適用于大多數電路。

圖3.AFE Σ-Δ 時序注意事項。

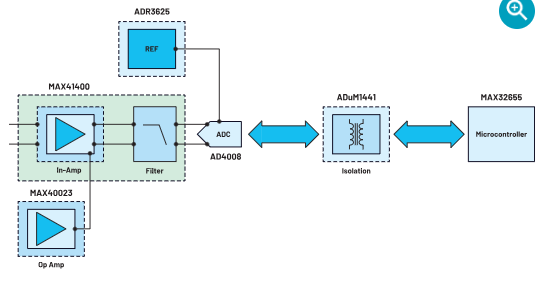

AD4130-8是精密低功耗信號鏈產品組的一部分,專門設計具有豐富的特性,可在降低功耗的同時實現高性能。其中一些特性包括板載FIFO、智能通道序列器和占空比。

AD4130-8是ADI公司最低功耗Σ-Δ型ADC。考慮到它包含許多關鍵的片上信號鏈構建模塊,例如片內基準電壓源、可編程增益放大器(PGA)、多路復用器和傳感器激勵電流或傳感器偏置電壓,超低電流令人印象深刻。

當我們考慮該器件的AFE時,它由一個片上PGA組成,使模擬輸入電流最小化,這消除了對外部放大器驅動輸入的需求。過采樣后跟數字濾波器可確保帶寬由數字濾波器主導。AD4130-8提供多種片內sinc3和sinc4濾波器以及設計用于抑制50 Hz和60 Hz噪聲的濾波器。sinc3和sinc4數字濾波器需要補充外部抗混疊濾波器。該抗混疊濾波器的目的是限制輸入信號的帶寬量。這是為了確保噪聲(例如,在fMOD(調制器頻率)下的變化率下不會混疊到通帶和轉換結果中。

圖4.AD4130 Σ-Δ簡化了系統模塊。

圖5.外部和內部濾波組合的模擬。

抗混疊濾波器

可以使用高階抗混疊濾波器,但通常使用一階單極點低通濾波器來滿足要求。濾波器基于對目標信號進行采樣而設計,公式1規定濾波器帶寬為3 dB:

當選擇電容值和電阻值時,較高的電阻更理想,但可能會增加噪聲,而較低的電容值達到一個限值,在此限值之后,引腳電容與外部電容的比值變得相關。

重要的是要知道電路充電所需的時間,具體取決于該電容器上可以看到的最大電壓階躍。

圖6.一階低通抗混疊濾波器。

在電容器上看到的電壓將隨時間變化,變化率為

VC= 某個時間點電容器兩端的電壓 VS = 施加的電源電壓

t = 時間

圖7.響應1 V滿量程階躍變化的一階低通濾波器建立時間。

上電時,VS,步長可以等于ADC的整個輸入電壓范圍(±V裁判/增益)。

圖7顯示,在4次常數(τ = R × C)之后,信號達到0.98 × VS.所需時間常數的數量可以通過步長之比V的自然對數計算得出S.

NT是輸入建立到LSB的一半以內時等待的時間常數數(VHALF_LSB)的ADC輸入電壓范圍。五世HALF_LSB在前面的公式中可以根據所需的電壓精度進行代入。如果系統設計人員希望解析到半LSB以內,對于具有N位分辨率和內部PGA增益= 1的雙極性輸入ADC,則為:

解析到實際輸入電壓 t 所需的時間ACQ變為時間常數數乘以 τ,等于 RC:

傳統上,在多路復用ADC的通道之間切換時,通道之間的大電壓擺幅(一個通道為負滿量程,下一個通道為正滿量程)將需要類似的計算。AD4130-8通過實現低功耗片內預充電緩沖器解決了這一問題,該緩沖緩沖器在通道之間切換時導通。這確保了在最快的數據速率下,切換通道后的第一次轉換將被正確轉換。還有一個片內PGA,設計用于提供完整的共模輸入范圍,這為系統設計人員提供了更大的裕量來應對廣泛變化的共模電壓。這對于測量信號很有用,但在最壞的情況下,一個通道可能處于負滿量程,而下一個通道可能處于正滿量程。

圖8.圖為帶有低通濾波器的隔離式AD4130-8電路。

示例:模擬前端低通濾波器

圖8中的示例顯示了一個惠斯通電橋傳感器,對于略低于16 kHz的24位ADC,具有–3 dB濾波。

R = 1 kΩ, C = 0.01 μF,帶 V裁判= 2.5 V,PGA增益設置為1:

圖8中的單端濾波器顯示主傳感器R = 1 kΩ和C = 0.01 μF:

圖8中的差分信號濾波器顯示主傳感器R = 1 kΩ和C = 0.1 μF。有關公式的詳細信息,請參閱 MT-070:

由于差分傳感器時間常數主導單端值,它將決定整個系統的計算:

此時,系統設計人員需要允許濾波器在上電時收集樣本之前從外部建立。這可以通過丟棄樣本在數字域中完成,或者可以延遲樣本瞬間以考慮這種充電。

設計濾波器時,電阻和電容值可能與前面所示的值不同。系統設計人員可以使用LTspice對濾波器和AD4130-8一起進行建模。LTspice還可用于對系統或信號鏈進行建模,如圖9所示,我們通過改變R2來仿真RTD行為。?

圖9.LTspice中RTD (R2)電路的仿真。

ADC 時序考慮因素

回想一下輸出數據速率是Σ-Δ型ADC時序的參考方式,讓我們研究與此類ADC相關的內部時序。

圖 10.Σ-Δ型ADC時序考慮因素。

這種類型的轉換器以高采樣速率對具有低分辨率(1位)ADC的模擬信號進行數字化處理。通過將過采樣技術與噪聲整形和數字濾波結合使用,可以提高有效分辨率。

SPI寫入數字寄存器允許用戶控制AD4130-8的過采樣和抽取率。調制器采樣率(f國防部) 是固定的。FS值實質上改變了數字濾波器用于獲得結果的采樣數量(AD4130-8以16為增量)。改變FS字會改變每個ADC結果的過采樣調制時鐘數。

圖 11.抽取。

由于抽取降低了ADC輸出端的有效采樣速率,因此可以實現更高的精度。抽取可以看作是去除過采樣過程引入的冗余信號信息的方法。使用的抽取越多(數字濾波器計算中包含的樣本越多),所述數字濾波器實現的精度就越高,但輸出數據速率越慢。

哪里:

f模數轉換器是輸出數據速率

f國防部是母時鐘頻率

FS是用于控制抽取率的乘數

過濾器延遲

當使能多個通道時,數據手冊輸出數據速率或ODR(f模數轉換器),并且數據吞吐率更加復雜。這是由于切換通道時數字濾波器的延遲。數字濾波器建立所需的時間取決于sinc濾波器類型。圖12顯示,sinc3濾波器的第一次轉換將需要三個轉換周期,直到達到相當于模擬輸入的數字。sinc4濾波器的第一次轉換將需要四個轉換周期。該 t解決是考慮多路復用器開關的用戶可編程建立時間。濾波器階數越高,噪聲越低,但缺點是濾波器建立所需的轉換周期數。

圖 12.篩選器延遲。

數字接口時序注意事項

為了幫助理解AD4130等Σ-Δ型ADC的數字接口時序,可通過ADI軟件工具ACE提供模型。計時工具是集成到 ACE 軟件中的多個軟件工具的一部分。有一個時序器時序圖和一個FIFO時序圖來幫助理解這些配置。

圖 13.AFE Σ-Δ數字接口時序注意事項。

AD4130-8時序控制器允許不同的輸入通道具有不同的數字濾波器和建立配置及時序。計時工具簡化了計算何時可以讀取數據的過程。

當啟用多個通道時,用戶不應錯誤地讀取已建立的通道ODR并除以啟用的通道數以計算吞吐速率,因為這不考慮數字濾波器延遲。在計算吞吐速率(有效ODR與數據手冊ODR)時,應考慮濾波器延遲。當啟用多個通道時,需要計算初始建立(tSETTLE)以及內部轉換周期數(t1st_CONV_IDEAL),如圖14所示。

圖 14.第一轉換輸出數據速率,包括濾波器延遲。

如果所有通道都具有相同的濾波器和建立配置,并且任何通道上都沒有重復轉換,則系統的吞吐速率變為:

哪里

CHs = 是否啟用的通道數

t1ST_CNV_IDEAL= 是轉換時間,包括濾波器延遲

t解決= 數字控制的時序參數,可以擴展,但具有最短的可編程時間,以考慮多路復用器建立

吞吐率可以通過查看1CNV_ODR時間的總和來計算,即圖 14 中綠色方塊之間的時間。

示例:壓力傳感器信號鏈時序

圖 15.簡化的壓力傳感器系統框圖。

如果我們想設計一個具有多個壓力傳感器的系統,如圖15中的壓力傳感器所示,并帶有一個溫度傳感器:

問題A:每個AD4130-8可以在系統中部署多少個壓力傳感器?

問題B:如果壓力傳感器的電壓輸出范圍為3 mV/V,我們可以期待什么分辨率?

問題C:如果工廠中的一條生產線需要至少14位的有效分辨率來滿足動態范圍系統的需求,那么系統需要多少個稱重傳感器?

A部分

第 1 步:選擇增益

影音DD= 1.8 V. 參考在+ 到 參考在– = 1.8 V

稱重傳感器在3 mV/V時的1.8 V激勵將導致每個稱重傳感器的最大輸出為5.4 mV。

PGA 的最大增益 = 128。

ADC輸入端的輸入電壓為5.4 mV×128 = 0.7 V,完全在1.8 V范圍內。PGA增益128是正確的使用增益。

步驟 2:選擇 FS 值

我們想選擇帶有 sinc3 過濾器和 FS = 1 的最快設置。

圖 16.計算 t 的總和1CNV_ODR使用計時工具。

步驟 3:使用一個通道的吞吐率計算系統中的通道數

1CNV_ODR = (1/1.667 毫秒) 600 SPS。

吞吐率 = 600 SPS/Nch。

1CNV_ODR = 具有相同配置且無重復轉換的多通道系統中單個通道的吞吐率。

可在 60 SPS 下對 10 個通道進行采樣。

答案 A:每個系統有 9 個稱重傳感器。

第 4 步:使用數據手冊有效分辨率表

另一點需要考慮的是,在查看噪聲和有效分辨率表時,計算需要基于FS濾波器值,而不是吞吐率。此處列出的 ODR 是單個通道上的已結算通道 ODR。

圖 17.FS 詞與增益。

系統設計人員在解釋數據手冊時需要小心。啟用多個通道時,SPS 中的吞吐率會降低。讀者可能會錯誤地解釋數據手冊中的分辨率表,并認為可以實現更高的分辨率。使用穩定通道ODR時,FS的變化會導致過采樣和抽取的增加,從而減慢系統速度以實現更高的精度。在啟用多個通道的情況下,SPS(吞吐量)中每個ADC通道的讀取速度下降是由于在多個通道上采樣。它不是由過采樣的增加引起的;因此,分辨率沒有增加。

圖 18.分辨率與增益數據手冊的關系表

B部分

如果我們查看數據手冊中的表格,我們會看到FS = 1和增益= 128的有效分辨率為11.7位。

答案 B:11.7 位。

C部分

為了解決 C 問題,我們需要回到 A 部分的幾個步驟:

步驟 2:選擇 FS 值

這一次,我們根據分辨率要求選擇 FS 值。為了實現 14 位的有效分辨率,應選擇 FS 為 3。

步驟 3:使用一個通道的吞吐率計算系統中的通道數

圖 19.使用時序工具更改濾波器類型和FS值,并讀取包括濾波器延遲在內的第一次轉換的輸出數據速率。

我們可以使用定時AFM來實現所需的分辨率(1/4.167 μs)。

240 SPS/Nch = 吞吐率。

我們可以在此數據速率下使用四個通道。

答案C:三個通道。

占空比

有些系統具有較低的吞吐率和較高的輸出數據速率,例如運行狀況監視設備,其中主機控制器會在大部分時間將系統置于待機模式并定期轉換。AD4130-8提供占空比,允許用戶連續轉換,器件進入待機模式,占空比的3/4或15/16,而器件轉換占空比的1/4或1/16。活動時間和待機時間是用戶選擇的設置的功能。

圖 20.占空比。

AD4130-8還集成了一個SYNC引腳,允許用戶確定性地控制何時在預選數量的通道上進行轉換。該器件還可配置為在降低電流待機模式下工作,啟動轉換序列,保持降低電流狀態,在多個通道上進行轉換,并在轉換完成后返回待機模式。

示例:啟用占空比

采用與前面的壓力傳感器信號鏈示例相同的設置,吞吐速率= 600 SPS/Nch,啟用兩個通道,ODR變為300 SPS,而采用3 V電源時平均電流為28.7 μA(見圖21)。

圖 21.啟用占空比之前的吞吐時間和電流。

啟用占空比1/16后,吞吐速率變為24.489 SPS,而平均電流變為4.088 μA(40.834 ms;見圖22)。

圖 22.啟用占空比后的吞吐時間和電流。

先進先出

AD4130-8內置FIFO。FIFO通過緩沖轉換并為微控制器或主機控制器提供在等待轉換時進入低功耗狀態的機會來降低系統功耗。這里最大的時序考慮因素是確保主機在連續轉換的同時足夠快地回讀FIFO,以避免錯過轉換。

用戶可以在收集指定數量的樣本(也稱為水印)后定期讀取FIFO。當達到所需數量的樣本時,中斷可用,主機將讀回FIFO。需要清空 FIFO 以清除中斷。用戶有一個預定義的時間段來從FIFO回讀數據。使用的 SCLK 頻率將決定在不丟失轉換的情況下可以讀取多少數據。

ACE軟件定時工具允許用戶改變SCLK頻率或使用門控時鐘來通知用戶在設計系統時何時需要降低水印水平。例如,先進先出回讀。

以最大 ODR 2400 kSPS 運行的連續單通道測量為例。如果水位線級別設置為 256 并且我們嘗試回讀,我們有 729.2 μs 的時間來回讀 FIFO,而不會錯過轉換。用戶需要回讀 4112 位。該工具通知用戶,為了讀回FIFO并且不錯過轉換,則需要5.64 MHz的主機SPI時鐘頻率。這打破了器件的5 MHz最大規格,并出現錯誤,允許用戶修改其水印以避免違反規格。

圖 23.AD4130-8 ACE軟件FIFO回讀窗口和警報。

| 主題 | 時序影響 | 低功耗信號鏈影響 |

| 信號鏈上電 | 延遲啟動每個塊 | 適用于所有信號鏈 |

| 抗鋸齒濾波 | 可能存在影響轉換結果的延遲 | AD4130-8切換通道時的預充電濾波器 |

| Sinc 濾波器延遲 | 多路復用系統的吞吐率受到影響 | 多路復用可提高節能效果 (μA/通道) |

| 占空比 | 占空比時吞吐率降低 | 平均電流成比例下降 |

| 先進先出 | 需要注意避免錯過轉化 | 主機控制器可以進入低功耗狀態 |

使用Σ-Δ型ADC時,我們可以看到需要考慮許多權衡、時序因素和特性。本文第2部分將探討SAR ADC技術以及影響基于SAR ADC的系統時序的因素和特性。

審核編輯:郭婷

-

傳感器

+關注

關注

2565文章

52869瀏覽量

766422 -

SAR

+關注

關注

3文章

426瀏覽量

46881 -

adc

+關注

關注

99文章

6681瀏覽量

548955

發布評論請先 登錄

利用隔離式精密信號鏈保持數據采集的準確度

精密信號調理研討會問答精選

ADI精密信號鏈的具體應用

使用SAR ADC構建低功耗精密信號鏈應用最重要的時序因素有哪些?

模擬前端時序、ADC時序和數字接口時序中的信號鏈考慮因素

低功耗精密數據采集信號鏈適用于空間受限的應用

低功耗精密信號鏈應用最重要的時序因素是什么

低功耗精密信號鏈應用最重要的時序因素是什么

評論