首先,從理論上講,Hold Time違例,是因為時鐘繞的太遠,到達時間太晚。而且綜合之后給出的時序報告都是估計值,因此綜合之后可以不考慮Hold Time,只考慮Setup Time;即便此時Hold Time違例,我們也不需要去理會。在Place Design之后再去看Hold Time,如果此時Hold Time的違例比較小(比如-0.05ns),還是不需要理會的,因為工具在布線時會修復Hold,但如果Slack太大了,無法修復了,就會犧牲setup來彌補hold。

如果出現(xiàn)了hold的違例,我們首先要分析時序報告,看是不是clock的skew太大了,hold違例一般都是時鐘的skew太大導致,如果skew太大,就要檢查原因了,是不是時鐘路徑上有buffer導致的,或者是因為時鐘跨SLR這種路徑太長導致。如果時鐘路徑上并沒有什么多余的buffer或者邏輯,那使用全局時鐘網(wǎng)絡(luò)帶來的skew是最小的。

這里補充一下綜合實現(xiàn)的步驟:

synth_design -> opt_design -> place-design -> phys_opt_design -> route_design

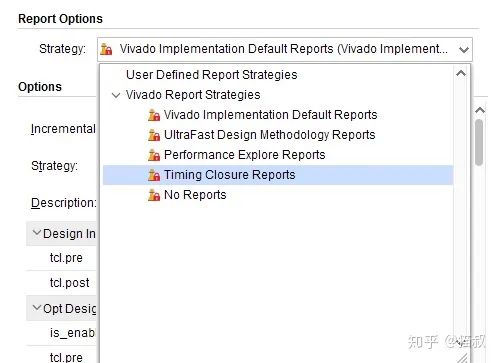

我們可以讓工具在每一步執(zhí)行后都會有時序報告,只需要把Report Options的策略選擇為Timing Closure Reports

如果route design之后hold time還是違例,可以使用tcl指令:

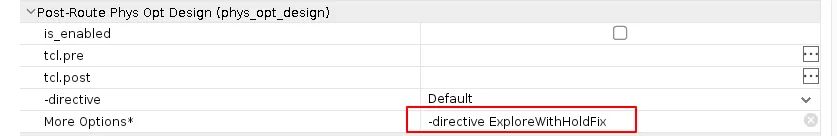

phys_opt_design -directive ExploreWithHoldFix

這個指令會嘗試不同的算法來優(yōu)化hold time違例(其實就是在數(shù)據(jù)路徑上插入LUT增加延遲)

或者在Implementation的時候指定,是一樣的效果。

Hold違例解決方法總結(jié)如下:

1. 檢查違例的時鐘是否是在全局時鐘網(wǎng)絡(luò)上,最好是讓時鐘走全局時鐘網(wǎng)絡(luò),減小skew

2. 檢查時序路徑上,避免有時鐘BUFFER的級聯(lián)

3. 插入延遲邏輯,在數(shù)據(jù)路徑上增加邏輯延遲(可以使用ExploreWithHoldFix讓工具自動插入,也可以手動修改代碼插入)

審核編輯:劉清

-

時鐘

+關(guān)注

關(guān)注

11文章

1893瀏覽量

133078

原文標題:Hold Time違例,該如何解決

文章出處:【微信號:傅里葉的貓,微信公眾號:傅里葉的貓】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Setup/Hold Time Problem

【FPGA經(jīng)典試題】電路模塊的setup-time和hold-time是正值還是負值

解釋下setup和hold time

請問AD80370中hold up time為負值是為什么?

2018年IC設(shè)計企業(yè)筆試題01英偉達Nvidia

出現(xiàn)時序違例的原因及解決辦法

什么是Setup和Hold時間

怎么解釋setup time和hold time的定義和在時鐘信號延遲時的變化呢?

Timing收斂 – 如何消除Hold Timing違例

建立時間和保持時間(setup time 和 hold time)

Vivado時序案例分析之解脈沖寬度違例

為什么setup檢查下一個沿而hold檢查當前沿

通過解剖一個邊沿觸發(fā)器簡要說明setup和hold產(chǎn)生原因

怎么解決解決Hold Time違例的問題呢

怎么解決解決Hold Time違例的問題呢

評論