大多數(shù)數(shù)字系統(tǒng)中,除了需要具有邏輯運算和算數(shù)功能的組合邏輯電路外,還需要具有存儲功能的電路,組合邏輯與時序邏輯可構成時序邏輯電路,簡稱時序電路。現(xiàn)在討論實現(xiàn)存儲功能的兩種邏輯單元電路,即鎖存器和觸發(fā)器。

雙穩(wěn)態(tài):電子電路中。其雙穩(wěn)態(tài)電路的特點是:在沒有外來觸發(fā)信號的作用下,電路始終處于原來的穩(wěn)定狀態(tài)。在外加輸入觸發(fā)信號作用下,雙穩(wěn)態(tài)電路從一個穩(wěn)定狀態(tài)翻轉到另一個穩(wěn)定狀態(tài)。由于它具有兩個穩(wěn)定狀態(tài),故稱為雙穩(wěn)態(tài)電路。

單穩(wěn)態(tài)電路只有一種穩(wěn)定狀態(tài),受到觸發(fā)以后,會自動轉到穩(wěn)定狀態(tài)。雙穩(wěn)態(tài)電路就兩種穩(wěn)定狀態(tài),受到觸發(fā)發(fā)后,就穩(wěn)定在那種狀態(tài),受到下一次觸發(fā)以后,再翻轉。

商店的彈簧門,就是一種“單穩(wěn)態(tài)”。人一推開門后,處在一種不穩(wěn)定狀態(tài),人一進入后就會自動回復到關門這種穩(wěn)定狀態(tài)。家中的普通門,就是“雙穩(wěn)態(tài)”,門一被打開,就停在那里了,是一種穩(wěn)態(tài);將它關上了,又是一種穩(wěn)態(tài)。

鎖存器:

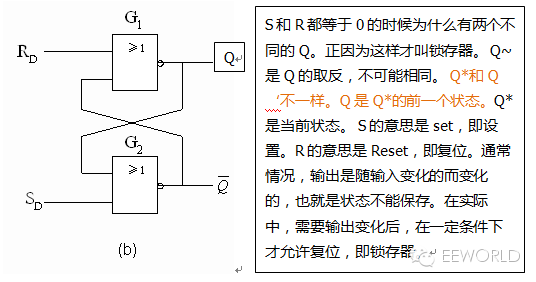

鎖存器是構成各種時序電路的基本元件,它的特點是具有0和1兩種穩(wěn)定的狀態(tài),一旦狀態(tài)被確定,就能自行保持,即長期存儲1位的二進制碼,直到有外部信號作用時才有可能改變。鎖存器是一種對電平敏感的存儲單元電路,它們可以在特定輸入電平作用下改變狀態(tài)。

鎖存器的當前狀態(tài)與前一個狀態(tài)有關。 當R為1,輸出被復位,即Q為0。不論前一個狀態(tài)是什么,即不論Q的值是1還是0。 當S為1,R為0的情況下,Q即為0。不論前一個狀態(tài)是什么,即不論Q的值是1還是0, 當S和R狀態(tài)相同時(不論是1還是0),Q的值為Q的值。即,保持狀態(tài),鎖存器。

代碼見1_latch

D鎖存器

邏輯門控D鎖存器: 由于當R、S為1的時候,鎖存狀態(tài)不確定,故為了消除SR鎖存器的不確定狀態(tài),可在電路的S和R輸入端連接一個非門G5從而保證S和R不同時為1的條件。此外還有傳輸門控D鎖存器,

觸發(fā)器

RS觸發(fā)器(RS (Reset-Set) flip-flop)

RS觸發(fā)器是雙穩(wěn)態(tài)觸發(fā)器,倆個與非門交叉耦合構成。由表可知它具有置“0”、置“1”和 “保持”三種功能。即在CP產(chǎn)生上升沿時才進行數(shù)據(jù)變化。RS觸發(fā)器分為上升沿觸發(fā)和下降沿觸發(fā)。注意Rd、Sd都是低電平有效。但我們到不需要注意這些,只需明白,cp上升沿時,R為0復位,這時輸出只和置位的S有關。如果R為1,則輸出均為0,根據(jù)電路結構可知。當RS均為1時會出現(xiàn)混亂,所以需要有約束條件來限制。

代碼見RS_regist

JK觸發(fā)器(JK (Jump-Key)flip-flop )

JK觸發(fā)器具有置0、置1、保持和翻轉功能,在各類集成觸發(fā)器中,JK觸發(fā)器的功能最為齊全。在實際應用中,它不僅有很強的通用性,而且能靈活地轉換其他類型的觸發(fā)器。由JK觸發(fā)器可以構成D觸發(fā)器和T觸發(fā)器。

D觸發(fā)器(data flip-flop)

D觸發(fā)器可以說是最常用的了。在寫Verilog時,觸發(fā)器均為D觸發(fā)器。雙穩(wěn)態(tài)多諧振蕩器(Bistable Multivibrator),是一種應用在數(shù)字電路上具有記憶功能的循序邏輯組件,可記錄二進位制數(shù)字信號“1”和“0”。觸發(fā)器是構成時序邏輯電路以及各種復雜數(shù)字系統(tǒng)的基本邏輯單元。觸發(fā)器的線路圖由邏輯門組合而成,其結構均由SR鎖存器派生而來(廣義的觸發(fā)器包括鎖存器)。觸發(fā)器可以處理輸入、輸出信號和時鐘頻率之間的相互影響。

代碼:D_flip_flop

T觸發(fā)器 T (Toggle flip-flop)

T觸發(fā)器是一種使用較多的觸發(fā)器,將JK觸發(fā)器的J、K輸入端相連,接成一個輸入端T,即J = K = T,組成的觸發(fā)器就稱為T觸發(fā)器。圖5.5.1為T觸發(fā)器邏輯符號。在JK觸發(fā)器的基礎上可以得出T觸發(fā)器的特性方程為

當T=0時,由其特性方程可得,即在時鐘信號的作用下,輸出端的狀態(tài)保持不變。

當T=1時,由其特性方程可得,即在時鐘信號下降沿的作用下,輸出端的狀態(tài)翻轉為相反的狀態(tài)。在這種條件下,也稱為觸發(fā)器

代碼:T_flop_flip

-

二進制

+關注

關注

2文章

805瀏覽量

42238 -

時序電路

+關注

關注

1文章

114瀏覽量

21913 -

鎖存器

+關注

關注

8文章

923瀏覽量

42239 -

觸發(fā)器

+關注

關注

14文章

2034瀏覽量

61988 -

單元電路

+關注

關注

4文章

32瀏覽量

19611

發(fā)布評論請先 登錄

FPGA學習之觸發(fā)器和鎖存器

FPGA學習之觸發(fā)器和鎖存器

評論