如何改變spi的時鐘頻率?

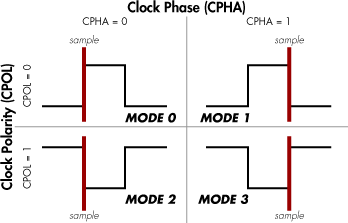

改變SPI的時鐘頻率需要以下步驟: 1. 選擇合適的時鐘源和分頻器:SPI接口的時鐘源可以是內部時鐘或外部時鐘,需要根據具體情況選擇;同時需要根據所需的SPI時鐘頻率,選擇合適的分頻器。 2. 配置寄存器:根據所選的時鐘源和分頻器,配置SPI控制寄存器中的位。有些MCU可能需要配置多個寄存器,需要根據具體情況選擇。 3. 啟動SPI:在配置完寄存器后,需要啟動SPI接口,讓其根據配置的寄存器位開始工作。 需要注意的是,改變SPI的時鐘頻率可能會影響通信的可靠性,因此需要在改變前進行充分測試和評估,確保系統的正確性和穩定性。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

接口

+關注

關注

33文章

8992瀏覽量

153661 -

時鐘

+關注

關注

11文章

1896瀏覽量

133160 -

SPI

+關注

關注

17文章

1801瀏覽量

95770

發布評論請先 登錄

相關推薦

熱點推薦

如何讓SPI額外發出一個時鐘?

現將2個ADC芯片進行菊花鏈式連接,手冊上給的時序圖中,兩個芯片讀數中間需要額外插入一個時鐘時序,要怎樣控制SPI輸出單個時鐘。還是說只能去用IO口模擬時序。IO口模擬的話速率又不如SPI

發表于 06-13 07:30

ADS1146的外接時鐘,以4.096MHZ為例,這個時鐘頻率是用來決定采樣頻率的么?

RDATA和RDATAC有何區別?兩者是否是獨立的?通過SPI寫控制命令的時候,是不是就和START的高低無關了?

2.、ADS1146的外接時鐘,以4.096MHZ為例,這個時鐘頻率

發表于 02-07 08:04

ads1298 DRDY輸出頻率一直是50HZ,無法改變,為什么?

我設置CONFIG1=0X06,CONFIG2=0X14,CONFIG3=0XC0,CH1SET=0X05,其余CH2~8SET=0X80,但是我時鐘頻率始終是50HZ,改變采樣率就是波形變丑了,會有不穩定,但是大致還是50H

發表于 02-07 06:59

iic協議與spi協議的區別

。 SPI :速度較快,可以達到幾Mbps到幾十Mbps,具體取決于時鐘頻率和硬件實現。 3. 地址方式 I2C :每個設備都有一個

TLC2574對SPI的時鐘頻率有沒有要求,最小是多少?

始終沒有觀察到EOC電平變化,始終是高,TLC2574輸出是固定的不對的值

TLC2574對SPI的時鐘頻率有沒有要求,最小是多少?我的SPI時鐘

發表于 01-16 07:58

ADS1282的SPI時鐘SCLK和芯片主時鐘MCLK有什么關系嗎?

ADS1282的SPI時鐘SCLK和芯片主時鐘MCLK有什么關系嗎? SCLK頻率太高會不會影響ADS1282配置或讀數失敗?

發表于 01-01 08:34

用SPI來配置ADS7229芯片,用外部時鐘SCLK和內部時鐘CCLK有區別嗎?

頻率會減小一半使用

2.手冊中在說明配置內部寄存器時,并沒有說什么腳電平如何拉低和拉高,所以想使用外部SPI提供的時鐘也沒辦法做到,在配置為內部時鐘或外部

發表于 12-23 07:58

ADS1256芯片用SPI控制,這個SPI的時鐘要怎么設置?

,這個ADS1256芯片用SPI控制,這個SPI的時鐘要怎么設置,是官方例程的那個SPI波特率吧?這個頻率有什么要求不?我的是stm32芯片

發表于 12-20 08:33

用ADS5560做數據轉換,輸出時鐘的占空比不是50%,改變輸入時鐘頻率占空比會變化,是正常的嘛?

現在用ADS5560做數據轉換,使用單端輸入時鐘,18MHz,發現輸出時鐘的占空比不是50%,改變輸入時鐘頻率占空比會變化,

發表于 12-20 07:27

spi master接口的fpga實現

串行外圍接口 大致了解: spi是個同步協議,數據在master和slaver間交換通過時鐘sck,由于它是同步協議,時鐘速率就可以各種變換。 sck:主機提供,從機不能操控,從器件由主機產生的

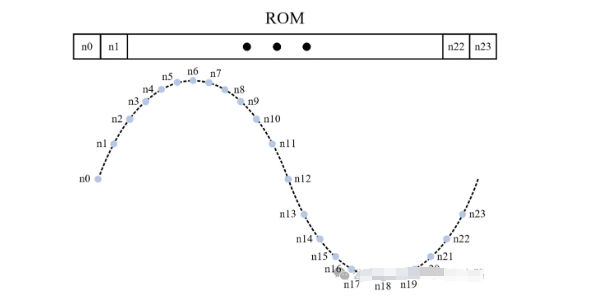

dds輸出頻率與時鐘的關系

DDS(Direct Digital Synthesizer,直接數字頻率合成器)技術是一種頻率合成方法,其輸出頻率與時鐘之間存在密切的關系。 一、DDS基本原理 DDS技術通過編程

DDR4時鐘頻率和速率的關系

DDR4(第四代雙倍數據率同步動態隨機存取存儲器)的時鐘頻率和速率之間存在著緊密的關系,這種關系對于理解DDR4內存的性能特性至關重要。以下將詳細探討DDR4時鐘頻率和速率之間的關系,

如何改變spi的時鐘頻率?

如何改變spi的時鐘頻率?

評論