隨著半導體行業朝著更先進的制程節點方向發展,靜態功耗已成為主要的設計限制因素。為此,亟需開發各種電源管理技術。例如,讓開發者可以創建多個電壓域,或者使用隔離單元將關斷的電源域與上電的電源域隔離。開發者可以在將信號電壓從一個域傳播到另一個域時,應用電平轉換器來放大或縮小信號電壓,或者可以使用保留單元來更快地將寄存器恢復到關斷前的狀態。就像在指定功能設計意圖時需要用到硬件描述語言(HDL)一樣,這些電源管理技術也需要一種通用語言來指定功耗設計意圖,那就是統一電源格式(UPF)。

考慮到當今的SoC非常復雜且通常針對特定的應用,為了設計和實現所需的功能并滿足時序和功耗要求,需要付出巨大的努力。但是,僅僅做到這些還是不夠。終端用戶總是渴望在最短的時間內獲得最新的功能,這給IP開發團隊帶來了壓力。為了滿足產品上市時間目標,芯片設計公司通常采用并行開發方法,由不同的團隊分別編寫寄存器傳輸級(RTL)、新思科技設計約束(SDC)文件、UPF文件等。

盡管設計和UPF的開發是齊頭并進的,但它們的時間表可能會有所不同,而這可能會帶來一些挑戰。本文將介紹如何使用新思科技獨立于設計的VC LP UPF檢查器(VC UPF)來應對這些挑戰。本文還將討論VC UPF如何幫助開發者在RTL準備好之前清理UPF文件中獨立于設計的各種問題。

優化SoC設計的功耗

設計SoC時,UPF的第一個版本可能在RTL最終確定之前就已經準備好了。但只有在設計就緒后,才能驗證UPF的準確性和完整性。因此,通常會有一個“等待期”,負責編寫UPF的開發者需要等待第一版RTL敲定,才能繼續后面的工作。在設計就緒后,開發者會運行一個靜態檢查器工具來驗證UPF與設計的一致性,往往在這時,開發者會發現UPF中存在的一些基本問題,其實這類問題本可以在不讀取設計的情況下就能找出。之前的等待實際上已經浪費了一些時間。而反復多次的UPF修復和檢查會導致周轉時間變得很長。

這就是VC UPF的用武之地。

顧名思義,VC UPF讓負責功耗設計意圖的開發者能夠在RTL就緒之前開始清理UPF文件中獨立于設計的問題。該解決方案包括:

UPF語法和語義檢查

UPF電源分析檢查

PST一致性檢查

UPF網絡相關一致性檢查

方法特定檢查(基于允許/不允許的命令和選項)

我們來看幾個例子,了解一下該解決方案能提供哪些幫助。

一種情況是UPF電源網絡未定義任何電源狀態。只有在閱讀設計、加載UPF并完成UPF檢查之后,用戶才會意識到:由于缺少狀態,有一些路徑無法進行分析。有了VC UPF,開發者將會在幾分鐘內獲得這些信息。

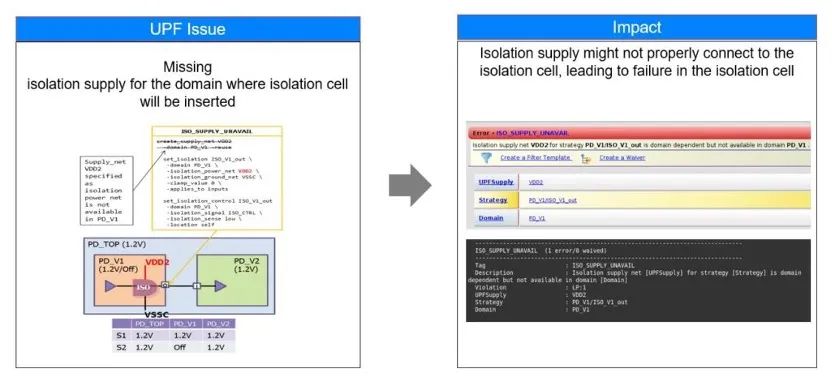

在另一種情況下,用于隔離策略的隔離電源網絡在所需的域中可能不可用。

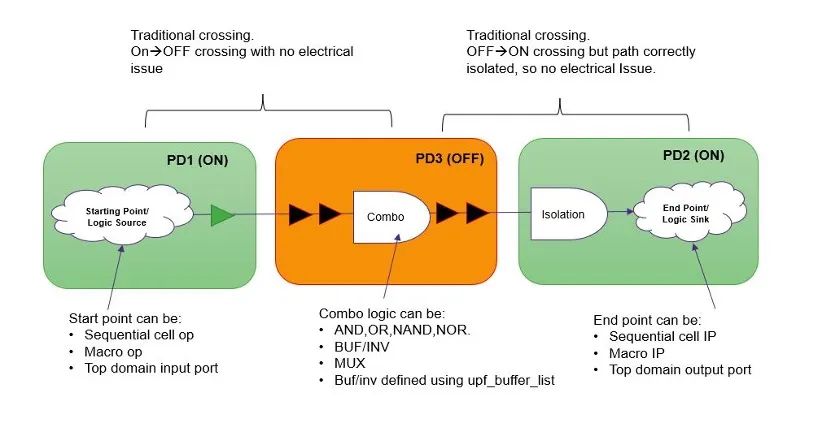

再來看另一個例子,比如從PD3到PD2的路徑。由于OFF–>ON交越得到了隔離單元的正確保護,因此不存在電氣問題。于是,傳統的電氣檢查不會標記任何違例。但在同一情況下,還存在一個功能問題,即來自PD1的信號會被PD3(電源處于OFF狀態)中的組合邏輯電路阻擋。

VC LP中全新的預檢查功能可以正確地標記該問題,并提醒開發者:盡管該路徑被正確隔離,但來自PD1的信號會被OFF域中的組合邏輯電路阻擋,只有鉗位值會到達PD2。

鑒于這一違例,開發者應驗證該路徑是否要在指示的電源狀態期間攜帶功能信息。如果它在給定的電源狀態下不攜帶功能信息,則無需進一步的操作。但如果該路徑需要攜帶功能信息,則需要為所示的緩沖器/反相器/組合邏輯電路通電,并且需要修復組合邏輯電路的電源連接。通過仿真來識別這些問題非常耗時,而借助VC LP,開發者現在可以在設計周期的早期階段發現這些問題,從而節省仿真時間。

盡管VC UPF的主要用途是早期清理UPF,但它也可以用于SoC的UPF管理。復雜的SoC具有來自不同供應商/設計團隊的IP模塊UPF文件,這通常會導致UPF修改推遲、時間表延誤,甚至要重新驗證。為了避免這些情況,CAD團隊可能會強制執行一些GuideWare規則,以符合IP供應商的UPF交付要求,從而確保SoC集成順利完成。VC UPF可以使用disallow_*命令或allow_*命令來協助執行此類GuideWare UPF架構檢查。

類似地,在SoC集成期間,開發者可能不希望某個特定的IP級UPF TCL變量被頂層覆蓋。帶有設計檢查工具的標準UPF不會將這種情況識別為問題。但是,利用VC UPF,開發者可以指定此類受保護變量的列表,并快速發現其中是否有任何變量已被頂層UPF所覆蓋。此外,開發者還可以驗證IP的UPF版本與SoC UPF的兼容性。根據用戶指南中關于允許和禁止的UPF版本組合,VC UPF可以執行IP與SoC的一致性檢查。請注意,除此以外,VC LP不考慮UPF版本,使用“upf_version”不會產生任何影響。

經認證的功耗感知靜態檢查簽核

新思科技的VC LP解決方案為UPF提供了準確且經過認證的支持,它與以下工具緊密集成,可用于靜態低功耗檢查和調試:

總結

毋庸置疑,要設計出滿足所需功能、時序和功耗要求的低功耗SoC,需要付出大量精力,而且還面臨著產品上市時間緊迫的壓力。通常,芯片設計公司選擇并行開發方法,由不同的團隊分別編寫RTL、設計約束文件、UPF文件等。但是,盡管設計和UPF的開發可以齊頭并進,但它們的時間表會有所不同。

VC LP解決方案讓負責功耗設計意圖的開發者能夠在RTL就緒之前開始清理UPF文件中獨立于設計的問題。該解決方案也可用于SoC的UPF管理,因為復雜的SoC通常具有來自不同供應商的IP UPF文件,而這可能會導致UPF修改推遲、時間表延誤,甚至要重新驗證。通過在早期階段清理UPF,開發者可以在低功耗SoC設計周期中節省時間和精力。

原文標題:VC LP解決方案:左手極致低功耗,右手高效驗證左移

文章出處:【微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

-

新思科技

+關注

關注

5文章

864瀏覽量

51412

原文標題:VC LP解決方案:左手極致低功耗,右手高效驗證左移

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

芯知識|廣州唯創電子WT2003H語音芯片:智能低功耗,喚醒隨心控

低功耗藍牙智能門鎖應用

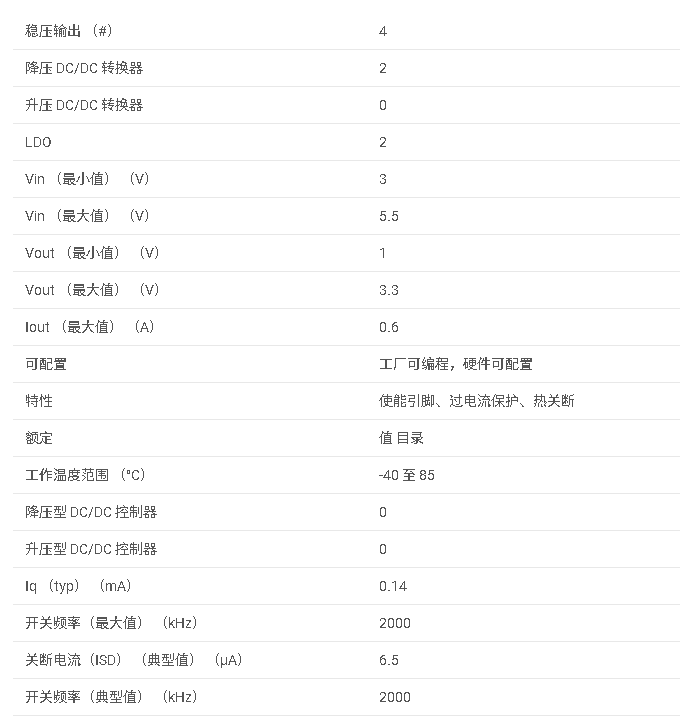

LP3905系列 用于低功耗手持應用的電源管理 IC數據手冊

高效低功耗:基于onsemi NCP1341的65W適配器電源方案

蜂窩物聯網的超低功耗特性

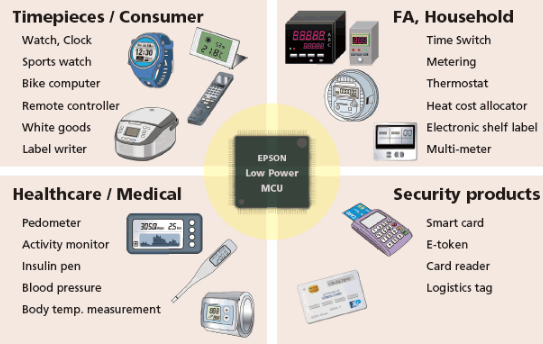

愛普生S1C17W00系列16位單片機:基礎控制的高效低功耗解決方案

安富利推出S2-LP超低功耗射頻收發器

BLE低功耗藍牙模塊在答題器中的應用方案

YXC超低功耗時鐘解決方案 1.2V超低電平有源晶振 新品發布

引領智能未來:英銳恩科技的國產低功耗單片機ENMCU

低功耗毫米波雷達解決方案使電池供電類接近感應產品實現新功能

適用于超低功耗和低功耗應用的獨特高效隔離式DC/DC轉換器

適合低功耗 HMI 按鈕應用的 LDC2112/LDC2114 電感應觸控解決方案數據表

VC LP解決方案:左手極致低功耗,右手高效驗證左移

VC LP解決方案:左手極致低功耗,右手高效驗證左移

評論