一、帶隙基準反饋極性分析:

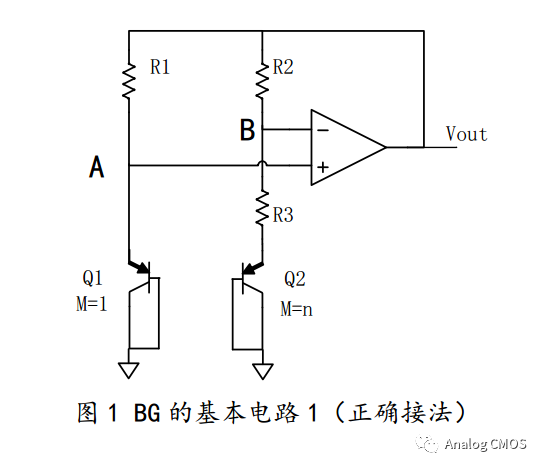

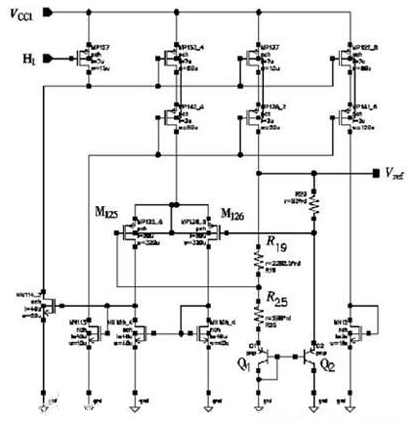

1.1****原理圖一:

輸出電壓:

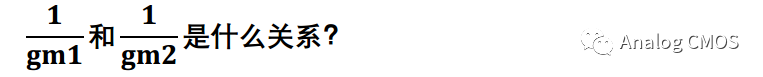

我們知道對于上圖的pnp二極管接法,向下看的輸入阻抗是1/gm,那么對于Q1和Q2他們個數不同,電流相同的情況下,輸入阻抗一樣嗎?換句話說:

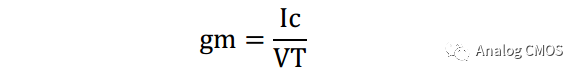

對于三極管的gm表示方式:

因為兩個pnp的電流一樣,所以根數上式,可以得到:

gm1=gm2

也就是:(為了方便,把PNP的輸入阻抗表示成RQ)

主要來分析一下電路的反饋:

反饋信號從輸出端反饋回兩個輸入端 A 和 B

反饋類型是:

電壓-電壓反饋

由于前饋通道的絕對值一樣,所以直接比較正反饋因子和負反饋因子,來分析反饋極性

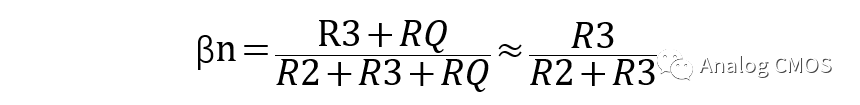

負反饋因子:

正反饋因子:

觀察βn和βp,兩個分式的分母在同一個量級,而分子:

RQ <

**

所以:

βn<<βp

也就是說這個bg結構含 有兩個反饋環(huán)路 ,一個是正反饋一個是負反饋,負反饋的環(huán)路增益大于正反饋,所以整個系統(tǒng)還是負反饋。

下面我們來看看另外一個比較常見的bg結構

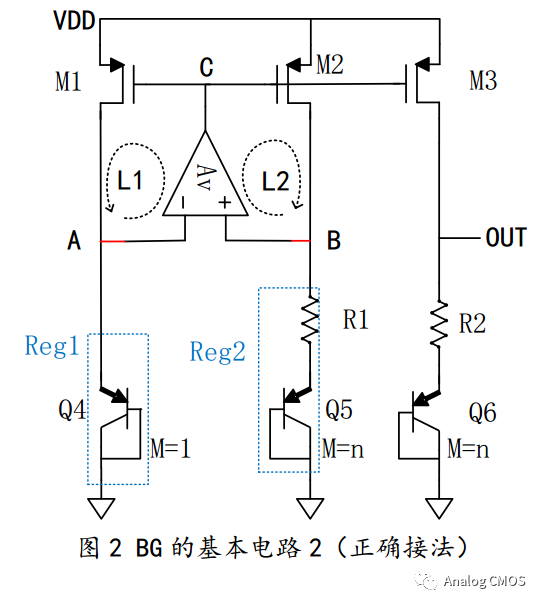

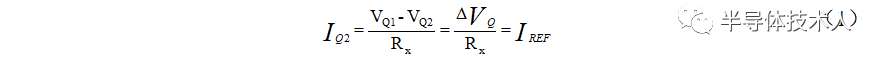

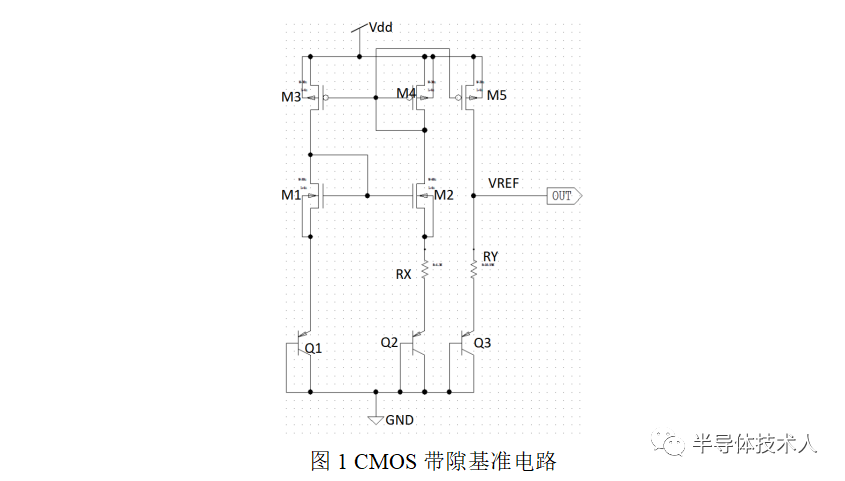

** 1.2 原理圖二:**

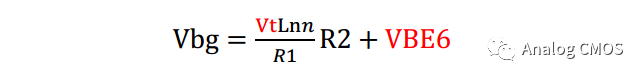

輸出電壓:

反饋類型判斷:

反饋量是電流,電流乘以如圖的Req得到電壓(VA、VB)作為運算放大器的輸入,所以反饋類型是:

電流—電壓反饋

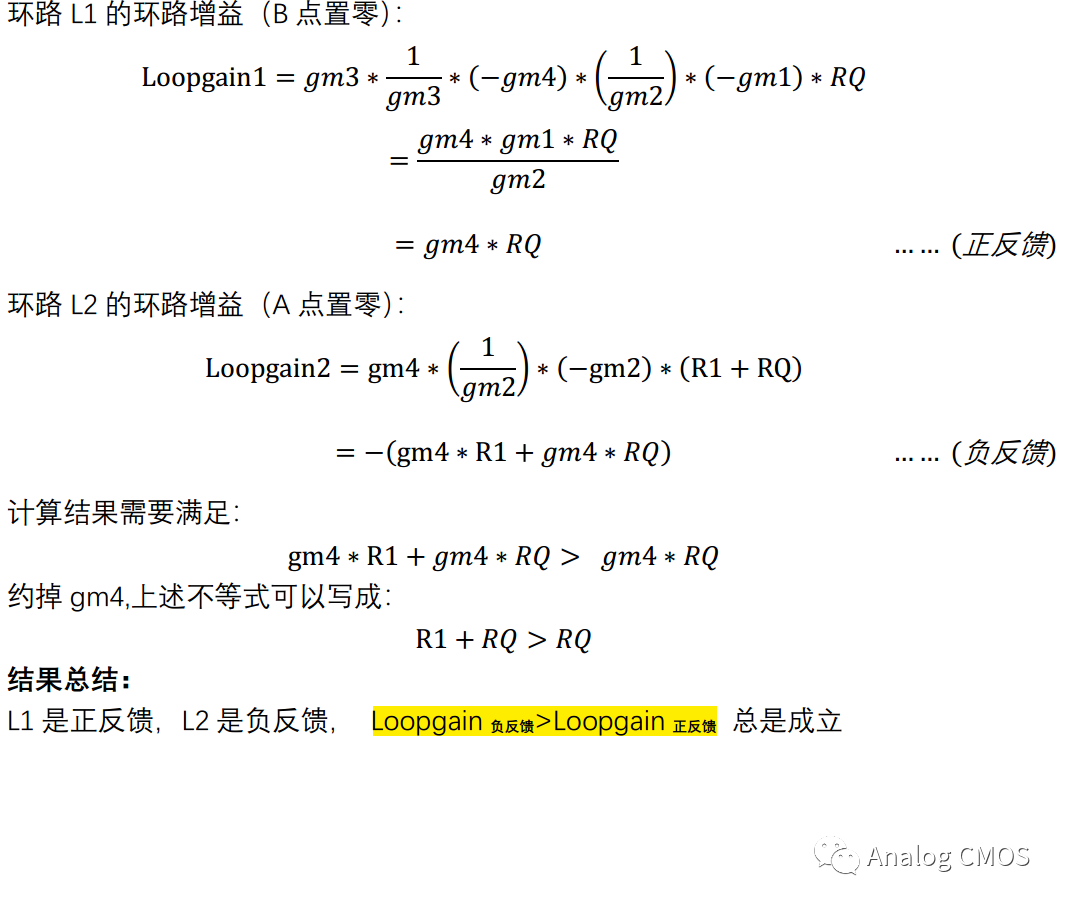

正確接法****環(huán)路增益計算:

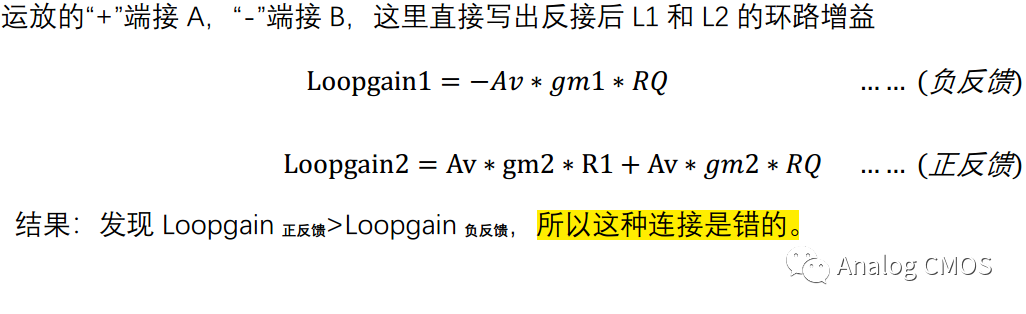

錯誤接法****環(huán)路益計算:

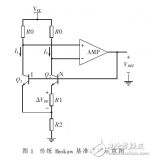

**1.3 **原理圖三:

對于圖3:

輸出電壓:

反饋類型判斷:

由于反饋量是電流,電流乘以 Req 得到電壓作為輸入,所以反饋類型是

電流-電壓反饋

正確環(huán)路****增益計算:

錯誤環(huán)路****增益計算:

總結:以上三種或者說兩種Bandgap Voltage電路,有 兩個反饋環(huán)路 (正反饋環(huán)路、負反饋環(huán)路),我們需要注意分析電路的結構,設置正確的偏置方法,在反饋類型上確定電路的穩(wěn)定。

**

-

二極管

+關注

關注

148文章

10072瀏覽量

171073 -

帶隙基準電路

+關注

關注

0文章

14瀏覽量

10818 -

失調電壓

+關注

關注

0文章

198瀏覽量

14324 -

PNP管

+關注

關注

1文章

28瀏覽量

7864

發(fā)布評論請先 登錄

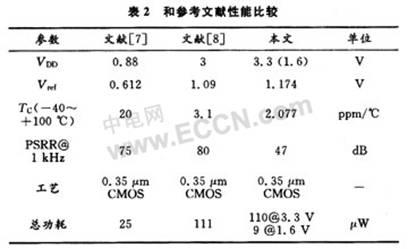

低溫漂CMOS帶隙基準電壓源分析

基于LDO穩(wěn)壓器的帶隙基準電壓源設計

基于汽車環(huán)境的帶隙基準電壓源的設計

14位Pipeline ADC設計的帶隙電壓基準源技術

CMOS帶隙基準電壓源曲率校正方法

帶隙電壓基準源的設計與分析

帶隙基準電壓模塊之反饋極性分析

帶隙基準電壓模塊之反饋極性分析

評論