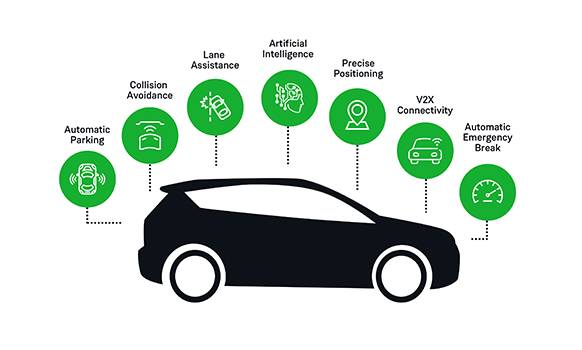

提高汽車電氣化和自動(dòng)駕駛的一個(gè)主要方面是先進(jìn)駕駛輔助系統(tǒng)(ADAS)的普及。如今,這些系統(tǒng)正迅速應(yīng)用于市場上幾乎所有的車輛,而且隨著技術(shù)的成熟,這一趨勢只會(huì)持續(xù)下去。然而,隨著技術(shù)的發(fā)展,ADAS設(shè)計(jì)人員面臨的硬件挑戰(zhàn)變得越來越復(fù)雜。在本文中,我們將介紹ADAS的硬件需求,FPGA如何填補(bǔ)這些空白,以及為什么eFPGA IP將成為下一個(gè)ADAS硬件趨勢。

ADAS的硬件要求

ADAS在現(xiàn)代汽車中的發(fā)展給底層硬件帶來了一些嚴(yán)峻的挑戰(zhàn)。在像ADAS這樣的關(guān)鍵任務(wù)應(yīng)用中,最重要的目標(biāo)是確保車輛乘員的安全。這個(gè)目標(biāo)要求系統(tǒng)準(zhǔn)確、可靠和實(shí)時(shí)地工作(即低延遲)。同時(shí),這些系統(tǒng)需要在盡可能低的功耗下運(yùn)行,以保持電池壽命并延長電動(dòng)汽車(Electric Vehicle)的續(xù)航里程。

平衡這些需求對ADAS來說是一個(gè)巨大的挑戰(zhàn),因?yàn)橄到y(tǒng)往往依賴于大量的數(shù)據(jù)和計(jì)算密集型的任務(wù),如機(jī)器學(xué)習(xí)算法。因此,ADAS硬件必須獲取數(shù)據(jù),通過傳感器融合匯集數(shù)據(jù),運(yùn)行機(jī)器學(xué)習(xí)算法,然后采取行動(dòng)——所有的都需要實(shí)時(shí)運(yùn)行,并以最低的功耗預(yù)算——這顯然不是一件容易的事。

汽車設(shè)計(jì)人員需要一個(gè)靈活且可擴(kuò)展的硬件平臺(tái)來滿足快速發(fā)展的規(guī)格變化,這進(jìn)一步加劇了這一挑戰(zhàn)。

硬件加速和FPGA

為了解決ADAS硬件面臨的嚴(yán)峻挑戰(zhàn),設(shè)計(jì)人員正在采用專用硬件加速器來提高性能,而不是傳統(tǒng)的基于CPU的架構(gòu)。從比較常規(guī)的計(jì)算資源(如CPU或GPU)轉(zhuǎn)移,通過專用硬件加速器為特定應(yīng)用程序提供了更好的性能和能效。基于在此范圍內(nèi),選擇通常介于FPGA和ASIC之間,F(xiàn)PGA提供最大的靈活性,ASIC提供最高的性能。

FPGA的一個(gè)關(guān)鍵特性是FPGA能夠提供高級別的并行性,同時(shí)仍然可以針對特定的工作負(fù)載進(jìn)行編程。結(jié)果表明,F(xiàn)PGA在工作負(fù)載加速方面提供了顯著的價(jià)值,特別是在性能和延遲作為關(guān)鍵的情況下。此外,與比較常規(guī)的CPU和基于GPU的系統(tǒng)相比,F(xiàn)PGA可以給需要加速的工作負(fù)載提供每瓦最佳的性能,從而幫助系統(tǒng)平衡性能和功率效率之間的權(quán)衡。

同樣重要的是,由于FPGA可編程特性,其在可擴(kuò)展性方面比ASIC更具優(yōu)勢。這種適應(yīng)性在如ADAS等底層算法瞬息萬變的機(jī)器學(xué)習(xí)系統(tǒng)中尤為重要。此外,ASIC的規(guī)格必須提前幾年定義,而FPGA可以在一分鐘內(nèi)更新和重新編程。此功能使基于FPGA 的ADAS系統(tǒng)能夠提供ASIC根本無法實(shí)現(xiàn)的可擴(kuò)展性和多功能性。

由于這些原因以及更多的原因,目前汽車中已經(jīng)搭載了超過2.5億顆FPGA,其中超過7500萬顆用于ADAS應(yīng)用。

行業(yè)趨勢:用于ADAS的eFPGA

盡管硬件加速功能強(qiáng)大,但像FPGA和ASIC等器件通常仍無法完全獨(dú)自運(yùn)行。今天的ADAS解決方案需要將硬件加速器與CPU集成在一起,其目的是在系統(tǒng)級別處理許多通用型和組織型任務(wù)。正是由于這個(gè)原因,異構(gòu)計(jì)算平臺(tái)(如異構(gòu)SoC)已經(jīng)成為加速和ADAS平臺(tái)中最常見的平臺(tái)之一。

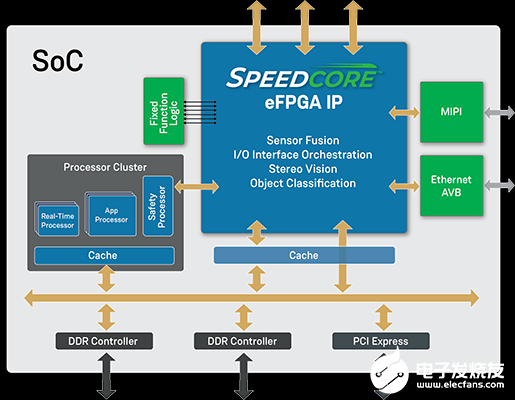

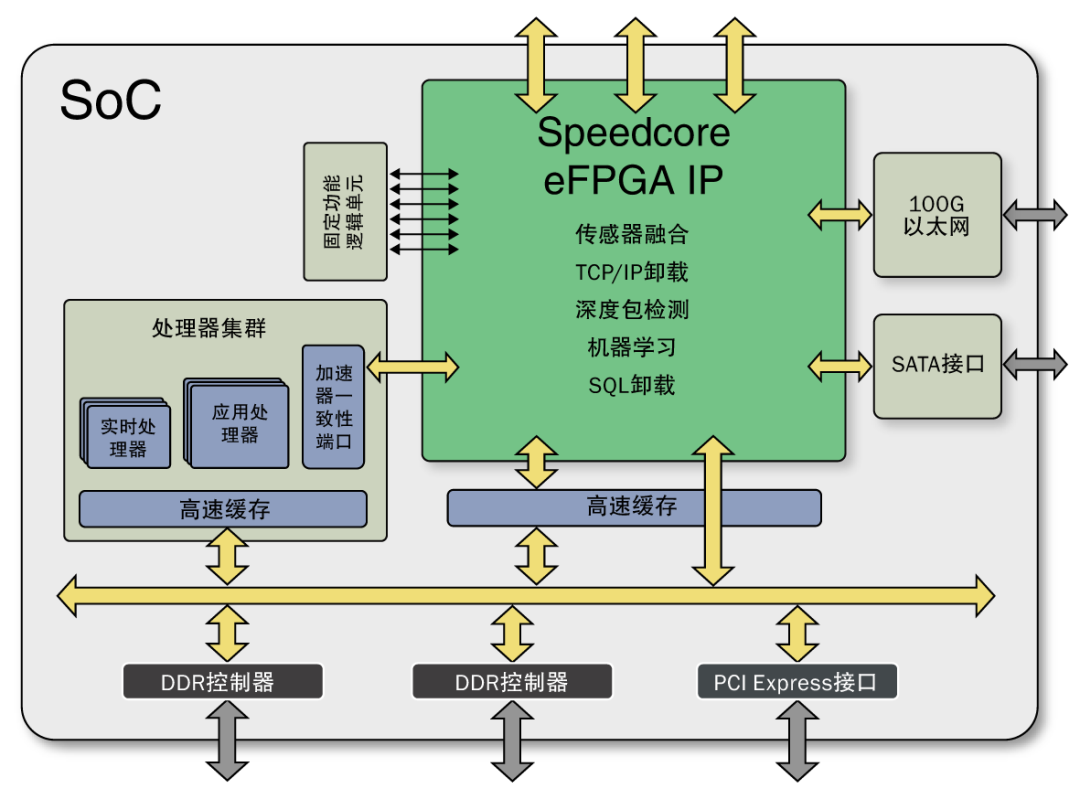

圖:Achronix的Speedcore IP這樣的eFPGA技術(shù)可以與CPU資源緊密耦合

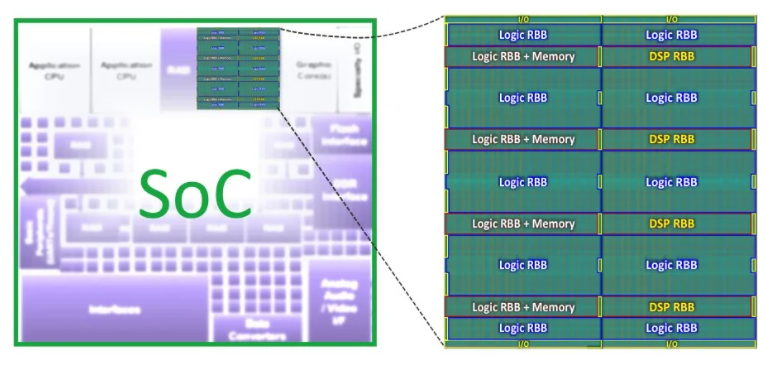

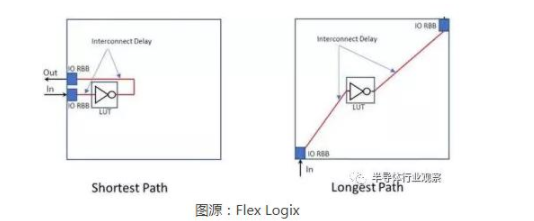

因此,我們相信ADAS計(jì)算的下一個(gè)主要趨勢將是嵌入式FPGA(即eFPGA)IP在定制ASIC中的興起。借助eFPGA IP,設(shè)計(jì)人員能夠利用FPGA技術(shù)的優(yōu)勢,同時(shí)將其硬件加速與其他ASIC子系統(tǒng)(如CPU和I/O接口)緊密耦合。通過將FPGA與CPU一起嵌入到定制SoC中,與分立式FPGA解決方案相比,eFPGA IP可顯著節(jié)省成本、功耗和空間。

具體來說,我們的評估表明,與基于FPGA的獨(dú)立系統(tǒng)相比,eFPGA IP集成可以幫助設(shè)計(jì)人員節(jié)省90%的成本、降低75%的功耗、延遲改善100倍、接口帶寬增加10倍。因此,ADAS將在不久的將來逐步采用基于eFPGA技術(shù)的異構(gòu)解決方案。

Achronix的行業(yè)角色

如今Achronix是唯一一家同時(shí)大批量生產(chǎn)獨(dú)立FPGA芯片和eFPGA IP解決方案的公司。得益于我們的Speedcore eFPGA IP等旗艦產(chǎn)品,迄今為止,我們已經(jīng)在多個(gè)行業(yè)領(lǐng)域授權(quán)了超過1500萬個(gè)基于eFPGA的產(chǎn)品。隨著對ADAS計(jì)算需求的不斷增長和演進(jìn),我們認(rèn)為有能力支持這些變化并賦能下一代計(jì)算平臺(tái)。

-

FPGA

+關(guān)注

關(guān)注

1645文章

22033瀏覽量

617753 -

嵌入式

+關(guān)注

關(guān)注

5148文章

19645瀏覽量

316991 -

adas

+關(guān)注

關(guān)注

310文章

2257瀏覽量

210171 -

efpga

+關(guān)注

關(guān)注

1文章

33瀏覽量

15858

發(fā)布評論請先 登錄

首款嵌入式FPGA誕生 能為AI帶來什么?

嵌入式 FPGA (eFPGA) 技術(shù)的過去、現(xiàn)在和未來

為什么嵌入式FPGA(eFPGA)IP是ADAS應(yīng)用的理想選擇?

FPGA是嵌入式系統(tǒng)設(shè)計(jì)的理想選擇

嵌入式FPGA的相關(guān)資料下載

嵌入式 FPGA (eFPGA) 時(shí)代已到!淺談FPGA技術(shù)的過去、現(xiàn)在和未來

嵌入式FPGA的發(fā)展前景如何

Achronix宣布用于SoC加速的Speedcore嵌入式FPGA IP產(chǎn)品開始供貨

一文讀懂eFPGA 選擇是要注意的四個(gè)步驟

SoC設(shè)計(jì)中嵌入FPGA(eFPGA)內(nèi)核實(shí)用評估方法

eFPGA是什么?幾個(gè)關(guān)于eFPGA的常見迷思

eFPGA在嵌入式360度視域視覺系統(tǒng)中有何應(yīng)用

對嵌入式FPGA的詳解

Primemas選擇Achronix eFPGA技術(shù)用于Chiplet平臺(tái)

Achronix Speedcore eFPGA的特性和功能

為什么嵌入式FPGA(eFPGA)IP是ADAS應(yīng)用的理想選擇?

為什么嵌入式FPGA(eFPGA)IP是ADAS應(yīng)用的理想選擇?

評論