節(jié)通過硬件描述語言Verilog HDL對二十進制編碼器的描述,介紹Verilog HDL程序的基本結(jié)構(gòu)及特點。

二十進制編碼器及Verilog HDL描述

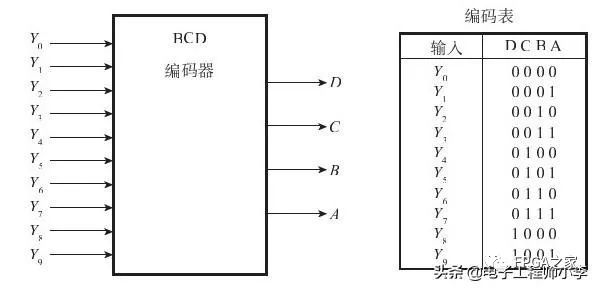

二十進制編碼器是數(shù)字電路中常用的電路單元,它的輸入是代表0~9這10個輸入端的狀態(tài)信息。輸入信號為高電平時,輸出相應的BCD碼,因此也稱為10線4線編碼器。其功能表及電路符號如圖3-1所示。

圖3-1二十進制編碼器

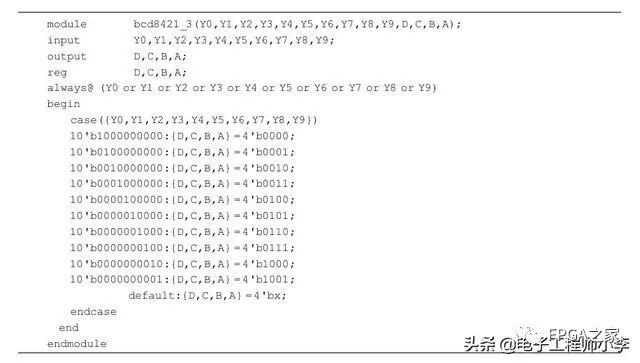

【例3-1】利用Verilog HDL對二十進制編碼器進行設計。

Verilog HDL程序的基本構(gòu)成

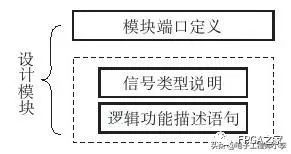

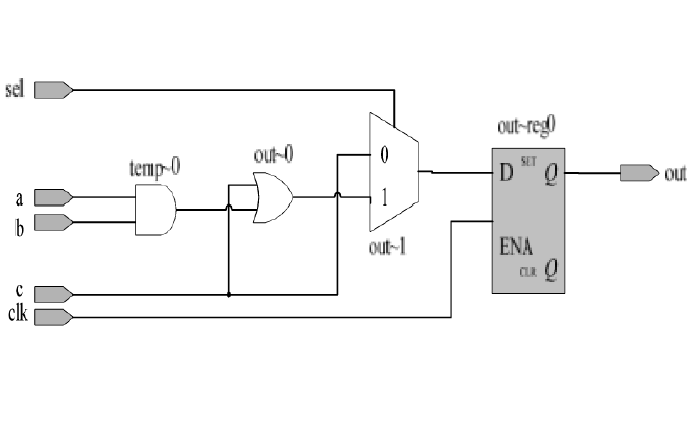

從例3-1可以看出,一個完整的Verilog HDL程序由3個基本部分構(gòu)成,分別是:模塊端口定義部分、信號類型說明部分和邏輯功能描述語句部分。其結(jié)構(gòu)圖如3-2所示。

圖3-2Verilog HDL程序基本結(jié)構(gòu)

模塊端口定義部分

對于硬件描述語言來說,一個程序代表了一個具有某種邏輯功能的電路,模塊端口定義部分描述了該電路的接口部分的信息,即輸入輸出信號的信息。

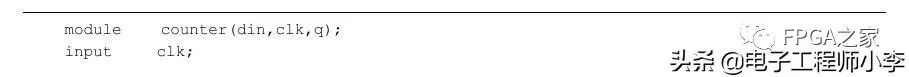

模塊端口定義部分的語法結(jié)構(gòu)如下:

module模塊名(端口信號1,端口信號2,端口信號3,端口信號4,……);

input[width:0]端口信號1,端口信號3,……;

output[width:0]端口信號2,端口信號4,……;

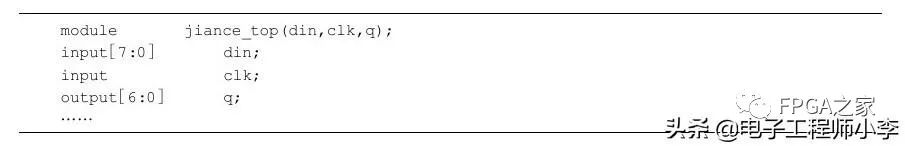

程序以關鍵詞module引導,模塊名是設計者對于設計的電路所取的名字,在模塊端口定義的第1行列出了所有進出該電路模塊的端口信號,在第2行和第3行中定義了各端口信號流動方向。流動方向包括輸入(input)、輸出(output)和雙向(inout),[width:0]表示信號的位寬,如果位寬沒有特別說明,則系統(tǒng)默認為1位寬度。

【例3-2】模塊端口定義舉例。

信號類型說明部分

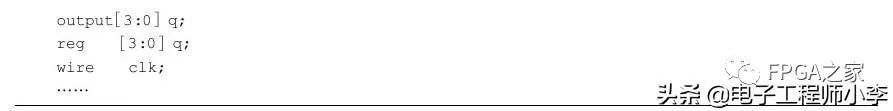

在Verilog HDL語法中,信號共有兩種數(shù)據(jù)類型,分別為:網(wǎng)線類型(net型)和寄存器類型(register型)。在信號類型說明部分除了要對輸入/輸出端口的信號類型進行說明之外,還要對程序中定義的中間量的數(shù)據(jù)類型進行說明。

信號類型說明部分的語法結(jié)構(gòu)如下:

wire[width:0]信號1,信號2,……;

reg[width:0]信號3,信號4,……;

【例3-3】信號類型說明舉例。

邏輯功能描述語句部分

邏輯功能描述語句部分對輸入/輸出信號之間的邏輯關系進行了描述,是Verilog HDL程序設計中最主要的部分,在電路上相當于器件的內(nèi)部電路結(jié)構(gòu)。在Verilog HDL語言中,常用的邏輯功能描述語句可以分為以下3種:

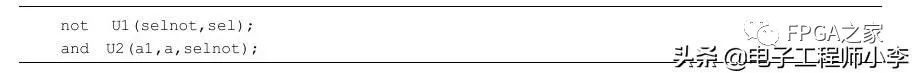

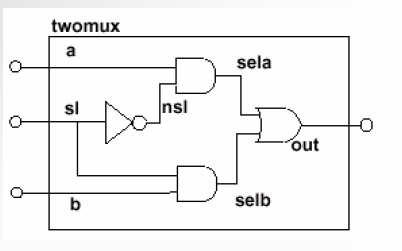

例化語句:調(diào)用已進行元件化封裝的程序。這種語句常應用于層次化設計的頂層文件設計中。

【例3-4】例化語句舉例。

該語句分別調(diào)用了一個非門和與門電路模塊。

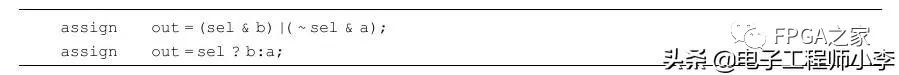

連續(xù)賦值語句:描述信號之間簡單的賦值關系。在連續(xù)賦值語句中,右邊表達式使用的操作數(shù)無論何時發(fā)生變化,右邊表達式都重新計算。這類描述通常以關鍵詞assign引導。

【例3-5】連續(xù)賦值語句舉例。

該語句描述了輸出信號與輸入信號的賦值關系。

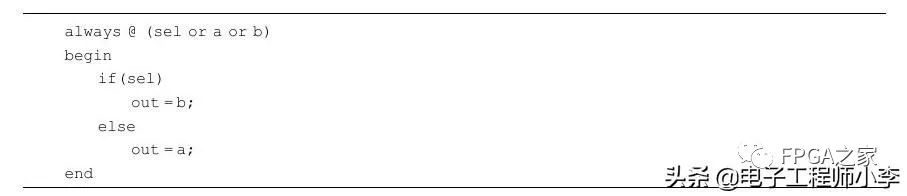

過程語句:以關鍵詞always、initial等關鍵詞引導的語句,描述了一定條件下信號之間的賦值關系。這種變量數(shù)據(jù)被賦值后,其值保持不變,直到下一次條件具備時對它們重新賦值。

【例3-6】過程語句舉例。

與連續(xù)賦值語句一樣,always和initial也描述了輸出信號與輸入信號的賦值關系,但是這種賦值往往是一種比較復雜的條件賦值,例如,例3-6就用了if……else語句描述了輸出信號與輸入信號的條件關系。

-

編碼器

+關注

關注

45文章

3786瀏覽量

137641 -

Verilog

+關注

關注

29文章

1366瀏覽量

112080 -

HDL

+關注

關注

8文章

330瀏覽量

47938 -

程序

+關注

關注

117文章

3825瀏覽量

82713

原文標題:邏輯功能描述語句部分

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

【FPGA學習】Verilog HDL有哪些特點

Verilog-HDL實踐與應用系統(tǒng)設計

什么是Verilog HDL?

Verilog HDL程序基本結(jié)構(gòu)與程序入門

Verilog HDL語言簡介

Verilog HDL程序設計教程_王金明

Verilog HDL硬件描述語言_結(jié)構(gòu)建模

Verilog HDL入門教程之Verilog HDL數(shù)字系統(tǒng)設計教程

Verilog HDL的基礎知識詳細說明

Verilog教程之Verilog HDL程序設計語句和描述方式

二十進制編碼器及Verilog HDL描述 Verilog HDL程序的基本結(jié)構(gòu)及特點

二十進制編碼器及Verilog HDL描述 Verilog HDL程序的基本結(jié)構(gòu)及特點

評論