I2C總線能掛多少設(shè)備?

理論上:

7-bit address :2 的 7 次方,能掛 128 個(gè)設(shè)備。

10-bit address :2 的 10 次方,能掛 1024 個(gè)設(shè)備。

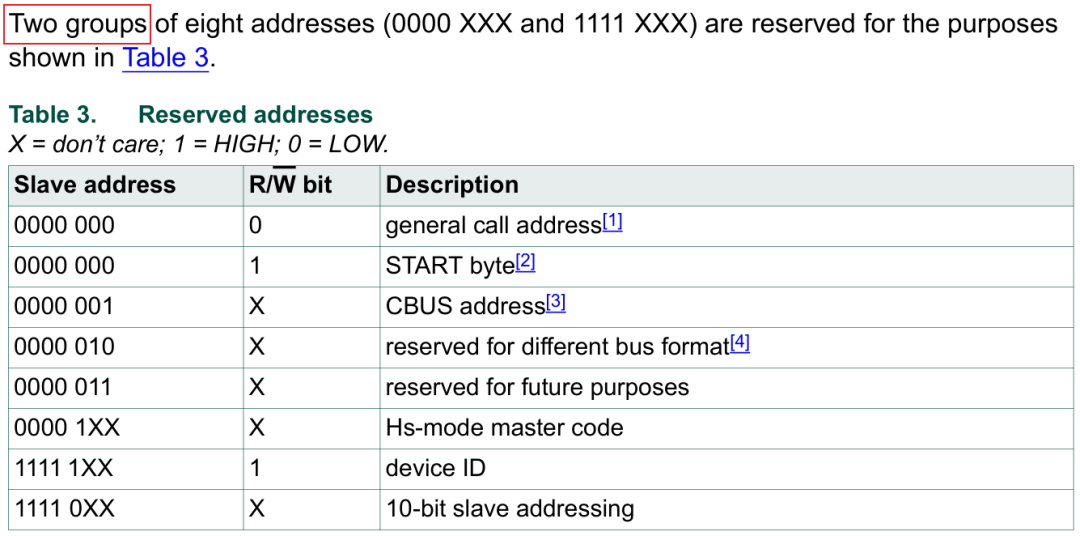

當(dāng)然,要把預(yù)留設(shè)備地址去除,7 bit 協(xié)議規(guī)定了 8個(gè)預(yù)留地址,普通廠商不可以使用。保留地址如下:

但是 I2C 協(xié)議規(guī)定,總線上的電容不可以超過(guò) 400pF。管腳都是有輸入電容的,PCB

上也會(huì)有寄生電容,所以會(huì)有一個(gè)限制。實(shí)際設(shè)計(jì)中經(jīng)驗(yàn)值大概是不超過(guò) 8 個(gè)器件。

總線之所以規(guī)定電容大小是因?yàn)椋琁2C 使用的 GPIO 為開漏結(jié)構(gòu),開漏結(jié)構(gòu)無(wú)法輸出高電平,要求外部有上拉電阻拉高。電阻和總線電容產(chǎn)生了一個(gè) RC延時(shí)效應(yīng),電容越大信號(hào)的邊沿就越緩,有可能帶來(lái)信號(hào)質(zhì)量風(fēng)險(xiǎn)。

傳輸速度越快,信號(hào)的窗口就越小,上升沿下降沿時(shí)間要求更短更陡峭,所以 RC 乘積必須更小。

I2C 架構(gòu)

我們知道 I2C 有不同的速度模式,標(biāo)準(zhǔn)(100KHz)、快速(400KHz)、快速plus(1MHz)、高速(3.4MHz)。

Vdd 可以采用 5V、3.3V、1.8V 等,電源電壓不同,上拉電阻阻值也不同。

一般總線上認(rèn)為,低于 0.3Vdd 為低電平,高于 0.7Vdd 為高電平。

-

設(shè)備

+關(guān)注

關(guān)注

2文章

4657瀏覽量

71605 -

總線

+關(guān)注

關(guān)注

10文章

2958瀏覽量

89535 -

I2C

+關(guān)注

關(guān)注

28文章

1538瀏覽量

127415 -

架構(gòu)

+關(guān)注

關(guān)注

1文章

528瀏覽量

25925

發(fā)布評(píng)論請(qǐng)先 登錄

i2c總線ppt(I2C總線器件應(yīng)用)

i2c總線的特點(diǎn)

I2C總線規(guī)范與I2C器件C51讀寫程序

I2C總線詳解

基于CPLD的I2C總線接口設(shè)計(jì)

Linux的I2C驅(qū)動(dòng)架構(gòu)

I2C總線的基本通信總結(jié)

硬件I2C與模擬I2C

I2C總線能掛多少設(shè)備 I2C架構(gòu)

I2C總線能掛多少設(shè)備 I2C架構(gòu)

評(píng)論