為何測出的相位噪聲性能低于ADIsimPLL仿真預(yù)期值?

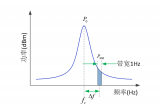

相位鎖定環(huán)(PLL)是一種重要的電路,可用于在不同領(lǐng)域中應(yīng)用,如無線通信、數(shù)據(jù)傳輸、數(shù)字信號處理等。PLL將信號同步到參考時鐘的頻率和相位,以保證信號的穩(wěn)定性和準(zhǔn)確性。其中一個重要的指標(biāo)是相位噪聲,它表征PLL鎖定的相位偏移情況。在PLL的設(shè)計和應(yīng)用過程中,相位噪聲性能是一個非常關(guān)鍵的指標(biāo),因為它直接影響系統(tǒng)的性能和精度。本文將就為何測出的相位噪聲性能低于ADIsimPLL仿真預(yù)期值這個問題進(jìn)行詳盡、詳實、細(xì)致的探討。

1. 頻率分辨率的影響

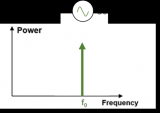

首先從頻率分辨率的角度來看,ADIsimPLL仿真預(yù)期值與實際測量的相位噪聲值之間可能有偏差。理論上,頻率分辨率越高,測量的相位噪聲值就越精確,但是實際上,由于實驗裝置的限制,無法達(dá)到理論上的頻率分辨率。因此,實際測量得到的相位噪聲值可能比仿真預(yù)期值要大。此時可以通過增加測量時的頻率分辨率或者使用更高精度的測量設(shè)備來提高測量精度,從而得到更準(zhǔn)確的測量結(jié)果。

2. 仿真模型的不足

其次從仿真模型的角度來看,ADIsimPLL仿真預(yù)期值可能存在一些模型上的限制,這些限制可能導(dǎo)致仿真結(jié)果與實際的測量結(jié)果存在一定偏差。例如,在仿真模型中,可能忽略了一些器件的非線性和噪聲,這些因素在實際電路中會對相位噪聲產(chǎn)生影響。因此,需要對仿真模型進(jìn)行完善和驗證,并根據(jù)實際電路的特點進(jìn)行模型參數(shù)的調(diào)整,以減小仿真與測量之間的差異。

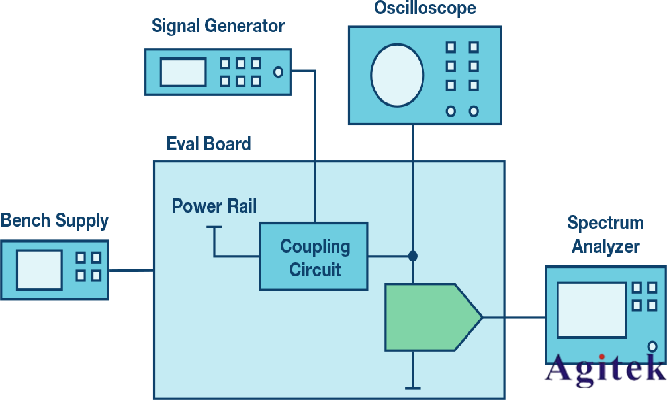

3. PCB設(shè)計的影響

還有就是PCB設(shè)計方面的影響。 PCB的設(shè)計質(zhì)量直接影響PLL電路的性能。 PCB設(shè)計不良會導(dǎo)致電路在高頻下產(chǎn)生反射、串?dāng)_等現(xiàn)象,影響電路的干擾、抗干擾能力和相位噪聲性能等。因此,在PLL電路的設(shè)計和調(diào)試過程中,需要對 PCB進(jìn)行全面考慮和優(yōu)化。

4. 環(huán)境因素的影響

最后從環(huán)境因素的角度來看,測試結(jié)果可能受到環(huán)境因素的影響。例如溫度、濕度等因素會影響電器元件的性能和電路中噪聲的產(chǎn)生。因此,需要在實驗環(huán)境穩(wěn)定的情況下進(jìn)行測量,并對測量結(jié)果進(jìn)行修正和分析,以確定真實的相位噪聲性能值。

綜上所述,為何測出的相位噪聲性能低于ADIsimPLL仿真預(yù)期值,可能有多種原因。在實際應(yīng)用中,需要結(jié)合具體情況進(jìn)行綜合考慮和分析,以準(zhǔn)確評估PLL電路的相位噪聲性能,確保系統(tǒng)的穩(wěn)定、精確和可靠。

-

無線通信

+關(guān)注

關(guān)注

58文章

4734瀏覽量

145054 -

PCB設(shè)計

+關(guān)注

關(guān)注

396文章

4793瀏覽量

89894 -

相位噪聲

+關(guān)注

關(guān)注

2文章

186瀏覽量

23269

發(fā)布評論請先 登錄

揭秘相位噪聲,提升測試效率

普源DSG3000系列如何實現(xiàn)低相位噪聲

信號發(fā)生器在相位噪聲測量中的應(yīng)用

是德示波器相位噪聲測試

請問如何根據(jù)相位噪聲求取相位噪聲的功率譜密度?

相位噪聲分析儀的技術(shù)原理和應(yīng)用

是德E5080B矢量網(wǎng)絡(luò)分析儀的相位噪聲分析

LMX2582開環(huán)相位噪聲和閉環(huán)相位噪聲的區(qū)別是什么?

數(shù)字振蕩器的相位噪聲是多少

頻譜儀怎么測量相位噪聲

時鐘抖動與相位噪聲的關(guān)系

鎖相環(huán)相位噪聲的影響因素

如何快速準(zhǔn)確地測量相位噪聲

為何測出的相位噪聲性能低于ADIsimPLL仿真預(yù)期值?

為何測出的相位噪聲性能低于ADIsimPLL仿真預(yù)期值?

評論