1 簡介

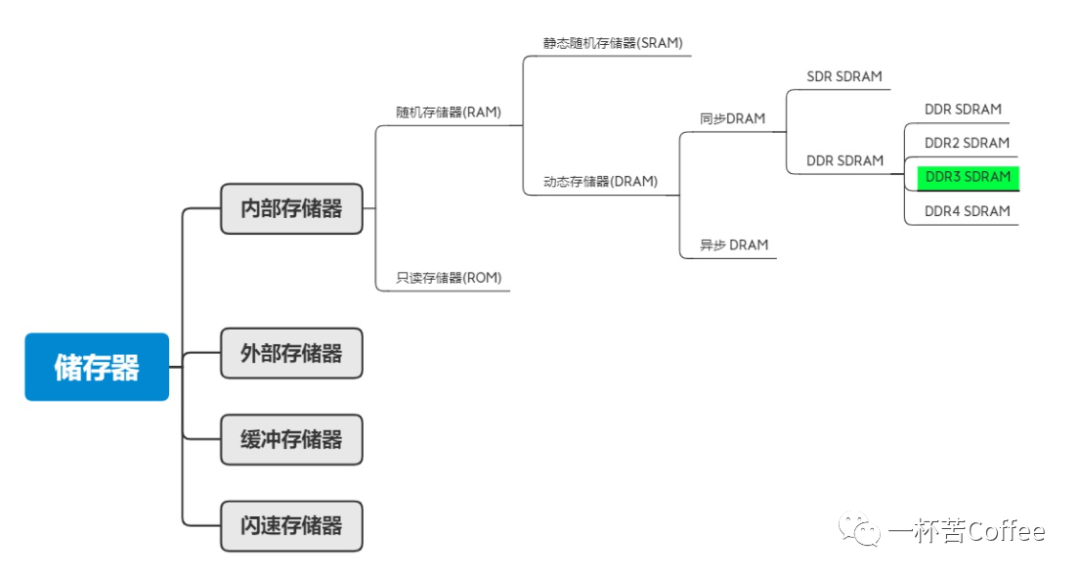

存儲(chǔ)器體可以分為RAM和ROM,其主要的區(qū)別如下:

- RAM存儲(chǔ)器: 存儲(chǔ)器掉電數(shù)據(jù)丟失,重新上電后數(shù)據(jù)無法回復(fù)。

- ROM存儲(chǔ)器: 存儲(chǔ)掉電數(shù)據(jù)不丟失,重新上電后能依然存在。

電路設(shè)計(jì)中常見的DDR屬于SDRAM,中文名稱是同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器。其中同步和動(dòng)態(tài)的意義分別如下:

- 動(dòng)態(tài)存儲(chǔ)器(Dynamic RAM,DRAM) :存儲(chǔ)器需每隔一段時(shí)間,要刷新沖一次電,否則會(huì)丟失內(nèi)部的數(shù)據(jù)。

- 靜態(tài)存儲(chǔ)器(Static RAM,SRAM) :不需要刷新電路,內(nèi)部數(shù)據(jù)不會(huì)丟失。

- 同步(Synchronous) :工作需要同步時(shí)鐘,它是內(nèi)部數(shù)據(jù)和指令的發(fā)送與接收的基準(zhǔn)。

- 隨機(jī)存儲(chǔ)器 :數(shù)據(jù)不是線性存儲(chǔ),而是通過指定地址來進(jìn)行數(shù)據(jù)的讀寫。

2 DDR的發(fā)展歷程

- 版本迭代

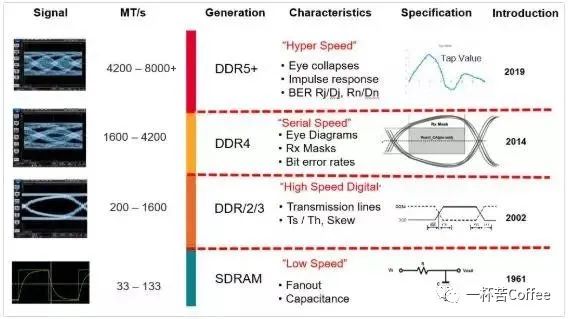

DDR的發(fā)展經(jīng)歷了SDRAM、DDR2、DDR3、DDR4、DDR5五個(gè)階段,隨著時(shí)間的推移,存儲(chǔ)的速率越來越高,核電越來越低。

- 最高傳輸速率

目前DDR5所能到達(dá)的最高的速率為6400T/s。

| 序號(hào) | 版本 | 核電壓 | 最高速率 |

|---|---|---|---|

| 1 | SDRAM | 2.5V/3.3V | |

| 2 | DDR2 | 1.8V | |

| 3 | DDR3 | 1.5V | 1600MT/s |

| 4 | DDR4 | 1.2V | 3200MT/s |

| 5 | DDR5 | 1.1V | 6400MT/s |

這里順帶說一下T/S和bps的換算關(guān)系:

- T/S的含義

T/s表示每秒****傳輸次數(shù)(Transfer per second) ,有效帶寬要結(jié)合傳輸協(xié)議來計(jì)算。

- bps的含義

bps表示每秒傳輸二級(jí)制位數(shù)(bit per second)。

案例 :PCI-e2.0 協(xié)議支持 5.0 GT/s, 即每一條Lane 上支持每秒鐘內(nèi)傳輸 5G次,因?yàn)镻CIe 2.0 的物理層協(xié)議中使用的是 8b/10b的編碼機(jī)制,即每傳輸8個(gè)bit,需要發(fā)送10個(gè)bit;這多出的2個(gè)bit并不是對(duì)上層有意義的信息。PCIe 2.0協(xié)議的每一條Lane支持 5 * 8/10=4Gbps的速率。 以一個(gè)PCIe 2.0 x8的通道為例,x8的可用帶寬為 4 * 8=32Gbps。(后面PCIe文章還會(huì)更加詳細(xì)講解)

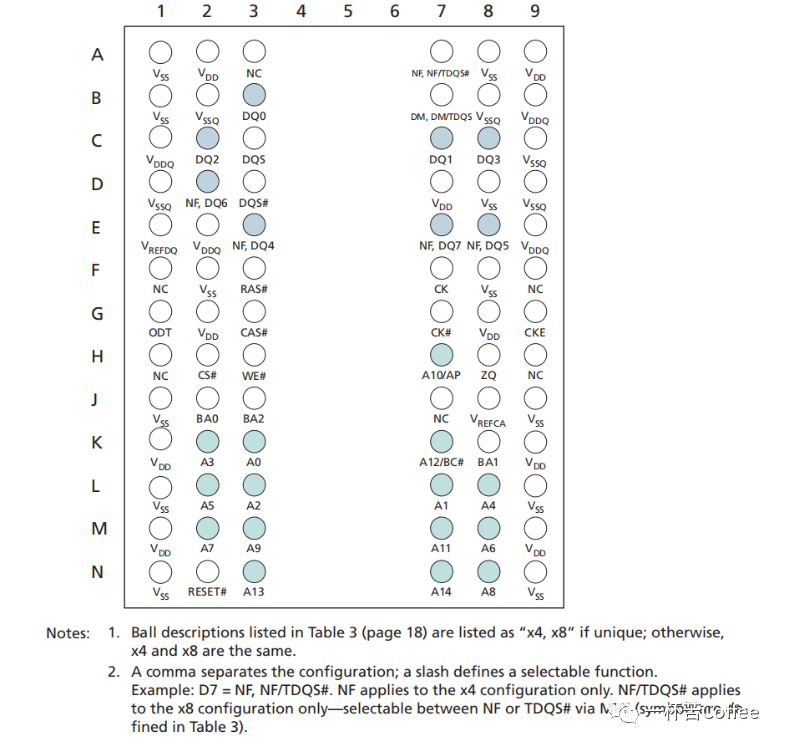

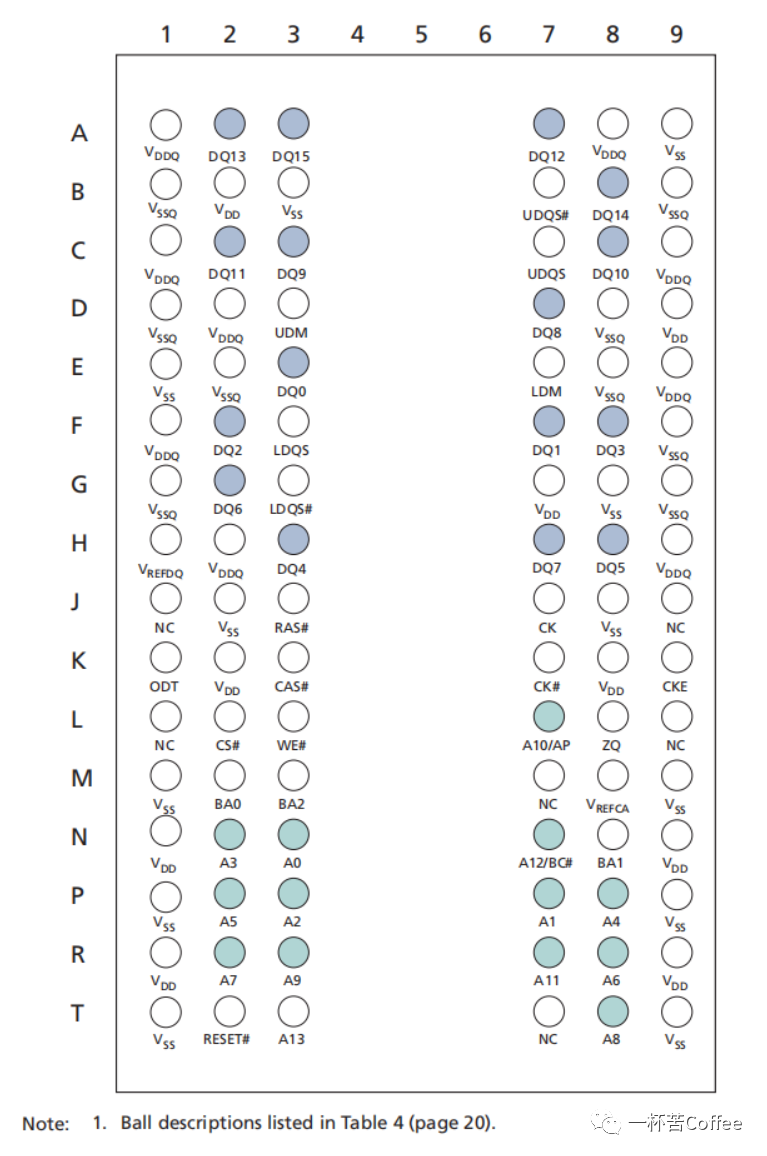

3 DDR的封裝

DDR3和DDR4的封裝主要有兩種:78-Ball FBGA – x4, x8 和96-Ball FBGA – x16。

- 78-Ball FBGA – x4, x8 (Top View)

這種封裝類型有78個(gè)PIN腳,僅支持4數(shù)據(jù)位寬和8數(shù)據(jù)帶寬。

- 96-Ball FBGA – x16 (Top View)

這種封裝類型有96個(gè)PIN腳,僅支持最高支持16數(shù)據(jù)帶寬。

4 DDR的容量計(jì)算

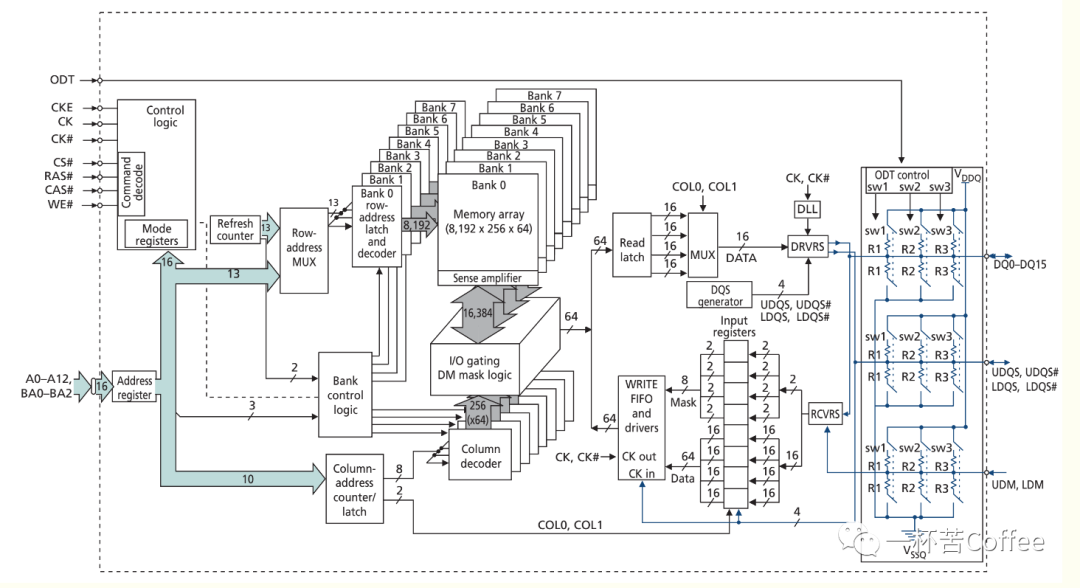

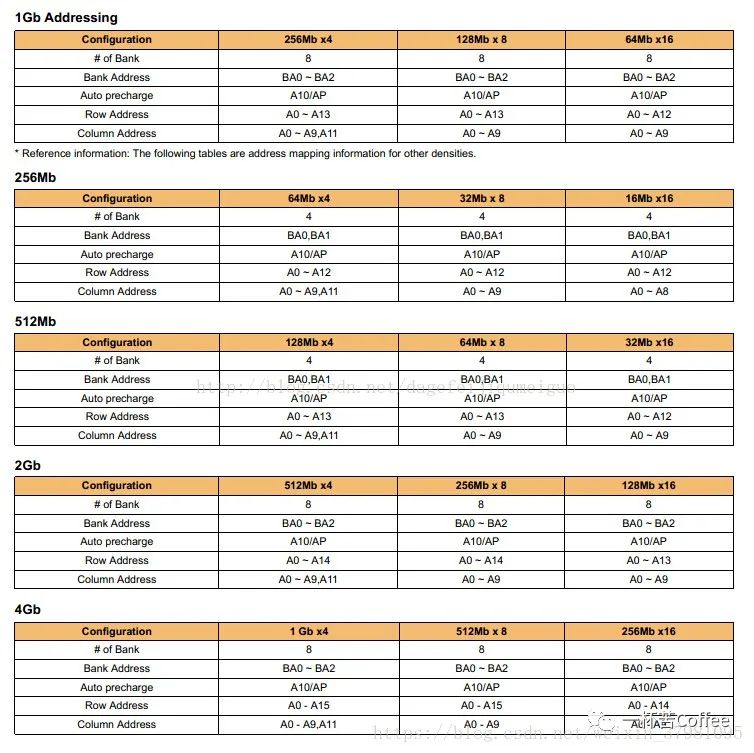

由圖可以歸納出:

- bank有8個(gè),對(duì)應(yīng)BA[2:0];

- 行地址有15bit,列地址有10bit(其中低3bit不會(huì)用于列尋址);

- 內(nèi)存顆粒的容量 = 2^15 * 2^10 * 8*16bit=4096Mbit;

- 根據(jù)DDR數(shù)據(jù)信號(hào)線位寬,描述上圖產(chǎn)品的規(guī)格,即256 * 16bit。

說明:15為行地址數(shù)目;7為列地址數(shù)目;8為Bank數(shù)目;16為數(shù)據(jù)位寬。

以下是案例:

5 DDR的基本原理

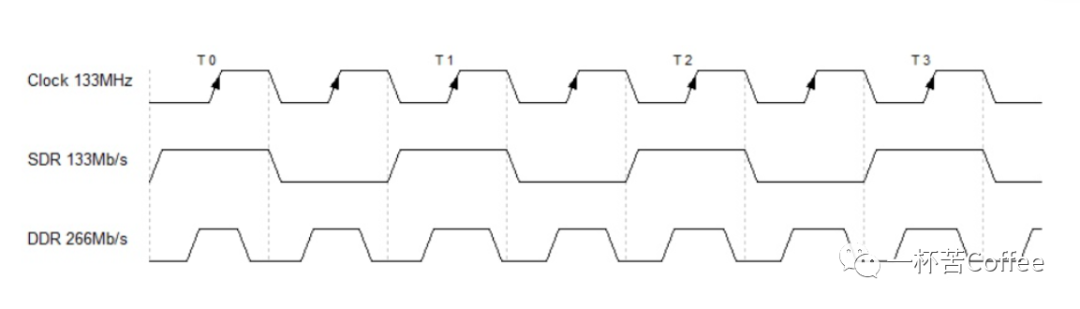

DDR里面主要使用了Double Data Rate 和 Prefetch兩項(xiàng)技術(shù)。實(shí)際上,無論是SDR還是DDR3,內(nèi)存芯片內(nèi)部的核心時(shí)鐘基本上是保持一致的,都是 100MHz 到 200MHz(某些廠商生產(chǎn)的超頻內(nèi)存除外)。DDR即 Double Data Rate 技術(shù)使數(shù)據(jù)傳輸速度較 SDR 提升了一倍。如下圖所示,SDR 僅在時(shí)鐘的上升沿傳輸數(shù)據(jù),而 DDR 在時(shí)鐘信號(hào)上、下沿同時(shí)傳輸數(shù)據(jù)。例如同為133MHz 時(shí)鐘,DDR卻可以達(dá)到266Mb/s的傳輸速度。

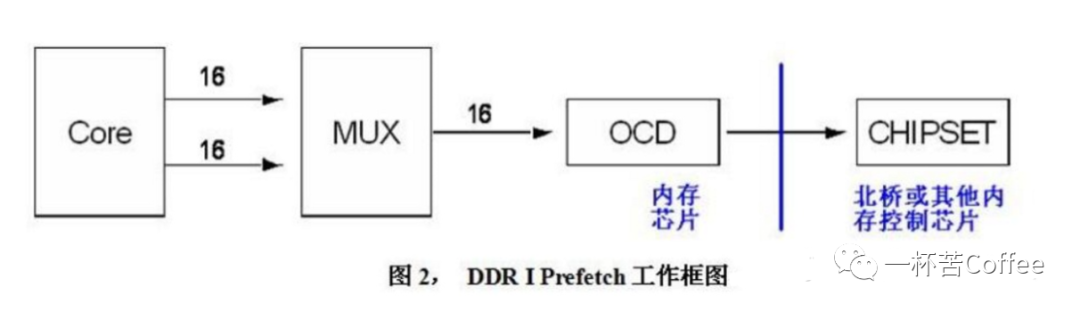

芯片內(nèi)部數(shù)據(jù)數(shù)據(jù)傳輸速度的提升則是通過Prefetch 技術(shù)實(shí)現(xiàn)的。 所謂 Prefetch 簡單的說就是在一個(gè)內(nèi)核時(shí)鐘周期同時(shí)尋址多個(gè)存儲(chǔ)單元并將這些數(shù)據(jù)以并行的方式統(tǒng)一傳輸?shù)絀O Buffer中,之后以更高的外傳速度將IO Buffer 中的數(shù)據(jù)傳輸出去 。這個(gè)更高的速度在DDR上就是通過Double Data Rate 實(shí)現(xiàn)的,也正因?yàn)槿绱耍珼DR外部 Clock 管腳的頻率與芯片內(nèi)部的核心頻率是保持一致的。如下圖所示為 DDR的Prefetch 過程中,在16位的內(nèi)存芯片中一次將2 個(gè)16bit數(shù)據(jù)從內(nèi)核傳輸?shù)酵獠縈UX單元,之后分別在Clock信號(hào)的上、下沿分兩次將這 2 x 16bit 數(shù)據(jù)傳輸給北橋或其他內(nèi)存控制器,整個(gè)過程經(jīng)歷的時(shí)間恰好為一個(gè)內(nèi)核時(shí)鐘周期。

發(fā)展到 DDR2,芯片內(nèi)核每次Prefetch 4倍的數(shù)據(jù)至IO Buffer中,為了進(jìn)一步提高外傳速度,芯片的內(nèi)核時(shí)鐘與外部接口時(shí)鐘(即我們平時(shí)接觸到的Clock 管腳時(shí)鐘)不再是同一時(shí)鐘,外 Clock時(shí)鐘頻率變?yōu)閮?nèi)核時(shí)鐘的2倍。同理, DDR3 每次Prefetch 8倍的數(shù)據(jù),其芯片Clock頻率為內(nèi)核頻率的4倍, 即 JEDEC標(biāo)準(zhǔn)(JESD79-3)規(guī)定的400MHz至800MHz,再加上在 Clock 信號(hào)上、下跳變沿同時(shí)傳輸數(shù)據(jù),DDR3的數(shù)據(jù)傳輸速率便達(dá)到了800MT/s到1600MT/s。具體到內(nèi)存條速度,我們以PC3-12800為例,其采用的DDR3-1600芯片核心頻率為 200MHz,經(jīng)過Prefetch后Clock信號(hào)頻率到達(dá) 800MHz,再經(jīng)過Double Data Rate 后芯片數(shù)據(jù)傳輸速率為1600 MT/s,內(nèi)存條每次傳輸64 bits或者說8 bytes數(shù)據(jù),1600*8 便得到12800MB/s的峰值比特率。

6 引腳描述

今天主要簡單介紹一些關(guān)鍵信號(hào),后續(xù)會(huì)詳細(xì)說明這些信號(hào)在設(shè)計(jì)中應(yīng)該注意的事項(xiàng) 。

| 信號(hào)名 | 方向 | 功能描述 |

|---|---|---|

| CK_t,CK_c | Input | 差分時(shí)鐘輸入。所有的地址、控制信號(hào)都是通過CK_t的上升沿與CK_c的下降沿進(jìn)行采樣的 |

| CKE | Input | 時(shí)鐘使能:CKE為高電平時(shí),啟動(dòng)內(nèi)部時(shí)鐘信號(hào)、設(shè)備輸入緩沖以及輸出驅(qū)動(dòng)單元。CKE低電平時(shí)則關(guān)閉上述單元。當(dāng)CKE為低電平時(shí),可使設(shè)備進(jìn)入PRECHARGE POWER DOWN、SELF-REFRESH以及ACTIVE POWER DOWN模式。CKE與SELF REFRESH退出命令是同步的。在上電以及初始化序列過程中,VREFCA與VREF將變得穩(wěn)定,并且在后續(xù)所有的操作過程中都要保持穩(wěn)定,包括SELF REFRESH過程中。CKE必須在讀寫操作中保持穩(wěn)定的高電平。在POWER DOWN過程中,除CK_t,CK_c,ODT以及CKE以外的所有輸入緩沖都是關(guān)閉的。在SELF REFRESH過程中,除CKE以外的所有輸入緩沖都是關(guān)閉的。在正時(shí)鐘上升邊沿采樣。 |

| CS_n | Input | 片選信號(hào):當(dāng)CS_n鎖存為高電平時(shí),所有的命令都被忽略。在正時(shí)鐘上升邊沿采樣。 |

| CA_n | Input | 命令/地址輸入信號(hào)。可作為地址線使用,也可作為命令代碼使用,是命令代碼的一部分。 |

| ODT | Input | On-Die Termination,片上終端電阻:ODT信號(hào)可使能DDR SDRAM內(nèi)部的RTT_NOM終端電阻。該設(shè)計(jì)通過允許DRAM控制器獨(dú)立地打開/關(guān)閉任一或所有DRAM設(shè)備的終端電阻來改善存儲(chǔ)器通道的信號(hào)完整性。DRAM通過ODT控制引腳為每個(gè)DQ,DQS_t及DQS_c和DM開啟/關(guān)閉終端電阻。與其他輸入命令不同,ODT引腳直接控制ODT動(dòng)作,不對(duì)其進(jìn)行時(shí)鐘采樣。在自刷新模式下不支持ODT。可以選擇在CKE掉電期間通過模式寄存器啟用ODT操作。請(qǐng)注意,如果在掉電模式下啟用ODT,則在掉電期間可能無法關(guān)閉VDDQ(I/O供電),同時(shí)DRAM也會(huì)在讀操作期間無法關(guān)閉。 |

| DM_n | Input | 輸入數(shù)據(jù)掩碼:DM_n信號(hào)是作為寫數(shù)據(jù)的掩碼信號(hào),當(dāng)DM_n信號(hào)為低電平時(shí),寫命令的輸入數(shù)據(jù)對(duì)應(yīng)的位將被丟棄。DM_n在DQS的兩個(gè)條邊沿都采樣。 |

| DQ | InputOutput | 數(shù)據(jù)輸入、輸出:雙向數(shù)據(jù)總線。若模式寄存器中使能了CRC功能,那么在數(shù)據(jù)burst結(jié)束時(shí)就會(huì)附加一段CRC碼。 |

| DQS_t,DQS_c | InputOutput | 差分?jǐn)?shù)據(jù)選通信號(hào):差分信號(hào)對(duì),作輸入時(shí)與寫數(shù)據(jù)同時(shí)有效,作輸出時(shí)與讀數(shù)據(jù)同時(shí)有效。讀數(shù)據(jù)時(shí)與邊沿對(duì)齊,但是跳變沿位于寫數(shù)據(jù)的中心。DDR4 SDRAM僅支持選通信號(hào)為差分信號(hào),不支持單根信號(hào)的數(shù)據(jù)選通信號(hào)。 |

| NC | N.A | 無電氣連接。 |

| VDDQ | Supply | I/O供電:1.2V +/- 0.06V |

| VSSQ | Supply | GND |

| VDD | Supply | Core供電:1.2V +/- 0.06V |

| VDDCA | Supply | CA供電 |

| VSSCA | Supply | GND |

| VSS | Supply | GND |

| VPP | Supply | DRAM激活供電:2.5V(最小2.375V,最大2.75V) |

| VREF | Supply | 參考電壓 |

| ZQ | Supply | Drive Strength Caliation校準(zhǔn)參考電阻 |

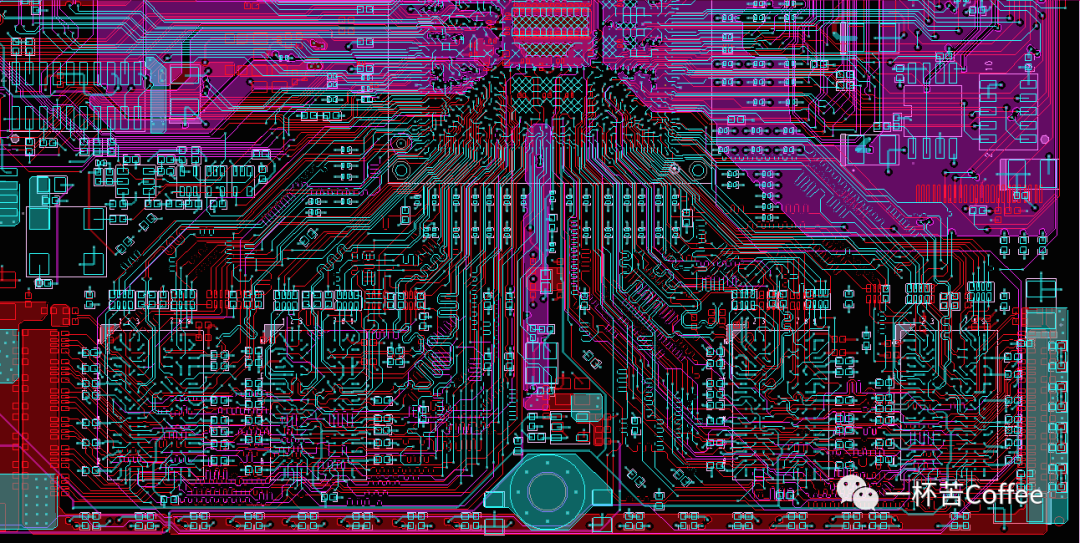

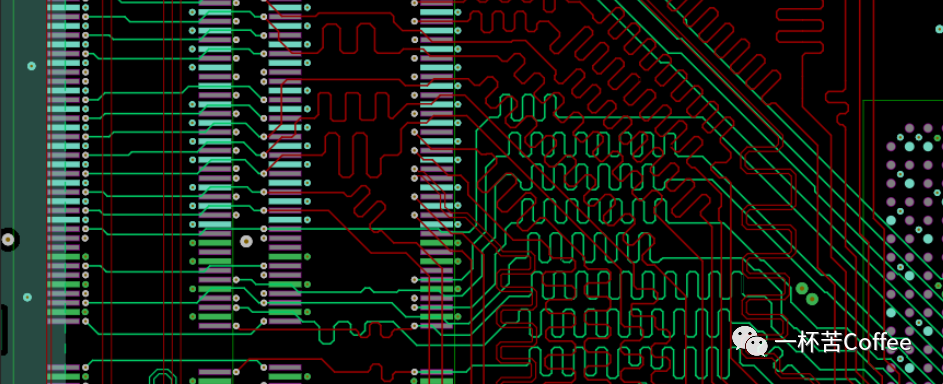

7 硬件電路實(shí)戰(zhàn)

今天主要是放一些參考電路,下一篇文章會(huì)詳細(xì)講解DDR設(shè)計(jì)的整個(gè)過程,包括DDR的級(jí)聯(lián)以及Layout中應(yīng)該注意的事項(xiàng)。

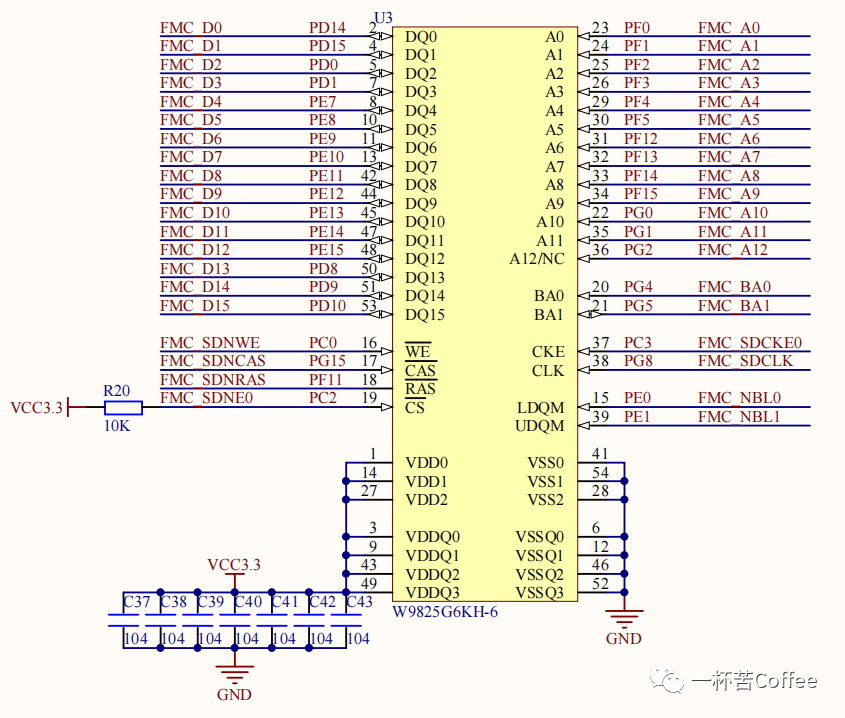

- SDRAM電路設(shè)計(jì)案例

SDRAM廣泛應(yīng)用于LCD屏幕中,通常搭配NAND Flash或者NOR Flash使用。

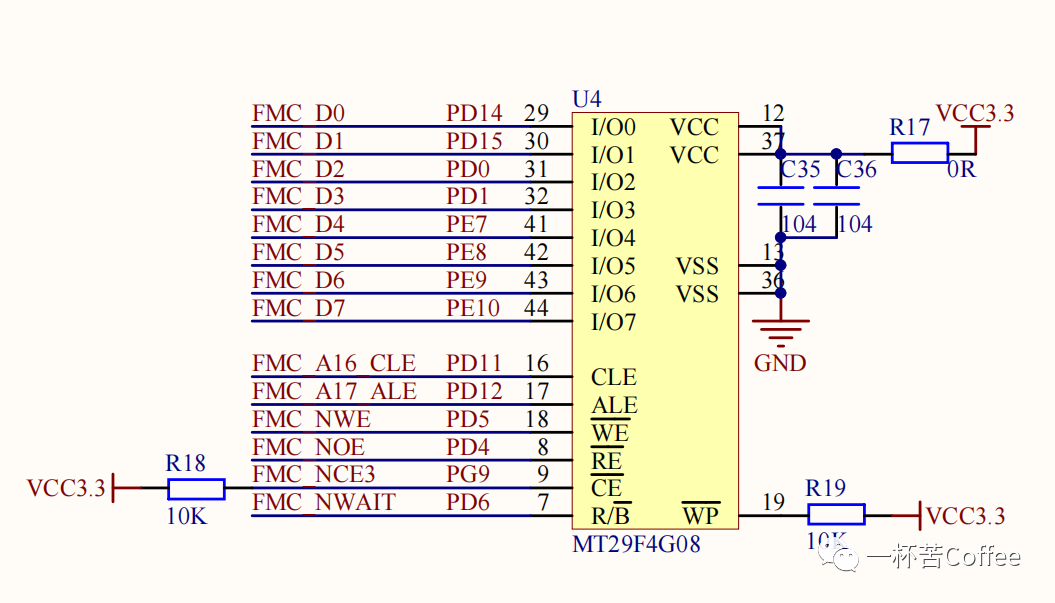

NAND Flash的存儲(chǔ)電路見下圖:

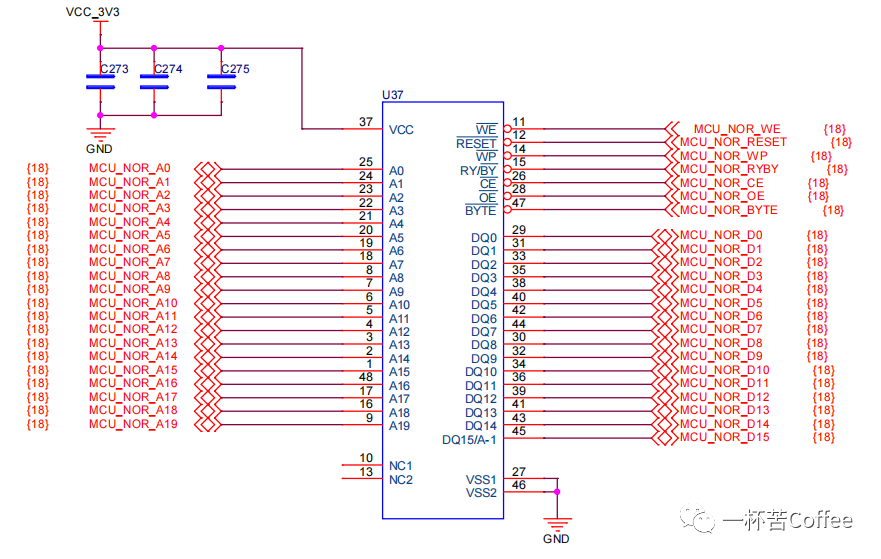

NOR Flash的電路設(shè)計(jì)見下:

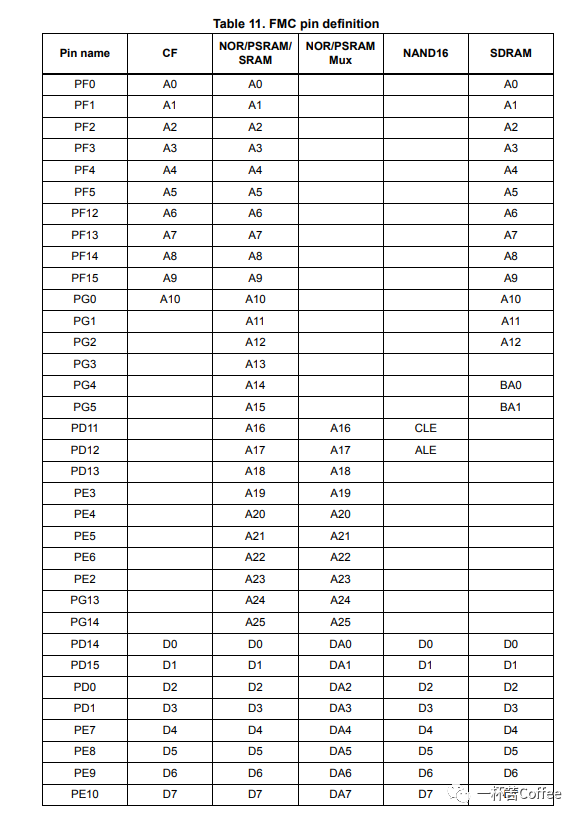

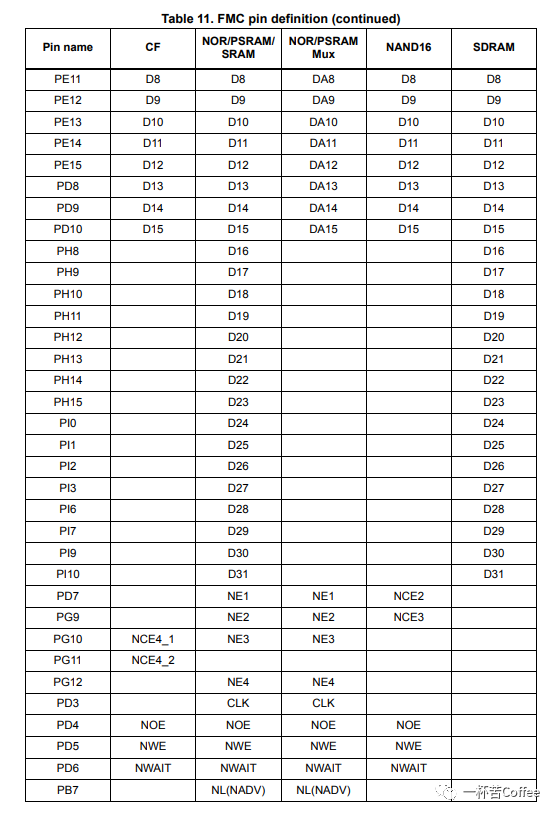

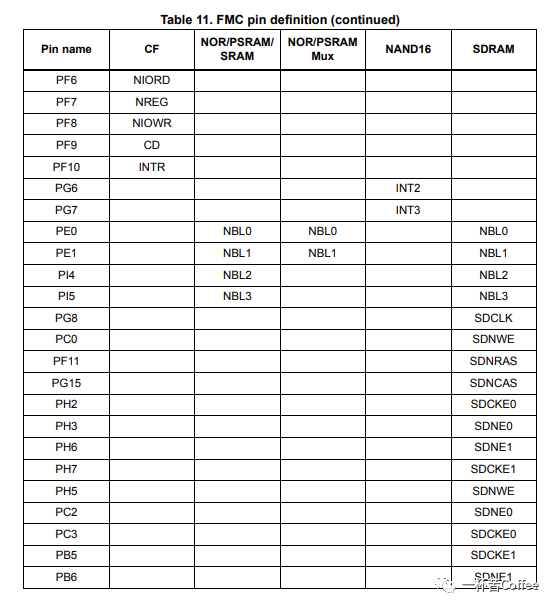

NOR Flash和SRAM的數(shù)據(jù)線和地址線通常是復(fù)用的,具體需要見手冊(cè),以下截取STM32手冊(cè)部分內(nèi)容:

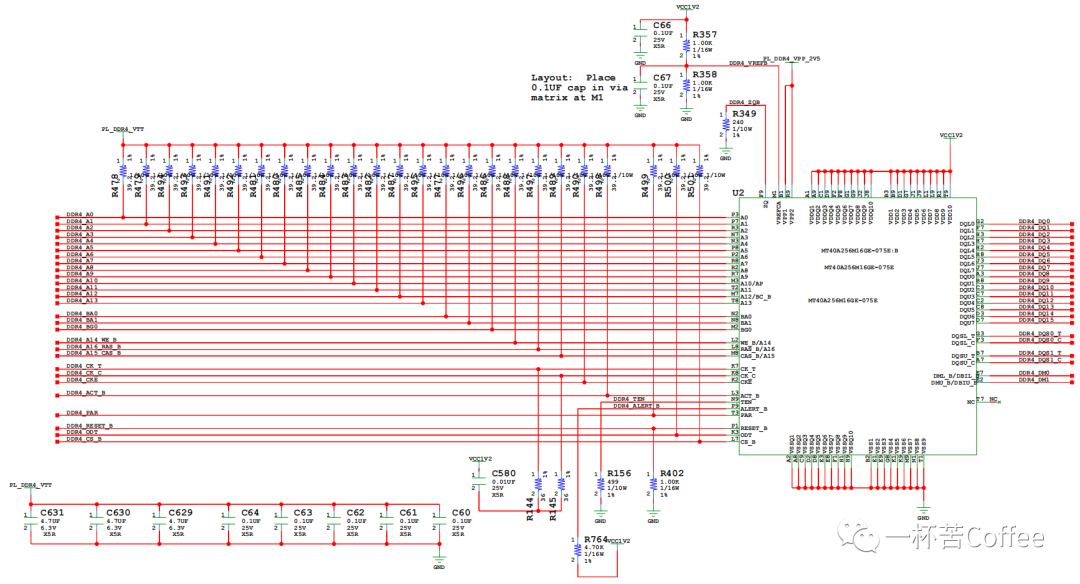

- DDR4電路設(shè)計(jì)案例

DDR4應(yīng)用最為廣泛,原因有兩個(gè):

- DDR4的存儲(chǔ)速率能滿足大部分工程師的需求;

- DDR5的走線對(duì)設(shè)計(jì)者的要求比較高。

NOR Flash/NAND Flash和SRAM的數(shù)據(jù)線和地址線通常是復(fù)用的

-

SDRAM

+關(guān)注

關(guān)注

7文章

442瀏覽量

56240 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7644瀏覽量

167088 -

電路設(shè)計(jì)

+關(guān)注

關(guān)注

6705文章

2536瀏覽量

214411 -

DDR

+關(guān)注

關(guān)注

11文章

732瀏覽量

66696 -

DDR2

+關(guān)注

關(guān)注

1文章

104瀏覽量

41959

發(fā)布評(píng)論請(qǐng)先 登錄

怎么成為硬件電路設(shè)計(jì)高手?

硬件電路設(shè)計(jì)之接地問題

硬件電路設(shè)計(jì)之晶體與晶振電路設(shè)計(jì)

高速電路設(shè)計(jì)

硬件電路設(shè)計(jì)流程系列

硬件電路設(shè)計(jì)的思路分享

硬件電路設(shè)計(jì)流程--原理圖設(shè)計(jì)

硬件電路設(shè)計(jì)之“磁珠”的應(yīng)用資料下載

硬件電路設(shè)計(jì)的基本流程、作用和注意事項(xiàng)

硬件電路設(shè)計(jì)之DDR電路設(shè)計(jì)(1)

硬件電路設(shè)計(jì)之DDR電路設(shè)計(jì)(1)

評(píng)論