在進(jìn)行數(shù)字電路后仿真時,經(jīng)常會遇到很多時序為例,通常這些違例都是由網(wǎng)表中大量的時序檢查報出的。這些常見的時序檢查系統(tǒng)任務(wù)如下表所示:

| 時序檢查系統(tǒng)任務(wù) | 說明 |

|

$setuphold |

檢查建立時間和保持時間,當(dāng)setup違例時,出現(xiàn)此信息 |

|

$setuphold |

檢查建立時間和保持時間,當(dāng)hold違例時,出現(xiàn)此信息 |

| $setup | 檢查建立時間 |

| $hold | 檢查保持時間 |

| $recovery | 檢查恢復(fù)時間(以復(fù)位信號為例,可以理解為rst必須在時鐘沿之前的有效的最小時間),一般用于復(fù)位、置位等 |

| $removal | 檢查撤銷時間(以復(fù)位信號為例,可以理解為rst必須在時鐘沿之后的有效的最小時間),一般用于復(fù)位、置位等 |

| $recrem | 檢查恢復(fù)和撤銷時間,一般常用于復(fù)位、置位等 |

| $period | 檢查周期信號的最小周期,一般常用于時鐘 |

| $skew | 檢查兩個信號之間的最大時間差 |

| $width | 檢查脈沖的最小寬度 |

因為在仿真的過程中,有些報出的違例我們是不關(guān)心的,這些信息的大量出現(xiàn)可能會淹沒我們真正需要觀測的信息,為此需要在仿真時講這些冗余的信息屏蔽掉。

針對大家經(jīng)常使用的NCSIM、VCS和ModelSim(QuestaSim),下文將說明如何在這兩種EDA工具中屏蔽冗余的違例信息。

1 NCSIM

屏蔽使用的命令格式:

% irun-tfile myfile.tfile[other_options] source_files

上述命令中myfile.tfile中包含屏蔽信息,其中主要內(nèi)容如下表:

| 參數(shù) | 說明 |

|

-iopath +iopath |

不使能路徑延遲 使能路徑延遲 |

|

-prim +prim |

不使能指定的instance中原語的延遲 使能指定的instance中原語的延遲 |

|

-port +port |

刪除指定的instance的port延遲 使能指定的instance的port延遲 |

|

[SystemTimingTask] -tcheck [SystemTimingTask] +tcheck |

屏蔽掉不關(guān)心的違例 |

【示例】*.tfile中內(nèi)容格式

PATH top.foo -tcheck // 屏蔽所有關(guān)于foo的時序檢查

PATH top.foo $setup $hold -tcheck // 屏蔽所有關(guān)于foo的setup和hold時序檢查

PATH :SOC.lcsoc.syn_reg $setup -tcheck // 屏蔽:SOC.lcsoc.syn_reg的setup檢查

注意:如果要屏蔽其他檢查,只需將示例中的$setup或者$hold換成SystemTimingTask中的任何一個即可。

2 VCS

命令格式如下:

tcheck

tcheck

上述命令使用時需要注意以下幾點:

1>在simv的option中,即 % ./simv -ucli run.tcl,其中run.tcl中增加需要屏蔽的信號,將tcheck中的內(nèi)容增加的run.tcl中;

2>該命令僅對Verilog/SystemVerilog使用;

3>該命令使用時,待檢測的源代碼必須包括時序檢查系統(tǒng)任務(wù),否則將會產(chǎn)生warning信息;

上述命令格式中使用的相關(guān)參數(shù)的說明如下表所示。

| 參數(shù) | 說明 |

| instance | port | 要被屏蔽的時序檢查的實例或者端口的全路徑名稱 |

| tcheck_type | 指定需要進(jìn)行屏蔽的時序檢查類型:HOLD|SETUP|SETUPHOLD|WIDTH|RECOVERY|REMOVAL|RECREM|PERIOD|SKEW|ALL |

| -disable | -enable | 使能或不使能相關(guān)時序檢查,如果要求屏蔽其中SETUP,則在tcheck_type指定SETUP后,需要在tcheck中使用-disable |

| -msg | -xgen |

A.指定的實例或者端口違例信息是否被顯示 B.指定的實例或者端口notifier信息是否被顯示 |

| -r | 指定是否遞歸式的對所有指定的instance及其以下層次所有的instance進(jìn)行時序檢查 |

【示例】(可以通過-ucli do.tcl直接添加到simv中)

tcheck {top_tb.C40010001} WIDTH -msg -disable

#對top_tb.C40010001不進(jìn)行WIDTH時序檢查,即屏蔽掉top_tb.C40010001的WIDTH檢查

tcheck {top_tb.C40010001} -query

#顯示對top_tb.C40010001的時序檢查信息

3 ModelSim(QuestaSim)

命令格式如下:

tcheck_set[-quiet]

上述命令格式中使用的相關(guān)參數(shù)的說明如下表所示。

| 參數(shù) | 說明 |

|

|

實例(模塊或者線網(wǎng))的全路徑名稱,該項是必須的 |

| -m | -n |

指定屏蔽操作的對象是模塊還是線網(wǎng),該項可選。 -m:此時命令中指定的instance是module(Verilog)或者entity(VHDL),此時的屏蔽操作將作用于指定的模塊的所有實例 -n:此時命令中指定的instance指向一個線網(wǎng),tcheck_set將應(yīng)用于所有連接該線網(wǎng)的實例 |

| -quiet |

用于指定配置信息不顯示于Transcript窗口,該參數(shù)的指定必須先于 |

| -r [-v] | 指定是否遞歸式的對所有指定的instance及其以下層次所有的instance進(jìn)行時序檢查,默認(rèn)情況下,遞歸過程中被改變的instance的信息不會輸出到Transcript,可以用-v將這些信息輸出至Transcript中,該項可選 |

| tcheck_type | 指定需要進(jìn)行屏蔽的時序檢查類型:HOLD|SETUP|SETUPHOLD|WIDTH|RECOVERY|REMOVAL|RECREM|PERIOD|SKEW|ALL |

|

|

使能或者禁止是否將指定的時序檢查違例信息和不定態(tài)產(chǎn)生的信息報出,該項可設(shè)置的值為“ON”和“OFF”,該項可選 |

|

|

控制指定時序檢查的違例信息和不定態(tài)信息,其中 |

【示例】

tcheck_set top_tb.u1.u2 “(WIDTH (negedge clk))”O(jiān)FF

#示例中,top_tb.u1.u2下的(WIDTH (negedge clk))檢查產(chǎn)生的所有信息都將被屏蔽掉。如果對于示例中時序檢查表達(dá)式的寫法不了解,可以使用“tcheck_statustop_tb.u1.u2”來查看top_tb.u1.u2下所有的時序檢查表達(dá)式,具體應(yīng)用如下所示:

% tcheck_status top_tb.u1.u2

% #0 (WIDTH (negedge clk)) MsgOn XOn

% #1 (WIDTH (posedge clk)) MsgOn XOn

% #2 (SETUP (negedge d)(posedge clk)) MsgOn XOFF

% #3 (HOLD (posedge clk)(negedge d)) MsgOn XOFF

最后在使用上述EDA工具時,因為不同的工具提供的路徑不同,在具體使用時,一定要使用對應(yīng)的工具獲得該工具可識別的路徑信息。

審核編輯:劉清

-

EDA工具

+關(guān)注

關(guān)注

4文章

273瀏覽量

32723 -

soc

+關(guān)注

關(guān)注

38文章

4362瀏覽量

222182 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1638瀏覽量

81756 -

VCS

+關(guān)注

關(guān)注

0文章

80瀏覽量

9879

原文標(biāo)題:NCSIM、VCS和QuestaSim(ModelSim)后仿真如何屏蔽違例

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

VCS仿真指南(第二版).pdf

ISE設(shè)計,questasim仿真時庫編譯的問題

nanosim和vcs混合仿真的過程是怎樣的?

VCS仿真卡住,為什么無法生成verdi波形文件呢?

基于linux系統(tǒng)的VCS使用及仿真說明

ModelSim和QuestaSim功能簡介及應(yīng)用

基于linux系統(tǒng)實現(xiàn)的vivado調(diào)用VCS仿真教程

基于FPGA的仿真如何工作

vcs學(xué)習(xí)筆記(常用選項/仿真流程/代碼覆蓋率/綜合后仿真/圖一樂技巧)

SpinalHDL運行VCS+Vivado相關(guān)仿真

淺談VCS的兩種仿真flow

使用Vivado調(diào)用questasim仿真報錯的原因及其解決辦法

如何在EDA工具中屏蔽冗余的違例信息

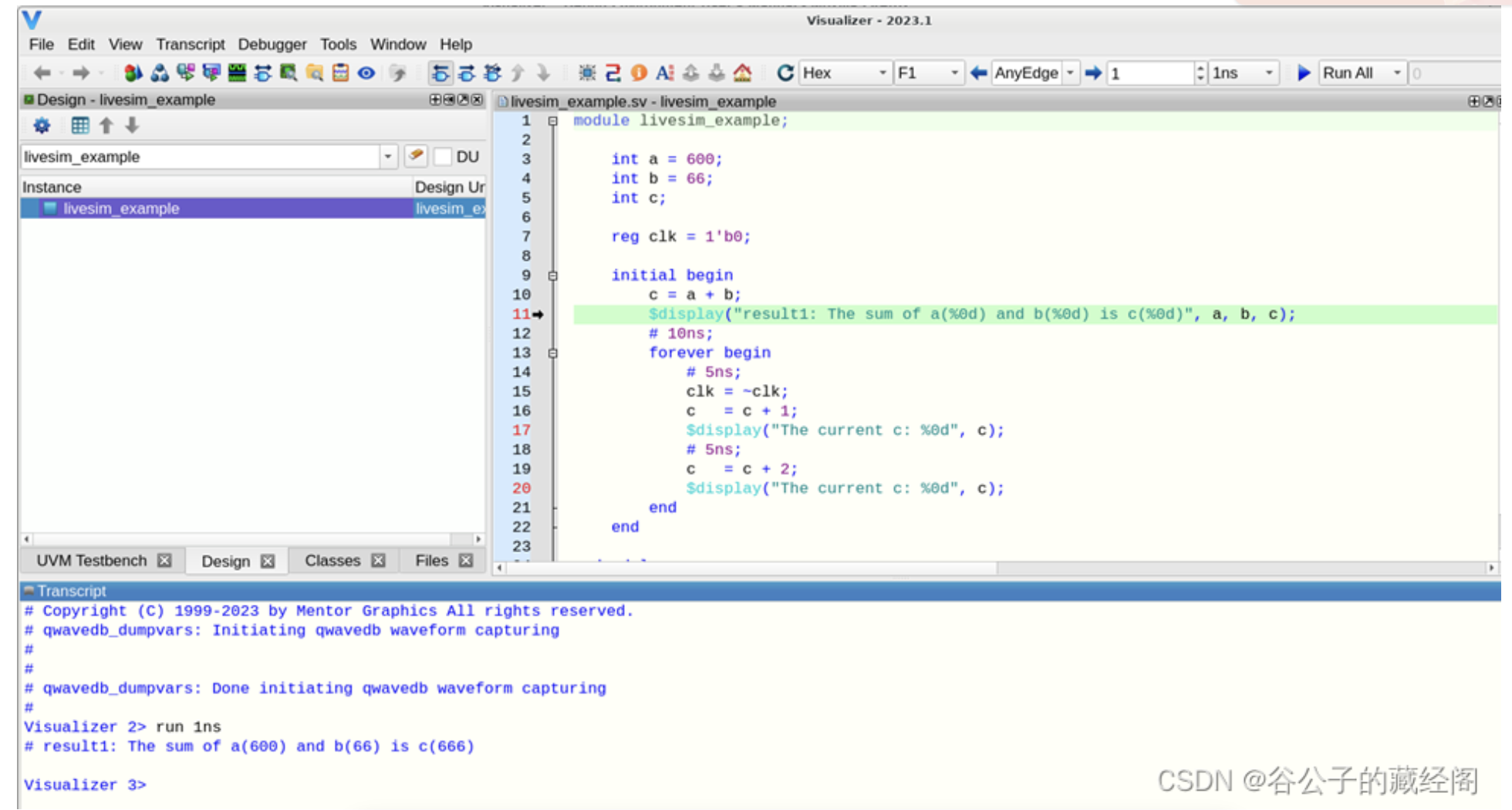

Questasim與Visualizer的livesim仿真如何啟動呢?

NCSIM、VCS和QuestaSim后仿真如何屏蔽冗余的違例信息呢?

NCSIM、VCS和QuestaSim后仿真如何屏蔽冗余的違例信息呢?

評論